Преобразователь перемещения в унитарный код

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством. С целью повышения разрешающей способности в преобразователь перемещения в унитарный код, содержащий генератор 1 импульсов, формирователь 2 опорного сигнала, фазовращатель 3, нуль-орган 4, фазовый дискриминатор 5, формирователь 7 компенсационного сигнала, введены блок 6 задержки временных интервалов, формирователь 8 импульсного грубого отсчета, формирователь 9 выходных кодов, формирователь 10 импульсов точного отсчета , триггеры 11 и 12. Перемещение преобразуют в фазовый сдвиг между фазным и опорным сигналом, в каждом периоде опорного Сигнала сравнивают по фазе фазный и компенсационный сигналы, разность фаз которых преобразуют в унитарный код грубого отсчета, сдвигают по фазе компенсационный сигнал до устранения рассогласования между ним и фазным сигналом , формируют дополнительные импульсы точного отсчета и суммируют их с унитарным кодом грубого отсчета. 9 ил. ел С

СОЮЗ СОВЕТСКИХ

СОЦИА.ЛИСТИЧF. СКИХ

РЕСПУБЛИК (s3)s Н 03 М 1/64

ГОСУДАРСТВЕ!-0ЮЕ ПАТЕНТНОЕ

ВЕДОМСТВО CCCP (ГОСПАТЕНТ СССР) ОГ1 И САН И Е И 3 О БР ЕТЕ Н ИЯ

}(ПАТЕНТУ (2 1) 4796276/24 (22) 27.02.90 (46) 23.01.93, Бюл, № 3 (71) Сибирский завод комплектного электропривода "Сибстанкоэлектропривод" (72) Н,В,Коголева, А.М.Колесников и

В,А. Цуканова (73) А.M, Колесников (56) Авторское свидетельство СССР

¹ 903928, кл, Н 03 M 1/64, 1981, Электротехническая промышленность.

Сер. Электропривод, 1983, вып, 3 (118), с. 11, рис. 1. (54) ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЯ

В УНИТАРНЫЙ КОД (57) Изобретение относится к автоматике и вычислительной технике и может быть использованв для связи аналоговых источников информации с цифровым вычислительным устройством. С целью повышения разрешающей способности в пре. Ж 1790802 АЗ образователь перемещения в унитарный код, содержащий генератор 1 импульсов, формирователь 2 опорного сигнала, фазовращатель 3, нуль-орган 4, фазовый дискриминатор 5, формирователь 7 компенсационного сигнала, введены блок 6 задержки временных интервалов, формирователь 8 импульсного грубого отсчета, формирователь 9 выходных кодов, формирователь 10 импульсов точного отсчета, триггеры 11 и 12. Перемещение преобразуют в фазовый сдвиг между фазным и опорным сигналом, в каждом периоде опорного Сигнала сравнивают по фазе фазный и компенсационный сигналы, разность фаз которых преобразуют в унитарный код грубого отсчета, сдвигают по фазе компенсационный сигнал до устранения рассогласования между ним и фазным сигналом, формируют дополнительные импульсы точного отсчета и суммируют их с унитарным кодом грубого отсчета, 9 ил.

1790802

Изобретение относится к области автоматики и вычислительной техники и может быть использовано Для сВязи аналогоВых источников информации с цифровым вычислительным устройством.

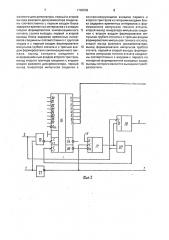

Целью изобретения является повышение разрешающей способности преобразователя перемещения в унитарный код, Структурная схема преобразователя представлена на фиг,1, структурная схема блока задержки Времейных интервалов — на фиг,2, структурная схема формирователя компенсационного сигнала — на фиГ,З, структурная схема формирователя импульсов грубого отсчета — на фиг,4, структурная схема формирователя выходных кодов — на фиг.5, структурная схема дифференцирующего элемента — на фиг,6, временная диаграмма

paGo гы устройства при поло)кительном и отрицательном направлении перемещения на фиг,7 и 8 соответственно, временная диаграмма работы блока задержки временных интервалов — на фиг,9.

Преобразователь перемещения в v i тарный код (фиг. 1) содержит генератор 1 импульсов, формирователь 2 опорного сигнала, фазовращатель 3, нуль-орган 4, фазовый дискриминатор 5, блок 6 задержки временных интервалов, формирователь 7 компенсационного сигнала, формирователь

8 импульсов грубого отсчета, формирователь 9 ьыходных кодов, формирователь 10 импульсов точного отсчета, триггеры 11 и

12. Формирователь 10 содер>кит триггер 13, дифференцирующий элемент 14 и элемент

15 И.

Блок 6 задержки временных интервалов (фиг.2) содержит реверсивный счетчик 16, триггеры 17 и 18, элементы 19, 20 И-НЕ, ин вертор 21. Формирователь 7 компенсационного сигнала (фиг.3) содержит инверторы

22 и 23, дифференцирующие элементы 24 и

25, элемент 26 И, элемент 27 И-НЕ, элемент

28 ИЛИ-НЕ, реверсивный счетчик 29. Формирователь 8 импульсов грубого отсчета (фиг.4) содержит реверсивный счетчик 30, триггер 31, элемент 32 И-НЕ и инвертор 33.

Формирователь выходных кодов (фиг.5) содержит инверторы 34 и 35, элементы 36, 37

2И-2ИЛИ-НЕ. Дифференцирующий элемент

14 (фиг,6) содержит триггеры 38 и 39, элемент 40 ИСКЛЮЧАЮЩЕЕ NflN.

Преобразователь работает следующим образом.

Генератор 1 формирует высокочастотные сигналы (фиг.7, 8, 9а). В формйрователе

2 производится деление по частоте импульсов генератора 1 и выделяется первая гармоническая составляющая низкочастотного сигнала, которая является опорным сигна30

50 нал по отношению к компенсационному сигналу, импульс, соответствующий. модулю фазового сдвига, с выхода фазового дискриминатора 5 поступает на вход блока 6 и открывает элемент 19М-НЕ для прохох<дения импульсов генератора 1 на суммиру ощий вход реверсивного счетчикам 16 (фиг.9, в). По заднему фронту импульса фазового дискриминатора 5, инвертированного инвертором 21 (фиг,9, г), триггер 17 блока 6 (фиг,9, д) и триггер 31 формирователя 8 (фиг.7, 8, M) устанавливаются в единичное состояние, Открывается элемент 20 и выходные импульсы генера — îðà 1 поступают на вычитающий вход реверсивного счетчика

16 (фиг.9, ж). Прл нулевом значении кода реверсивный счетчик 16 формирует импульс (фиг,9, з), по которому производится сброс триггера 17. Триггером 18 вырабатывается сигнал (фиг,9, е), задержанный на один период по отношени о к выходному слгналу триггера 17, Реверсивный счетчик 29 вырабатывает компенсационный сигнал, непрерывно суммируя импульсы, сформированные дифференцируощим элементом 24 по срезам импульсов генератора 1. Прямой и инвертированный инвертором 23 сигналы знака фазового сдвига йоступают на первые управляющие входы элементов 26 и 27, на вторые управляющие Входы которых постулом, поступающим на вход фазовращателя

3, В фаэовращателе 3 происходит преобразование перемещения в фазовый сдвиг между фазным выходным сигналом фазовращателя 3 и его входным опорным слгналом. Нуль-орган 4 формирует прямоугольные импульсы (фиг. 7, 8, б) из фазного выходного сигнала фазовращателя

3. Фронты вь|ходных сигналов нуль-органа

"0 4 совпадают с моментами перехода через нуль фазного сигнала. В триггере 11 (фиг,7, 8, г) фронть выходных сигналов нуль-органа

4 синхронизируются импульсами генератора 1, В фазовом дискриминаторе 5 опреде"5 ляются модуль и знак фазового сдвига между фазным сигналом с выхода триггера

11 (фиг,7, 8, г) и компенсационным сигналом с выхода триггера 12 (фиг.7, 8, д), 1Лодуль фазового сдвига формируется в фазовом дискриминаторе 5 в виде импульса (фиг.7, 8, л, фиг.96), длительность которого соответствует временному интервалу между передними фронтами фазно-.о и компенсационного сигналов между передними фронтами фазного и компенсационного сигналов с Выходов триггеров 11 и 12, Знак фазового сдвига формируется В виде ециничного или нулевого сигнала (фиг,7, 8, к) в зависимости от того, отстает или опере>кает по фазе фазнь1й сиг1790802 способность преобразователя перемещения в унитарный код увеличивается вдвое.

50

55 атсч та, первый и второй триггеры, выходы, н.л -сргана соединен с первым входом форпает выходной сигнал триггера 18 блока 6, длительность которого соответствует модулю фазового сдвига; На выходах элементов

26 и 27 формируются импульсы, соответствующие передним фронтам импульсов генератора 1. Число импульсов на выходе каждого из элементов 26 и 27 соответствует модулю фазового сдвига, а наличие импульсов на выходе одного из этих элементов определяется знаком фазового сдвига, Выходные импульсы элементов 26 и 27 поступают соответственно на суммирующий и вычитающий входы реверсивного счетчика

29, сдвигая по фазе компенсационный сигнал с выхода старшего разряда счетчика 29 в сторону устранения рассогласования между ним и фазным сигналом с выхода триггера 11, Выходной сигнал реверсивного счетчика 29 синхронизируется в триггере 12 импульса ли генератора 1.

Па заднему фронту импульса фазового дискриминатора 5, прошедшего через инвертор 21 блока 6, выходной код счетчика 16 переписывается в счетчик 30 со сдвигом на один разряд в сторону старших разрядов.

При этом триггер 31 устанавливается в единицу (фиг.7, 8, м) и открывается элемент 32 для прохождения импульсов со второго выхода генератора 1, Выходные импульсы элемента 32 поступают на вычитающий вход реверсивного счетчика 30 и через инвертор

33 — на выход формирователя 8. При нулевом значении кода реверсивный счетчик 30 формирует импульс, по которому производится сброс триггера 31 (фиг,7, 8, м). В результате длительность выходного импульса триггера 31 вдвое превышает длительность выходного импульса фазового дискриминатора 5 и сдвинут относительно его па фазе. В зависимости от знакового сигнала с выхода фазового дискриминатора 5 (фиг.7, 8, к) выходные импульсы формирователя 8 коммутируются элементами 36 и 37 формирователя 9 на одну или другую выходные

Формула изобретения

Преобразователь перемещения в унитарный код, содержащий последовательно соединенные генератор импульсов, формирователь опорного сигнала, фазавращатель и нуль-орган, фазовый дискриминатор, формирователь ко лпенсационного сигнала, первый вход которого подключен к первому выходу генератора импульсов, о т л и ч а юшийся тем, чта, с целью повышения

30 Г

40 шины устройства (фиг,7; о, фиг, 8, н), в результате чего осуществляется преобразование временных интервалов в унитарный код грубого отсчета. Число импульсов с выхода формирователя 8 вдвое превышает число квантов рассогласования между фазным и компенсационным сигналами.

Формирователь 10 предназначен для формирования дополнительных импульсов точного отсчета с соответствующим знаком перемещения и уменьшенной вдвое их ценой по сравнению с ценой импульсного унитарного кода грубого отсчета. Триггер 13 устанавливается в единицу или ноль (фиг.7, 8, в) в зависимости от совпадения фиксированного значения фаэного сигнала (фронта выходного импульса нуль-органа 4) с импульсами и паузами высокочастотного сигнала генератора 1. На выходе триггера t3 формируется знак перемещения точного отсчета. Выходной сигнал триггера 13 синхронизируется в триггере 38 сигналом с второго выхода генератора 1 (фиг.7, 8, и) и сдвигается на один такт в триггере 39. Выходные сигналы триггера 38 (фиг.7, 8, е) v. триггера

39 (фиг.7, 8, ж) поступают на входы элемента

40 ИСКЛЮЧАЮЩЕЕ ИЛИ, на выходе которого формируются импульсы (фиг.7, 8, з), соответствующие фронтам синхронизированного сигнала триггера 13, Из этих импульсов элементом 15 И формируются импульсы, равные по длительности выходным импульсам генератора 1. В зависимости от знакового сигнала с выхода триггера

13 (фиг,7, 8, в) выходные импульсы элемента

15 И коммутируются элементами 36 и 37 формирователя 9 на соответствующие выходные шины преобразователя (фиг.7, н) фиг.8, о), при этом происходит суммирование дополнительных импульсов точного QTсчета формирователя 10 с унитарным кодом грубого отсчета. В результате разрешающая разрешающей способности преабразоватегя, в нега введены блок задержки временных интервалов, формирователь импульсов грубого отсчета, формирователь выходных кодов, формирователь импульсов точного миравателя импульсов точного отсчета и с ин формационным входом первого триггера, выход которого соединен с первым входом

1790802 фазового дискриминатора, первый и второй выходы фазового дискриминатора соединены соответственно с первым входом блока задержки временных интервалов и с вторым входом формирователя компенсационного сигнала, группа выходов, первый и второй выходы блока задержки временных интервалов соединены соответственно с группой входов и с первым входом формирователя импульсов грубого отсчета и с третьим входом формирователя компенсационного сигнала, выход которого соединен с информационным входом второго триггера, выход второго триггера соединен с вторым входом фазового дискриминатора, первый выход генератора импульсов соединен с синхронизирующими входами первого и второго триггеров и с вторыми входами блока задержки временных интервалов и формирователя импульсов точного отсчета, 5 второй выход генератора импульсов соединен с вторым входом формирователя импульсов грубого отсчета и с третьим входом формирователя импульсов точного отсчета, второй выход фазового дискриминатора, 10 выход формирователя импульсов грубого отсчета, первый и второй выходы формирователя импульсов точного отсчета соединены соответственно с входами с первого по четвертый формирователя выходных кодов, 15 выходы которого являются выходами преобразователя. I790802

<Т90802

179000< :

Г ЮЖ ЮБЕ ЮБЮБЕЕБ

Я Щ ДЙ=

М РУ,РР - * БЙБ7 ",БЯ2ЕИВЗЕИББЕЗЯ.

3 3ЕЗИЕРХВЕЕЕЕЕРАЮЖТ Ю7 ЙЕ32ЛЕРЗ

Составитель A,Ñèäopîâ

Техред М.Моргентал Корректор Н,Милюкова

Редактор

Производственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарина, 101

Заказ 376 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4i5