Устройство для ввода информации в калькулятор

Иллюстрации

Показать всеРеферат

Изобретение относится к устройствам ввода информации в клавишные вычислительные машины, в частности в калькуляторы . Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения режима приостанова решения задачи. Устройство содержит первый и второй регистры, первый и второй преобразователи кодов, мультиплексор, блок управляющей памяти, первый и второй счетчики, блок памяти команд, блок ключей, блок пуска, дешифратор, индикатор, триггер , элемент НЕ, первый, второй и третий элементы И, первый, второй элементы ИЛИ, с первого по четвертый формирователи импульсов , первый и второй тактовые входы устройства, информационные входы и выходы устройства. Блок пуска содержит второй и третий триггеры, первый и второй переключатели , Устройство позволяет решать задачи с переменными, вводимыми в процессе решения задачи. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (st)s G 06 F 3/00

ГОСУДАРСТВЕННЫИ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4795064/24 (22) 09,01.90 (46) 30,01.93, Бюл, М. 4 (71) Завод электронных вычислительных машин им. 50-летия СССР (72) В.А.Андреев и В.Е.Лаптев (56) Авторское свидетельство СССР

N. 1718210, кл, G 06 F 3/00, 1988, (54) УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ В КАЛЬКУЛЯТОР (57) Изобретение относится к устройствам ввода информации в клавишные вычислительные машины, в частности в калькуляторы. Целью изобретения является расширение фун кционал ьн ых возможностей устройства за счет обеспечения режима приостанова

Изобретение относится к устройствам ввода информации в клавишные вычислительные машины, в частности в калькуляторы.

Целью изобретения является расширение функциональных возможностей устройства путем обеспечения режима приостанова решения задачи.

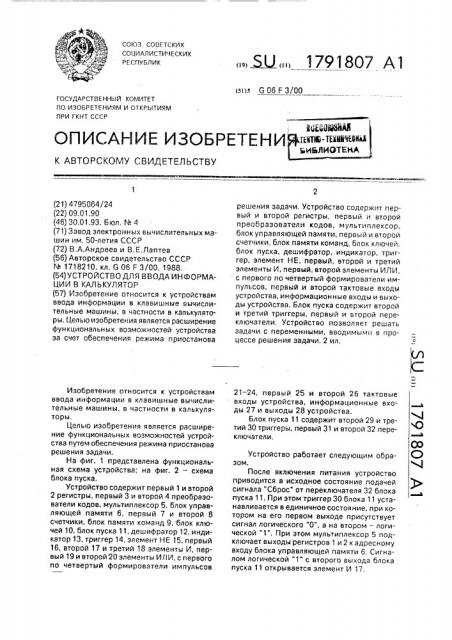

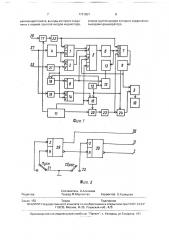

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 — схема блока пуска.

Устройство содержит первый 1 и второй

2 регистры, первый 3 и второй 4 преобразователи кодов, мультиплексор 5, блок управляющей памяти 6, первый 7 и второй 8 счетчики, блок памяти команд 9,.блок ключей 10, блок пуска 11, дешифратор 12, индикатор 13, триггер 14, элемент НЕ 15, первый

16, второй 17 и третий 18 элементы И, первый 19 и второй 20 элементы ИЛ И, с первого по четвертый формирователи импульсов,, !(2,, 1791807 А1 решения задачи. Устройство содержит первый и второй регистры, первый и второй преобразователи кодов, мультиплексор, блок управляющей памяти, первый и второй счетчики, блок памяти команд, блок ключей, блок пуска, дешифратор, индикатор, триггер, элемент НЕ, первый, второй и третий элементы И, первый, второй элементы ИЛИ, с первого по четвертый формирователи импульсов, первый и второй тактовые входы устройства, информационные входы и выходы устройства, Блок пуска содержит второй и третий триггеры, первый и второй переключатели, Устройство позволяет решать задачи с переменными, вводимыми в процессе решения задачи. 2 ил.

21 — 24, первый 25 и второй 26 тактовые входы устройства, информационные входы 27 и выходы 28 устройства.

Блок пуска 11 содержит второй 29 и третий 30 триггеры, первый 31 и второй 32 переключатели.

Устройство работает следующим образом.

После включения питания устройство приводится в исходное состояние подачей сигнала "Сброс" от переключателя 32 блока пуска 11, При этом триггер 30 блока 11 устанавливается в единичное состояние, при котором на его первом выходе присутствует сигнал логического "0", а на втором — логической "1", При этом мультиплексор 5 подключает выходы регистров 1 и 2 к адресному входу блока управляющей памяти 6. Сигналом логической "1" с второго выхода блока пуска 11 открывается элемент И 17.

1791807

Для решения задачи на клавиатуре калькулятора набирается номер выбранной задачи двумя старшими разрядами, то есть номера задач могут быть от 0 до 99.

Семисегментный код номера выбранной задачи поступает от индикатора калькулятора по шине 27 на вход преобразователя кодов 4 и входы элемента ИЛИ 19. Разряды номера задачи поступают на вход преобразователя кодов 4 синхронно с соответствующими управляющими тактовыми сигналами на шинах 25 и 26. Старший разряд номера задачи поступает синхронно с TBKTQBb! м сигналом на шине 25, а второй старший разряд поступает синхронно с тактовым сигналом на шине 26. Преобразователь кодов 4 преобразует семисегментный код в двоична-десятичный и выдает его на входы регистров 1 и 2. По первому тактовому сигналу с шины

25 двоична-десятичный код первого разряда заносится в регистр 2, а второй тактовый сигнал заносит информацию в регистр 1. С выходов регистров 1 и 2 код номера задачи поступает через мультиплексор 5 на адресные входы управляющей памяти 6. Вход обращения к блоку памяти 6 соединен с одним из полюсов источника питания устройства таким образом, что постоянно присутствует выборка блока 6. В блоке 6 хранятся адреса программ решаемых задач. С выхода блока

6 адрес решаемой задачи по второму тактовому сигналу заносится в счетчик 7, С выхода счетчика 7 начальный адрес программы поступает на адресный вход блока памяти команд 9, При этом с блока памяти команд

9 считывается первая команда программы решаемой задачи. В первой команде программы на выходе блока 9 считывается код

"1", который поступает на третий вход элемента И 16 и второй вход формирователя 24 и подготавливает их к работе, а через элемент НЕ 15 закрывает дешифратор 12 и элемент И 18 по первому входу. Затем от блока пуска 11 подается сигнал пуска от переключателя 31. При этом триггер 29 формирует на единичном выходе сигнал, который поступает на второй вход элемента

ИЛИ 20, а сигналом с нулевого выхода устанавливает в нулевое состояние триггер 30, Сигналом логического "0" с единичного выхода триггера 30 закрывается элемент И 17, запрещая прохождение второго тактового сигнала с шины 26 устройства, при этом блокируется дальнейший прием в счетчик 7, в котором зафиксирован начальный адрес программы решаемой задачи. С нулевого выхода триггера 30 блока 11 сигнал логического "0" поступает на второй вход элемента И 16 и управляющий вход мультиплексора 5. При этом мультиплексор

5 подключает выход счетчика 8 и первый выход блока памяти команд 9 к адресному входу блока управляющей памяти 6. Сигнал с выхода элемента ИЛИ 20 запускает формирователь 23, сигнал с которого поступает на счетный вход счетчика 7 и добавляет к его содержимому единицу, По новому содержимому счетчика 7 выбирается следующая команда программы блока 9, которая с первого выхода блока 9 поступает на вход преобразователя кодов 3. На выходе блока

9 выбирается также код логической "1" и, поступая на второй вход формирователя 24, разрешает его пуск. Задним фронтом сигнала с выхода формирователя 23 запускается формирователь 24, который формирует сигнал времени нажатия кнопки. Сигнал с формирователя 24 поступает на управляющий вход преобразователя кодов 3, который и реобразовывает двоичный код, поступающий с блока 9, B сигнал на включение соответствующего ключа блока ключей 10. Ключи блока 10 подсоединены по шине 28 параллельно клавишам калькулятора. Замыкание ключа имитирует нажатие соответствующей клавиши калькулятора. При этом калькулятор начИнает выполнять соответствующую операцию, на время которой прекращается выдача семисегментного кода на индикацию. По окончании выполнения операции калькулятор выдает результаты операции на индикацию, то есть семисегментный код на вход элемента ИЛИ 19, При этом по первому тактовому входу с шины 25 триггер 14 взводится и открывает элемент И 16. Сигналом с выхода элемента И 16 через элемент ИЛИ

20 запускается формирователь 23, который увеличивает содержимое счетчика 7 и запускает формирователь 24, и вычислительный процесс продолжается.

При необходимости ввода данных о переменных в процессе выполнения программы решаемой задачи с блока памяти команд

9 считывается команда, которая содержит по второму выходу блока памяти команд 9 код логического "0", а по выходам — начальный адрес символа переменной, Код логического "0" с выхода блока 9 поступает на вход элемента НЕ 15, на третий вход элемента И

16 и второй вход формирователя 24, закрывая их. При этом вычислительный процесс приостанавливается, так как на выходе элемента И 16 сигналы не вырабатываются. С выхода элемента НЕ 15 сигнал логического

5

"0" поступает на вход дешифратора 12 и первый вход элемента И 18 и открывает их, Первый тактовый импульс с шины 25 проходит через формирователь 21 и элемент И 18 на счетный вход второго счетчика 8. Сигналы с выхода счетчика 8 и начальный адрес

1791807

10

55 символа переменной с первого выхода блока памяти команд 9 поступают через второй информационный вход мультиплексора 5 на адресный вход блока памяти 6. Считанные данные с блока управляющей памяти 6 о символе переменной поступают на второй вход индикатора 13. Кроме того, сигналы со счетчика 8 поступают на информационный вход дешифратора 12. При этом дешифратор 12 последовательно вырабатывает сигналы на своих выходах, которые поступают на первый вход индикатора 13, При пробегании счетчиком 8 значений от нуля до максимального на индикаторе 13 высвечивается символ переменной. В соответствии о высвечиваемым символом переменной оператор вводит с клавиатуры калькулятора численное значение переменной. После ввода переменной устройство запускается с помощью переключателя 31 блока пуска

11. При этом логическая "1" с выхода блока

9 открывает формирователь 24 и элемент И

16 для дальнейшего прохождения программы, а через элемент НЕ 15 закрывает элемент И 18 и запрещает выборку дешифратором 12 сигналов на своих выходах. При запрещении работы дешифратора

12 гаснет символ переменной на индикаторе 13 и процесс вычисления продолжается, Процесс ввода переменных может повторяться программой и количество вводимых переменных не ограничивается. По окончании вычислительного процесса на выходе блока памяти 9 считывается ноль и процесс останавливается. На индикаторе 13 при этом высвечивается символ окончания решения задачи, например символ "К", а на индикаторе кал ькуляторэ — резул ьтат решения. Для приведения устройства в начальное состояние подается сигнал сброса от переключателя 32 блока 11.

Устройство позволяет решать задачи с переменными, вводимыми в процессе решения задачи, а также обеспечивает диалог и подсказку оператору о вводимой переменной.

Формула изобретения

Устройство для ввода информации в калькулятор, содержащее первый и второй регистры, первый и второй преобразователи кодов, блок управляющей памяти, первый счетчик, блок памяти команд, блок ключей, блок пуска, триггер, с первого по четвертый формирователи импульсов, первый, второй и третий элементы И, первый элемент ИЛИ, при этом информационные входы первого и второго регистров соединены с выходами второго преобразователя кодов, входы которого соединены с

40 информационными входами устройства,1 входами первого элемента ИЛИ, выход которого соединен с информационным входом триггера, тактовый вход которого соединен с входом записи второго регистра и выходом первого формирователя импульсов, вход которого является первым тактовым входом устройства, вход записи первого регистра соединен с входом записи первого счетчика и выходом второго фармиравателя импульсов, вход которого соединен с выходом второго элемента И, второй вход которого является вторым тактовыл входом устройства, а первый соединен с вторым выходом блока пуска, первый выход которого соединен с BTopblM входом первого элемента И, первый вход которого сеединен с выходом триггера, выходы блока управляющей памяти соединены с информационными входами первого счетчика, тактовый вход которого соединен с выходом третьегс и первым входом четвертого формиравэ е;-ей импульсов, а выходы соединены с адресными входами блока памяти команд, выходы которого соединены с информационными вхадал1и первого преобразователя кодов, управляющий вход которого соединен с выходам четвертога формирователя импульсов, а выходы — с входами блока ключей, выходы которого являются информационными выходами устройства, а т л и ч а ощ е е с я тем, что, с целью расширения функциональных возможностей устройства путем обеспечения режима приастанава решения задачи, в него введены мультиплексор, второй счетчик, дешифратор, индикатор, второй элемент ИЛИ, элемент

HF, причем первая группа информационных входов мультиплексора соединена соответственно с выходами первого и второго регистров, а вторая группа входов — с выходами блока памяти команд и второго счетчика, выходы которого также соединены с входами дешифраторэ, управляющий вход дешифратора соединен с выходом элемента

НЕ и первым входом третьего элел1ента И, второй вход которого соединен с тактовым входом триггера, а выход — с тактовым вхадом второго счетчика, адресные входы мул ьтиплексорэ соединены с первым выходом блока пуска. третий выход которого соединен с вторым входом второго элемента

ИЛИ, выход которого соединен с входом третьего формирователя импульсов, э первый вход — с выходом первого элел1ента И, третий вход которого соединен с входом элемента HE. вторым входом четвертага формирователя импульсов и выходам блока памяти команд, выходы мультиплексора соединены с адресными входами блока уп1791807

Составитель А,Алексеев

Техред М.Моргентал Корректор Q.ÊðàBöoaà

Редактор

Заказ 152 Тираж Подписное

RHVIVIRVI Государственного комитета по изобретениям и открытиям при ГККТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул,Гагарина, 101 равляющей памяти, выходы которого соеди- вторая группа входов которого соединена с нены с первой группой входов индикатора, выходами дешифратора,