Цифровой интегратор

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в устройствах ввода-вывода микроЭВМ и телеметрических устройствах. Цель изобретения -- повышение точности интегрирования. Цель достигается тем, что цифровой интеграл содержит первый и второй генераторы тактовых импульсов, с первого по третий элементы И, элемент ИЛИ, первый и второй счетчики, накапливающий сумматор и дешифратор . 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 G 06 F 7/64

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

IlG ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

OO

0 (21) 4848264/24 (22) 11.05.90 (46) 30.01.93. Бюл, N 4 (71) Муромский филиал Владимирского политехнического института . (72) В.В,Чекушкин, Б,В.Амосов и С.В,Чекушкин (56) Чекушкин В, В. Анализ ошибок цифрового интегратора с параллельным переносом. Известия вузов. — Приборостроение, 1989, т. XXXII, N 10.

Авторское свидетельство СССР

N. 525945, кл, G 06 F.5/02, 1976, Изобретение относится к области вычислительной техники и может быть использовано в устройствах вывода электронных вычислительных машин и телеметрических устройствах.

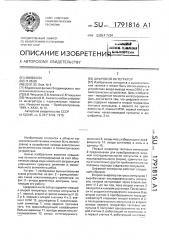

Целью изобретения является повышение точности интегрирования эа счет обеспечения ввода кода начальной загрузки для уменьшения среднего значения и максимального значения ошибок, На фиг. 1 изображена функциональная схема устройства; на фиг. 2 — функциональная схема накапливающего сумматора; на фиг. 3 — эпюры временных диаграмм, пояс-, няющие его работу.

Цифровой интегратор содержит первый и второй генераторы тактовых импульсов 9 и 1, первый, второй и третий элементы И 10, 2 и 6, первый и второй счетчики 4 и 3, элемент ИЛИ 12, дешифратор 5, накапливающий сумматор 7, вход задания признака того, что масштабирующий коэффициент больше единицы 11, выходы результата интегрирования 13, входы интегрируемого Ы 1791816 Al (54) ЦИФРОВОЙ ИНТЕГРАТОР (57) Изобретение относится к вычислительной технике и может быть использовано в устройствах ввода-вывода микроЭВМ и телеметрических устройствах. Цель изобретения — повышение точности интегрирования.

Цель достигается тем; что цифровой интеграл содержит первый и второй генераторы тактовых импульсов, с первого по третий элементы И, элемент ИЛИ, первый и второй счетчики, накапливающий сумматор и дешифратор. 3 ил. значения 8, входы масштабирующего коэффициента 14, входы установки в ноль и в единицу 15, Первый генератор тактовых импульсов

9 предназначен для преобразования входной последовательности импульсов в две последовательности (серии), сдвинутых одна относительно другой приблизительно на половину периода следования импульсов.

Цифровой интегратор работает следующим образом.

Второй генератор тактовых импульсов 1 вырабатывает последовательность импульсов, которая не проходит через второй элемент И 2 до тех пор, пока второй счетчик 3 находится в нулевом состоянии. После записи по входам интегрируемого значения 8 so второй счетчик 3 преобразуемого числа дешифратор 5 открывает второй элемент И 2, и последовательность импульсов со второго выхода первого генератора тактовых импульсов 9 поступает одновременно во второй счетчик 3, работающий на вычитание, и в первый счетчик 4, работающий на сложе1791816

Если К>1, то перед началом пересчета на вход признака масштабного коэффициента 11 подают сигнал "1", разрешающий дополнительно прохождение импульсов с

M(7, nj= ——

3 3+n

4 4,?л первого выхода первого генератора такто22 вых импульсов в первый счетчик 4. В остальДля п=5 получим M(t, 5j= 32 . ном схема работает так же, как и при К<1, 55 Введение входов начальной установки в

Поскольку в процессе работы остаток в ноль и в единицу позволяет Уменьшить накапливающем сумматоре 7 всегда мень- среднее значениеошибки практическидо0, ше 1, то в результате интегрирования в пер- а максимальное значение — на 25%. вом счетчике 4 будет зафиксировано число Пример конкретного выполнения накапливающего сумматора 7. Накапливаюние импульсов. При этом во второй счетчик

3 импульсы поступают непосредственно, а в первый счетчик 4 — через третий элемент

И 6 при совпадении с импульсами переноса накапливающего сумматора 7. В момент равенства счетных импульсов двоичному числу, записанному ранее во второй счетчик 3, дешифратор 5 закрывает второй элемент И 2.

При этом во втором счетчике 4 фиксируется выходное число, например, в двоична-десятичном коде, умноженное на масштабирующий коэффициент К, код которого устанавливается на входах 14 и 11, Например, при К=5/32 перед преобразованием на вход признака масштабного коэффициента подается сигнал "0" (так как К<1), а на входы масштабирующего коэффициента цифрового интегратора 14 — код дробной части числа К, т,е, 0,00101.

Число К будет добавляться в накапливающий сумматор 7 при поступлении на его вход синхронизации каждого импульса со второго выхода первого генератора тактовых импульсов 9. При этом число импульсов переполнения накапливающего сумматора 7, а следовательно, и число счетных импульсов на выходе третьего элемента

И 6 будет пропорционально К.

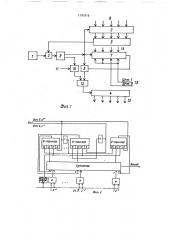

Временная диаграмма работы устройства приведена на фиг. 3.. Эпюра U< изображает импульсы на входе синхронизации накапливающего сумматора 7 и в счетном входе второго счетчика 3. Эпюры Uz и язв соответственно импульсы на выходе TpQTbего элеме ITQ И 6, погрешность преобразования при К вЂ” -5/32 и начальном состоянии сумматора 00000. Значение погрешности по оси ординат откладывается в долях единицы младшего разряда выходного кода. Значение ошибки определяется по отношению к идеальному алгоритму интегрирования.

На эпюре Бз горизонтальной линией показано также значение математического ожидания при числе разрядов накапливающего сумматора n=-5, В общем случае значение математического ожидания, относимое ко всем комбинациям значений коэффициента

К, определяется выражением

45 с погрешностью, не превышающей единицы младшего разряда выходного кода. При нулевом начальном состоянии накапливающего сумматора 7 (эпюра Бз) указанная погрешность всегда отрицательна, и ее максимальное абсолютное значение равно

-n 31 смаке=1 2, Для п=5, /макс = — (код в на32 капливающем сумматоре 7 11111).

При произвольном начальном состоянии накапливающего сумматора 7 погрешность в общем случае будет разнополярной, и ее максимальное абсолютное значение тока может быть близко к единице, а среднее значение ошибки не скомпенсировано, Поэтому в предложенном цифровом интеграторе перед началом пересчета по входам установки в единицу и в ноль 15 в накапливающий сумматор 7 заносят код 10111, т,е. триггеры Н-ro разряда и разрядов с первого по (Н-2)-й накапливающего сумматора 7 устанавливаются в единицу, а (Н-1)-ro разряда — в ноль, Тогда при пересчете независимо от величины К первый и все последующие импульсы переноса с выхода накапливающего сумматора 7 будут появляться раньше по отношению к импульсам переноса накапливающего сумматора 7 при его начальном нулевом состоянии, вследствие чего средняя ошибка будет практически скомпенсирована. На эпюрах Uq u Uq приведены соответственно импульсы на выходе третьего элемента И 6 и погрешность преобразования при К=5/32 и начальной установке накапливающего сумматора 7 в состояние

10111. На эяюре Ug горизонтальной линией показано также значение математического ожидания ошибки после его компенсации, 1 т.е. М= —. 32

Уменьшение среднего значения ошибки интегратора производится более чем в 10 раз. Контур изменения максимальной ошибки остается прежним, но смещается. Максимальная ошибка уменьшается не менее чем на 25%.

1791816 щий сумматор 7 имеет следующие входы и выходы (фиг. 2):

Вх. 1 — вход синхронизации;

Бх. 3 — информационные входы накапливающего сумматора 7, эти входы соответствуют входам масштабирую щего коэффициента К 14, Вх. 2 — входы установки в нуль и в единицу 15;

Вых. — выход соответствует выходу переноса накапливающего сумматора 7.

Накапливающий сумматор 7 включает группу вентильных элементов И, управляемых с информационных входов и с входа синхронизации. Таким образом осуществляется формирование числа с информационных входов на первых входах сумматора во время действия импульсов синхронизации. На вторые входы сумматора подается числовой код с выходов регистра кода, выполненного на D-триггерах, Сформированная на выходах сумматора сумма чисел поступает на информационные входы Dтриггеров. Перепись информации в 0-триггеры осуществляется задержанным импульсом с элемента задержки для устранения "гонки фронтов". Импульс переполнения сумматора является выходным импульсом переноса накапливающего сумматора 7.

D-триггеры имеют входы установки в

"1" — S и установки в "0" — R. Перед началом работы по входам начальной установки в регистре, а следовательно, и в накапливающем сумматоре 7 устанавливается значение кода 101„.1, 0-триггеры выполнены, например, на

D-триггерах 564ТМ2, сумматор выполнен на микросхемах четырехраэрядн ых сумматоров 564ИМ1 по типовой схеме включения.

Накапливающий сумматор 7 работает следующим образом. Со Вх. 2 задается. код начальной установки, обеспечивающий компенсацию средней ошибки. На Вх. 3 подается двоичный код коэффициента К, после чего на Вх. 1 (синхронизации) подаются счетные импульсы. При каждом переполнении накапливающего сумматора 7 выдается импульс переноса.

Введение входов установки в ноль и в единицу цифрового интегратора позволяет практически полностью скомпенсировать среднее значение ошибки и уменьшить не менее чем на 25 g, максимальное значение ошибки.

Использование предложенного цифрового интегратора в устройствах вывода

ЭВМ и в измерительных устройствах позволит без увеличения аппаратурных затрат

5 снизить суммарную погрешность подобных устройств.

Формула изобретения

Цифровой интегратор, содержащий

10 первый и второй генераторы тактовых импульсов, с первого по третий элементы И, элемент ИЛИ, первый и второй счетчики, накапливающий сумматор и дешифратор, причем вход признака того, что масштаби15 рующий коэффициент больше единицы цифрового интегратора, подключен к первому входу первого элемента И, выход которого подключен к первому входу элемента ИЛИ, выход которого подключен к счетному входу

20 первого счетчика, информационные выходы которого подключены соответственно к выходам результата интегрирования цифрового интегратора, входы интегрируемого значения которого подключены соответст25 венно к информационным входам второго счетчика, информационные выходы которого подключены соответственно к информационным входам дешифратора. выход которого подключен к первому входу второ30 го элемента И, выход которого подключен к входу запуска первого генератора тактовых импульсов, первый выход которого подключен к второму входу первого элемента И, входы масштабирующего коэффициента

35 цифрового интегратора подключены соответственно к информационным входам разрядов накапливающего сумматора, выход переноса которого подключен к первому входу третьего элемента И, выход которого

40. подключен к второму входу элемента ИЛИ, выход второго генератора тактовых импульсов подключен к второму входу второго элемента И, второй выход первого генератора тактовых импульсов подключен к входу син45 хронизации накапливающего сумматора, к счетному входу второго счетчика и к второму входу третьего элемента И, о т л и ч а ю щ ее с я тем, что, с целью повышения точности интегрирования, вход установки в "0" цифро50 вого интегратора подключен к входу установки в "0" (Н-1)-ro разряда накапливающего сумматора, вход установки в" 1" цифрового интегратора подключен к входам установки в "1" Н-го разряда и разрядов с первого по

55 (Н-2) накапливающего сумматора.

1791816

1791016

Составитель В.Чекушкин

Техред М,Моргентал Корректор О,Кравцова

Редактор

Производственно-издательский комбинат "Патент", г. Ужгород. Ул, Гагарина, 101

Заказ 152 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5