Устройство для восстановления постоянной составляющей

Иллюстрации

Показать всеРеферат

Изобретение относится к телевидению, в частности к приемным станциям спутникового телевидения, и может быть использовано при создании специализированных интегральных микросхем, Цель изобретения - повышение помехоустойчивости и расширение динамического диапазона. Устройство содержит дифференциальный видеоусилитель , два конденсатора, два транзисторных ключа, синхроселектор и дифференциальный блок выборки хранения. Низкочастотная помеха, наложенная на видеосигнал, подавляется за счет стабилизации привязки уровня синхроимпульсов к опорному напряжению , что также расширяет динамический диапазон .. 2 з. п. ф-лы, 1 ил. (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 Н 04 N 5/16

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4883606/09 (22) 16,11.90 (46) 07.02.93. Бюл, ¹ 5 (71) Конструкторское бюро Красноярского завода телевизоров и Красноярский политехнический институт (72) В, И. Юзов, Г, М, Рагзин, Е. Г, Хазанкин и В, А. Чавлытко (56) Авторское свидетельство СССР

¹ 1642935; кл, Н 04 N 5/16, 1989, (54) УСТРОЙСТВО ДЛЯ ВОССТАНОВЛЕНИЯ ПОСТОЯННОЙ СОСТАВЛЯЮЩЕЙ (57) Изобретение относится к телевидению, в частности к приемным станциям спутникоИзобретение относится к телевидению в частности к приемным станциям спутникового телевидения, и может быть использовано при создании специализированных интегральных микросхем.

Известно устройство для восстановления постоянной составляющей телевизионного сигнала, содержащее первый и второй конденсаторы, ключ, резисторы, дифференциальный усилитель и преобразователь напряжения в ток, первый вывод первого конденсатора является входом устройства, второй — его выходом, последовательно соединенные ключ, интегратор, образованный резистором, дифференциальным усилителем и вторым конденсатором; и преобразователь напряжения в ток своими входом и выходом соединены с вторым выводом первого конденсатора, управляющий вход ключа — с выходом синхроселектора, а второй вход дифференциального усилителя — с источником смещения. Ы 1793558 А1 вого телевидения, и может быть использовано при создании специализированных интегральных микросхем, Цель изобретения— повышение помехоустойчивости и расширение динамического диапазона. Устройство содержит дифференциальный видеоусилитель, два конденсатора, два транзисторных ключа, синхроселектор и дифференциальный блок выборки хранения. Низкочастотная помеха, наложенная на видеосигнал, подавляется за счет стабилизации привязки уровня синхроимпульсов к опорному напряжению, что также расширяет динамический Я диапазон, 2 з. и. ф-лы, 1 ил.

Установка известного устройства на входе видеоусилителя приводит к снижению точности восстановления зэ счет дрейфа нуля видеоусилителя, установка нэ 0 выходе снижаетдинамическийдиапазон ви- (, } деоусилителя при зашумленности сигнала, (Я в обоих случаях точность восстановления (Л постоянной составляющей оказывается не- р достаточной.

Известно также устройство для восстановления постоянной составляющей, выбранное в качестве прототипа и содержащее дифференциальный видеоусилитель, первый и второй конденсаторы, первый и второй резисторы, по одному выводу которых подключено к источнику смещения, первый и второй транзисторы, транзисторный ключ, выход которого соединен с змиттерэми первого и второго транзисторов, селектор разбаланса, первый и второй выходы которого соединены соответственно с базами первого и второго транзисторов, 1793558 первый вход подключен к выходудифференциального усилителя, а второй — к источнику напряжения смещения, и синхроселектор, вход которого соединен с выходом дифференциального усилителя, а выход — с входом ключа, вторые выводы первых конденсатора, резистора и коллектор первого транзистора соединены с первым входом дифференциального усилителя, вторые выводы вторых конденсатора, резистора и коллектор второго транзистора — с его вторым входом, первый вывод второго конденсатора заземлен.

Если известное устройство устанавливается непосредственно после фильтров или иных колебательных систем, из-за подачи импульсных напряжений на входные разделительные конденсаторы возникают переходные процессы, снижающие динамический диапазон и помехоустойчивость приемного тракта.

Цель изобретения — повышение помехоустойчивости и расширение динамического диапазона.

Указанная цель достигается тем, что в устройство для восстановления постоянной составляющей, соде ржащее последовательно соединенные дифференциальный видеоусилитель, синхроселектор и

25 транзисторный ключ, первый и второй кон- 30 денсаторы, причем первый конденсатор включен между источником сигнала и первым входом дифференциального видеоусилителя, второй — между его вторым входом и землей, дополнительно введены второй 35 транзисторный ключ, вход которого подключен к выходу синхроселектора и дифференциальный блок выборки-хранения, первый и второй, сигнальные входы которого подключены соответственно к второму 40 выходу дифференциального видеоусилителя и источнику опорного напряжения, третий и четвертый управляющие входы — к выходам первого и второго транзисторных ключей, а выход соединен с третьим, управ- 45 ляющим входом дифференциального видеоусилителя, Дифференциальный блок выборки хранения содержит третий конденсатор, первый — пятый резисторы, первый — шестой 50 транзисторы и первый и второй диоды, первый вывод первого резистора является входом блока и подключен к второму выходу видеоусилителя, второй его вывод является третьим входом и соединен с выходом пер- 55 вого ключа и анодом первого диода, первый вывод второго резистора является вторым входом блока и соединен с источником опорного напряжения, его второй вывод является четвертым входом, соединен с выходом второго ключа, анодом второго диода и базой третьего транзистора. базы первого и второго транзисторов соединены с коллектором второго транзистора и катодом второго диода, коллектор первого транзистора подключен к катоду первого диода, базе пятого транзистора и первому выводу третьего резистора, коллектор третьего транзистора соединен с источником питания, а эмиттер — с базой и коллектором четвертого транзистора, вторым выводом третьего резистора и первым выводом третьего конденсатора, коллектор пятого транзистора соединен с базой шестого транзистора непосредственно, а с источником питания — через четвертый резистор, эмиттер шестого транзистора соединен с вторым выводом третьего конденсатора непосредственно, а с землей— через пятый резистор, эмиттеры первого, второго, четвертого и пятого транзисторов соединены с землей, коллектор шестого транзистора является выходом блока и подключен к третьему, управляющему входу дифференциального видеоусилителя, Дифференциальный видеоусилитель содержит токовый фаэоинвертор, первый и второй преобразователи тока в напряжение, первый и второй входы токового фазоинвертора являются первым и вторым входами видеоусилителя и соединены соответственно с вторыми выводами первого и второго конденсаторов, вход первого и первый вход второго преобразователя тока в напряжение подключены к выходам токового фазоинвертора, второй вход второго преобразователя тока в напряжение является третьим, управляющим входом видеоусилителя и соединен с выходом дифференциального блока выборки — хранения, выходы первого и второго преобразователей тока в напряжение являются выходами видеоусилителя и соединены соответственно с входами синхроселектора и блока выборки-хранения.

Техническая сущность предлагаемого технического решения заключается в использовании переключаемых обратных связей для увеличения отношения постоянных времени разряда и заряда третьего конденсатора. Заряд последнего осуществляется через низкое выходное сопротивление эмиттерного повторителя, выполненного на шестом транзисторе, и низкое входное сопротивление третьего и четвертого транзисторов, кроме того наличие во время заряда общей отрицательной обратной связи, охватывающей второй преобразователь тока в напряжение видеоусилителя и дифференциальный блок выборки-хранения дополнительно в десятки раз сокращает постоянную

1793«),<. времени заряда. На этапе хранения заряда разрывается общая обратная связь, обесточиваются третий и четвертый транзисторы, в результате чего третий конденсатор оказывается BключеHH ûм в интегратор, образованный пятым и шестым транзисторами, что позволяет значительно увеличить постоянную времени разряда конденсатора.

Это позволяет при сокращении постоянной разряда увеличить точность "привязки" строчных импульсов к уровню опорного

10 напряжения. В результате эффективно подавляются помехи с частотами ниже частоты строчных импульсов, что, в конечном

15 счете, приводит к повышению помехоустойчивости и динамического диапазона.

Известные схемы выборки-хранения используют заряд-разряд интегратора при переключении лишь общей обратной связи (" Аналоговые и цифровые интегральные

20 схемы", под. ред. С. В. Якубовского. М.; Радио и связь, 1985 г., стр. 369 — 370). Получение достаточно больших отношений постоянных разряда и заряда в известных

25 устройствах возможно лишь при использовании полевых транзисторов, что ограничивает возможности построения таких устройств B составе интегральных микросхем, выполненных на биполярных транзисторах, тем более одной проводимости.

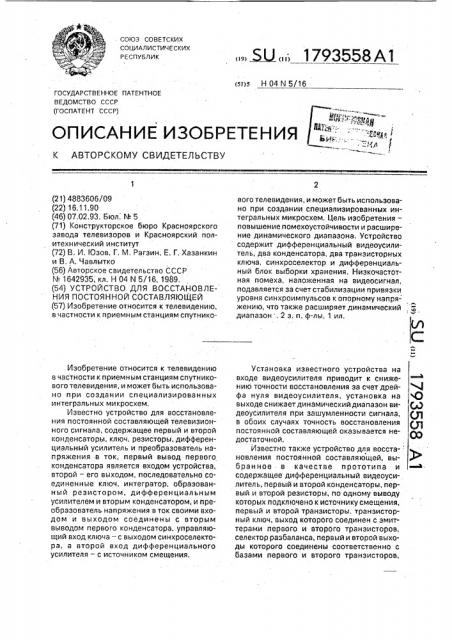

На чертеже изображена схема устройства, Устройство для восстановления постоянной составляющей содержит дифферен30 второй 3 конденсаторы первый 4 и второй 5 транзисторные ключи, синхроселектор 6 и дифференциальный блок 7 выборки хранения. Первый и второй сигнальные входы

40 дифференциального видеоусилителя 1 соединены соответственно через первый конденсатор 2 с источником сигнала (на схеме не показан), и через второй 3 — с землей, третий, управляющий вход подключен к вы45 ходу дифференциального блока 7. Вход синхроселектора 6 соединен с первым выходом дифференциального видеоусилителя 1, а

его выход — с управляющими входами первого и второго 5 транзисторных ключей, 50

Первый вход дифференциального блока 7 выборки-хранения подключен к второму выходу дифференциального видеоусилителя 1, второй — к источнику опорного напряжения (на схеме не показан), третий и четвертый к выходам первого 4 и второго 5 транзисторных ключей, Дифференциальный блок выборки-хранения содержит третий конденсатор 8, первый — пятый 9-13 резисторы, первый— шестой транзисторы 14- 19. первый 20 и вто55 циальный видеоусилитель 1, первый 2 и 35 рой 21 диоды. Первый вывод первого резистора 9 является входом блока 7 и подключен к второму вь.ходу видеоусилителя 1, второй его вывод является третьим входом и соединен с выходом первого ключа 4 и анодом первого диода 20, первый вывод второго резистора 10 является вторым входом блока 7 и соединен с источником опорного напряжения. его второй вывод является четвертым входом, соединен с выходом второго ключа 5, анодом второго диода 21 и базой третьего транзистора 16. базы первого 14 и второго 15 транзисторов соединены с коллектором второго транзистора 15 и катодом второго диода 21, коллектор первого транзистора 14 подключен к катоду первого диода 20, базе пятого транзистора 18 и первому выводу третьего резистора 11, коллектортретьего транзистора 16 соединен с источником питания, а эмиттер — с базой и коллектором четвертого транзистора 17, вторым выводом третьего резистора 11 и первым выводом третьего конденсатора 8, коллектор пятого транзистора 18 соединен с базой шестого транзистора 19 непосредственно. а с источником питания — через четвертый резистор 12, эмиттер шестого транзистора 19 соединен с вторым выводом третьего конденсатора 8 непосредственно, а с землей — через пятый резистор 13, эмиттеры первого 14, второго

15, четвертого 17 и пятого 18 транзисторов соединены с землей, коллектор шестого транзистора 19 является выходом блока 7 и подключен к третьему, управляющему входу дифференциального видеоусилителя 1, Дифференциальный видеоусилитель 1 содержит токовый фазоинвертор 22, первый

23 и второй 24 преобразователи тока в напряжение первый и второй входы токового фазоинвертора 22 являются первым и вторым входами видеоусилителя 1 и соединены соответственно с вторыми выводами первого 2 и второго 3 конденсаторов. вход первого 23 и первый вход второго 24 преобразователей тока в напря>кение подключены к выходам токового фазоинвертора 22, второй вход второго преобразователя

24 тока в напряжение является третьим, управляющим входом видеоусилителя 1 и соединен с выходом дифференциального блока

7 выборки-хранения, выходы первого и второго 24 преобразователей тока в напряжение являются выходами видеоусилителя и соединены соответственно с входами синхроселектора 6 и блока 7 выборки-хранения.

Работает устройство следующим образом.

Входной видеосигнал поступает на первый вход дифференциального видеоусили1793558 теля 1, а с его первого и второго выходов два усиленных противофазных сигнала поступают соответственно на входы синхроселектора 6 и дифференциального блока 7 выборки-хранения, Синхроселектор 6 во время действия синхроимпульсов формирует на своем выходе импульс отрицательной полярности, запирающий первый 4 и второй

5 ключи. На первый и второй, сигнальные входы дифференциального блока 7 выборки — хранения поступают соответственно видеосигнал с второго выхода дифференциального усилителя 1 и опорное напряжение.

При закрытых ключах 4 и 5. соответствует прохождению синхроимпульсов, эти напряжения сравниваются, разность усиливается и формируется ток, поступающий на третий, управляющий вход дифференциального видеоусилителя 1, изменяющий режим второго преобразователя 24 тока в напряжение, таким образом, чтобы свести разность входных напряжений дифференциального блока

7 выборки-хранения к нулю. Значение установившегося тока запоминается. После окончания синхроимпульса выходным напряжением синхроселектора 6 открываются первый 4 и второй 5 ключи, дифференциальный блок 7 выборки-хранения переходит в режим хранения и величина тока, поступающего на третий вход дифференциального видеоусилителя 1 остается практически неизменной вплоть до прихода следующего синхроимпульса. Далее процесс повторяется.

Во время действия синхроимпульсов первый 4 и второй 5 ключи закрыты, первый

20 и второй 21 диоды открыты, на базу пятого транзистора 18 через схему сравнения, образованную первым 9 и вторым 10 резисторами и токовым зеркалом, выполненным на первом 14 и втором 15 транзисторах, подается напряжение, которое усиливается пятым 18 и шестым 19 транзисторами, вклю- ченными с общими эмиттерами, и коллекторный ток четвертого транзистора, являющийся выходным током дифференциального блока 7 выборки-хранения, поступает на третий управляющий вход видеоусилителя 1, а с его выхода — íà первый вход блока 7 выборки-хранения, замыкая петлю обратной отрицательной связи. В момент равновесия, достигаемый к концу синхроимпульса, выходное напряжение дифференциального видеоусилителя 1 описывается приближенным выражением

Вг Uaa xx

Uevx=Uon+ — =—

Й1 Кобш где 0 1х — выходное напряжение видеоусилителя 1;

0оп — величина опорного напряжения;

R1, Иг — величины первого 9 и второго 10

5 резисторов;

Кобщ — ОбщЕЕ ПЕтЛЕВОЕ УСИЛЕНИЕ, раВНОЕ

Кобщ=

R3 В

10 В1+Йз

Ro

R5 здесь В, Rin — коэффициент усиления по току и входное сопротивление пятого транзистора 18;

15 Вз, R4, Вб — величины третьего 11, четвертого 12 и пятого 13 резисторов;

Ro — коэффициент преобразования второго преобразователя 24 тока в напряжение.

20 При типовых параметрах;

Й1=йг=йз=500 ОМ, R4=3,5 КОМ, об=200 ОМ, Ro=1 КОМ. В=30, Rin =500 ОМ

25 петлевое усиление близко к 350, примерно такой же величине равно подавление низкочастотных помех в видеосигнале, Эмиттерным током пятого транзистора

30 18 заряжается третий конденсатор 8. Собственная постоянная времени заряда

То=Со + + Rin/2

R4+ RIn

35 где Co — величина третьего конденсатора 8.

Rino — входные сопротивления третьего

16 и четвертого 17 транзисторов в схеме с общей базой.

40 С учетом общей отрицательной обратной связи постоянная времени заряда соКращаЕтСя В (1+Кобщ) раэ

Т„р=То/(1+Кобщ)=0,4+Со сек

По окончании действия синхроимпуль45 са выходным напряжением синхроселектора 6 открываются первый 4 и второй 5. ключи, потенциалы на анодах первого 20 и второго 21 диодов падают.до нуля, диоды 20, 21, а также первый 14, второй 15, третий 16

50 и четвертый 17 транзисторы запираются, размыкая петлю общей обратной связи и изолируя первый вывод третьего конденсатора 11 от земли. Выходной ток блока 7 выборки-хранения поддерживается почти постоянным за счет заряда, накопленного на третьем конденсаторе 11. Сам конденсатор оказывается включенным в схему интегратора, образованного каскадом с общим эмиттером на пятом транзисторе 18, эмит179. 1558

10 терным повторителем на шестом транзисторе 19. Постоянная времени разряда оказывается равной

Тразр=Со+ В + R< = 100000 + Со сек

Минимальная величина третьего конденсатора 8 определяется допустимым изменением уровня видеосигнала между синхроимпульсами 0 и длительностью стро- 10 ки Т«р

Tcllh о тр р и может составлять 0.6 мкф при допустимом изменении уровня D=-0,1, 15

При такой емкости динамическая погрешность сравнения напряжений во время действия синхроимпульсов пренебрежимо мала, и подавление низкочастотных помех определяется лишь статической погрешно- 20 стью сравнения напряжений во время действия синхроимпульсов.

Введение дополнительных элементов и связей позволяет, по сравнению с прототипом, значительно увеличить отношение по- 25 стоянных времени заряда и разряда

Формула изобретения

1, Устройство для восстановления постоянной составляющей, содержащее последовательно соединенные дифференциальный видеоусилитель, синхроселектор и транзисторный ключ, первый и второй конденсаторы, причем первый конденсатор включен между источником сигнала и первым входом дифференциального видеоусилителя, второй — между его вторым входом и "землей", о т л и ч а ю щ е е с я тем, что, с целью повышения помехоустойчивости и расширения динамического диапазона, введены второй транзисторный ключ, вход которого подключен к выходу синхроселектора, и дифференциальный блок выборки-хранения, первый и второй сигнальные входы которого подключены соответственно к второму выходу дифференциального видеоусилителя и источнику опорного напряжения, третий и четвертый управляющие входы — к выходам первого и второго транзисторных ключей, а выход соединен с третьим управляющим входом дифференциального видеоусилителя.

2, Устройство по и. 1, о т л и ч э ю ще ес я тем, что дифференциальный блок выборки хранения содержит третий конденсатор, нэкопительного конденсатора. Это обеспечивает при достаточно малых изменениях уровня видеосигнала за время между строчными импульсами обеспечить практически полное подавление динамической погрешности и, за счет глубокой общей, обратной связи уменьшение более чем в 350 рэз статической погрешности.

При наложении на видеосигнал низкочастотной помехи последняя эффективно подавляется зэ счет стабильной привязки уровня синхроимпульсов к опорному напряжению. Устранение помехи из выходной части видеоусилителя расширяет его динамический диапазон.

Отсутствие ключевых элементов на входе видеоусилителя практически полностью исключает прохождение коммутационных помех нэ фильтры, обычно стоящие нэ входе видеоусилителя.

Устройство выполнено нэ транзисторах одной проводимости, имеет минимальное число конденсаторов и сравнительно узкий диапазон используемых резисторов. Это позволяет выполнить его в составе твердотельной интегральной микросхемы, первый — пятый резисторы, первый — шестой транзисторы и первый и второй диоды, первый вывод первого резистора является входом блока и подключен к второму выходу видеоусилителя, второй его вывод является третьим входом и соединен с выходом первого ключа и анодом первого диода, первый вывод второго резистора является вторым входом блока и соединен с источником опорного напряжения, его второй вывод является четвертым входом, соединен с выходом второго ключа, анодом второго диода и базой третьего транзистора, базы первого и второго транзисторов соединены с коллектором второго транзистора и катодом второго диода, коллектор первого транзистора подключен к катоду первого диода, база пятого транзистора — к первому выводу третьего резистора, коллектор третьего транзистора соединен с источником питания, а эмиттер — с базой и коллектором четвертого транзистора, вторым выводом третьего резистора и первым выводом третьего конденсатора, коллектор пятого транзистора соединен с базой шестого транзистора непосредственно, э с источником питания — через четвертый резистор, эмиттер шестого транзистора соединен с вторым выводом третьего конденсатора не1793558

Составитель 8ЛОзов

Техред М.Моргентал

Корректор И,Шулла

Редактор С.Кулакова

Заказ 511 Тираж . Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раущская наб., 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101 посредственно, а с землей — через пятый резистор, эмиттеры первого, второго, четвертого и пятого транзисторов соединены с землей, коллектор шестого транзистора является выходом блока и подключен к третьему управляющему входу дифференциального видеоусилителя, 3. Устройство по и. 1, о т л и ч а ю щ е ес я тем, что дифференциальный видеоусилитель содержит токовый фазоинвертор, первый и второй преобразователи тока в напряжение, первый и второй входы токового фазоинвертора является первым и вторым входами видеоусилителя и соединейы соответственно с вторыми выводами первого и второго конденсаторов, вход первого и первый вход второго преобразователей тока в напряжение подключены к выходам токового фазоинвертора, второй вход второго преобразователя тока в напряжения я вляется третьим управляющим входом видеоусилителя и соединен с выходом дифференциального блока выборки-хранения, выходы первого и второго преобразователей тока в напряжение являются выходами видеоусилителя и соединены соответственно с входами синхроселектора и блока выборки-хранения.