Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

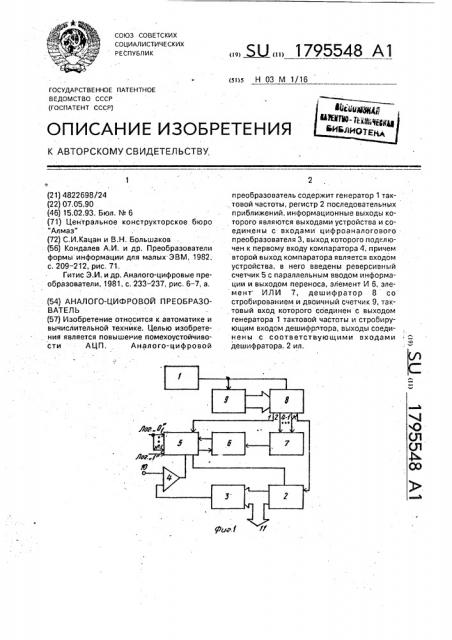

Изобретение относится к автоматике и вычислительной технике. Целью изобретения является повышение помехоустойчивостиАЦП . Аналого-цифровой преобразователь содержит генератор 1 тактовой частоты, регистр 2 последовательных приближений, информационные выходы которого являются выходами устройства и соедин.ены с входами цифроаналогового преобразователя 3, выход которого подключен к первому входу компаратора 4, причем второй выход компаратора является входом устройства, в него введены реверсивный счетчик 5 с параллельным вводом информации и выходом переноса, элемент И 6, элемент1 ИЛИ 7, дешифратор 8 со стробированием и двоичный счетчик 9, тактовый вход которого соединен с выходом генератора 1 тактовой частоты и стробирующим входом дешифратора, выходы соединены с соответствующими входами дешифратора. 2 ил. Г N. Ъ

союз советских

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)5 Н 03 M 1/16

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ, 1 (21) 4822698124 (22) 07.05.90 (46) 15.02.93. Бюл. N. 6 (71) Центральное конструкторское бюро

"Алмаз" (72) С,И.Кацан и B.H. Большаков (56) Кондалев А.И. и др. Преобразователи формы информации для малых ЭВМ, 1982, с. 209 — 212, рис. 71, Гитис 3.И. и др. Аналого-цифровые преобразователи, 1981, с. 233 — 237, рис, 6 — 7, а. (54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРА30ВАТЕЛ6 (57) Изобретение относится к. автоматике и вычислительной технике. Целью изобретения является повышение помехоустойчивости АЦП. Аналого-цифровой Ы 1795548 А1 преобразователь содержит генератор 1 так, товой частоты, регистр 2 последовательных приближений, информационные выходы которого являются выходами устройства и соединены с входами цифроаналоговогопреобразователя 3, выход которого подключен к первому входу компаратора 4, причем второй выход компаратора является входом устройства, в него введены реверсивный счетчик 5 с параллельным вводом информации и выходом переноса, элемент И 6. элемент ИЛИ 7, дешифратор 8 со стробированием и двоичный счетчик 9, тактовый вход которого соединен с выходом генератора 1 тактовой частоты и стробирующим входом дешифр тора, выходы соединены с соответствующими входами дешифратора, 2 ил.

1795548

Изобретение относится к автоматике и вычислительной технике, в частности к устройствам аналого-дискретного преобразования, Изобретение может быть использовано в цифровых вычислительных и измерительных устройствах, системах программного управления и автоматической обработки данных.

Целью изобретения является повышение помехоустойчивости.

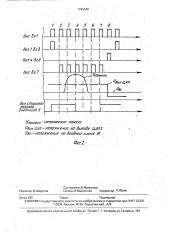

На фиг.1 представлена структурная схема устройства; на фиг,2 — временные диаграммы.

На фиг,1 генератор 1 тактовой. частоты, регистр 2 последовательных приближений, цифра-аналоговый преобразователь 3, компаратор 4, реверсивный счетчик 5 с параллельной записью информации и выходом переноса, элемент И 6,:элемент ИЛИ 7, дешифратор 8 со стробированием, двоичный счетчик 9, входная шина 10, выходная шина

11.

Коэффициент деления двоично о счетчика 9 выбирается следующим образом

N > — +2, 2r

Т где Т вЂ” период тактовой частоты генератора частоты 1; г — максимальная длительность помехи.

Устройство работает следующим образом

Импульсы тактовой частоты от генератора 1 тактовой частоты, приложенные к двоичному счетчику 9, образует на его выходе линейно нарастающий код. Этот код дешифратором 8 преобразуется в импульсы, стробированные импульсами тактовой частоты от генератора 1 тактовой частоты, последовательно появляющиеся на выходах дешифратора 8. Импульс с первого выхода дешифратора 8 записывается в старший разряд реверсивного счетчика 5 логическую

"1". Последующие импульсы со второго по

N-1-й через элемент ИЛИ 7 поступают на тактовый вход реверсивного счетчика 5. В зависимости от состояния выхода компаратора 4 счетчик работает или в режиме сложения (при лог, "1" на выходе компаратора

4) или в режиме вычитания (при лог. "0" на выходе компаратора 4), После прихода N-1го импульса с элемента ИЛИ 7 на выходе старшего разряда реверсивного счетчика 5 устанавливается то состояние компаратора

4. которое больше времени присутствовало на выходе компаратора за время действия импульсов со второго по N-1-й. К-й импульс с дешифратора 9 поступает на тактовый вход . регистра 2 последовательных прибли10 времени счета реверсивного счетчика 5, то она не может изменить значения старшего

"5 разряда реверсивного счетчика 5 после прохождения всех (со второго по N-й) импульсов на его тактовый вход с элемента ИЛИ 7, это означает, что наличие помехи в данном

50

45 жений, Регистр 2 последовательных приближений, учитывая значение информационного входа, на который поступает сигнал со старшего разряда реверсивного счетчика

5, переходит к следующему такту преобразования.

Таким образом, при наличии помехи на любом такте преобразования реверсивный счетчик кратковременно переходит в противоположный режим счета и затем опять возвращается в рабочий режим счета, так как длительность помехи меньше половины такте преобразования не изменило значение сигнала на информационном входе регистра 2 последовательных приближений в момент анализа входной информации регистром 2 последовательных приближений ине привело к ложному срабатыванию, Элемент И 6 необходим для исключения переполнения реверсивного счетчика 5 и появления на выходе его старшего разряда ложной информации (при полном заполнении счетчика сигнала лог."0" с выхода переноса запрещает поступление тактовых импульсов на тактовый вход реверсивного счетчика 5), Для обьяснения временной диаграммы приняты следующие приближения..

Для лучшего понимания работы устройства разберем его работу в одном такте преобразования на конкретном примере.

Предположим, что длительность помехи составляет не более 2,5 периодов тактовой частоты, тогда коэффициент деления счетчика 9 выбираем (исходя из формулы) равным 8.

Первым импульсом тактовой частоты в счетчик 5 записывается код 1000 ("1" — в старшем разряде).

Вторым импульсом информации в счетчике 5 увеличивается на единицу, так как помеха отсутствует, код в счетчике 1001.

Во время действия третьего, четвертого и пятого импульсов появляется помеха, которая переводит счетчик 5 в реверсивный режим, поэтому код в счетчике 5 становится

0110.

Во время действия шестого и седьмого импульсов помеха отсутствует, поэтому код в счетчике становится равным 1000, Единица в старшем разряде счетчика 5 к моменту действия последнего (восьмого) импульса показывает, что в течение такта преобразования амплитуда входного сигна1795548 ла большее время была меньше амплитуды с выхода ЦАП (т.е. длительность помехи была меньше половины времени счета счетчика 5). После восьмого импульса устройство переходит к анализу информации в следую- 5 щем такте преобразования регистра 2 последовательных приближений, Таким образом, из приведенной временной диаграммы видно, почему коэффи- 10 циент деления счетчика выбирается по формуле, приведенной ниже. Со вторым входом элемента И 6 соединен выход пере- носа реверсивного счетчика 5 для того, что 15

Формула изобретения

Аналого-цифровой преобразователь, содержащий генератор тактовой частоты, регистр последовательных приближений, информационные выходы которого являются выходной шиной и соединены с входами цифроаналогового преобразователя, выход которого подключен к первому Йходу KQMпаратора, второй вход которого является входной шиной, отличающийся тем, что, с целью повышения помехоустойчивости, в него введены реверсивный счетчик, элемент

И, элемент ИЛИ, дешифратор и двоичный счетчик, тактовый вход которого соединен с выходом генератора тактовой частоты и объединен со стробирующим входом дешифратора, выходы соединены с соответствующими информационными вхобы при отсутствии помехи счетчик 5 не переполнилсяя.

Использование изобретения позволит по сравнению с прототипом повысить помехоустойчивость аналого-цифрового преобразователя путем исключения ложной фиксации состояния компаратора регистром последовательных приближений, производить преобразование при наличии импульсных помех высокого уровня без потерь точности. Кроме того, обеспечивается лучшая совместимость аппаратуры и допускается большая удаленность абонентов комплекса, дами дешифратора, первый выход которого подключен к входам записи параллельной информации реверсивного счетчика, выходы с второго no N-1 соединены с входами элемента ИЛИ, à ¹A выход — с тактовым входом регистра последовательных приближений, информационный вход которого подключен к выходу старшего разряда реверсивного счетчика, вход направления счета которого соединен с выходом компаратора, параллельные входы — с первого по й-1 подключены к общей шине, М-й вход является шиной логической единицы, выход переноса подключен к первому входу, элемент И, выход которого соединен с тактовьн входом реверсивного счетчика, второй вхо, элемента И соединен с выходом элемен.:.э

ИЛИ.

1795548

88/х &f

Удо,хщ- напряжение лоухи

Йь/х И,Ап — 0/ЙДЯИРниЯ zu Revue ЩОЗ

Qy. — мЮояжжюг ьо 8ходной aruae 4

Редактор В.Федотов

Заказ 435 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035. Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарина, 101

Вых. сааршего ,Я7УОЯЙУ

evemvuvu Я

Составитель В,Махнанов

Техред М,Моргентал Корректор С.Юско