Формирователь переноса

Иллюстрации

Показать всеРеферат

COIO3 СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5!)5 G 06 F 7/50

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4945726/24 (22) 17.06,91 (46) 28.02.93. Бюл. М 8 (71} Государственный научно-исследовательский институт авиационных систем (72) В,Г.Курочкин (56) Авторское свидетельство СССР

М 1312567, кл. G 06 F 7/50, 1985.

Авторское свидетельство СССР

М 1702361, кл. G 06 F 7/50, 1990. (54) ФОРМИРОВАТЕЛЬ ПЕРЕНОСА (57) Изобретение относится к вычислительной технике и может быть использовано при построении арифметических цифровых устИзобретение относится к вычислительной технике и может быть использовано при построении арифметических цифровых устройств на КМДП-транзисторах, в частности многоразрядных параллельных сумматоров-вычислителей и схем сравнения.

Цель изобретения — упрощение конструкции формирователя переноса за счет увеличения регулярности его структуры.

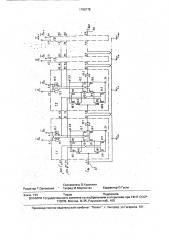

Электрическая функциональная схема заявляемого устройства представлена на чертеже.

На чертеже условно показаны младшие разряды заявляемого устройства, где каждый разряд 1 содержит входы 2 и 2 первого и второго операндов соответственно. вход переноса 4 и выход переноса 5, первый 6 и второй 7 входы управления, первый 8 и второй 9 выходы управления, элементы И-НЕ

10, ИЛИ-НЕ 11, первый-пятый МДП-тран. Ж„„17гМЛ78 А1 ройств на КМДП-транзисторах, в частности многоразрядных параллельных сумматоров-вычитателей и схем сравнения, -Цель изобретения — упрощение устройства, Формирователь переноса содержит в каждом разряде. входы первого и второго операндов, вход переноса, выход переноса, пер- . вый и второй входы управления, первый и второй выходы управления, элемент И-НЕ, элемент ИЛИ вЂ”.HF, пять МДП-транзисторов р-типа, пять МДП-транзисторов п-типа, эле, мент НЕ, шины питания и нулевого потейциала, соединенные между собой функционально. 1 ил., 1 табл, зисторы р-типа 12 — 16 соответственно, первый-пятый МДП-транзисторы п-типа 17-21 соответственно, элемент НЕ 22, шины 23 питания и 24 нулевого потенциала устройства, причем входы переноса младшей пары разрядов устройства соединены со входом

25 его начального переноса, выход переноса его старшего разряда образует выход 26 переноса устройства, первые и вторые входы управления каждого разряда устройства соединены соответственно с первым и вторым выходами управления соседнего младmего разряда с логическими "1" и "0" у самого младшего из них, Обозначим прямые значения)-го разряда первого и второго входных операндов устройства А и В1 соответственно, где ) = (0,1..., N — 1), N — разрядность входных операндов; прямое значение сигнала переноса, формируемого соответствующим разрядом

1798778 устройства как С, прямое значение началь. ного переноса устройства как Св> и прямое значение его выходного переноса как Сецх.

Формирователь переноса работает следующим образом. 5

Будем считать, что уровень "логической

I ("1") соответствует напряжению шины 23 питания формирователя, а уровень "логическбго 0" .("О") соответствует напряжению шины 24 нулевого потенциала формирователя.

Для удобства выделим следующие два режима работы каждого разряда формирователя: — режим генерации собственного переноса; — режим передачи сквозного переноса.

Разряд формирователя. переноса работает в режиме генерации собственного переноса при совпадении сигналов на его 20 входах 2 и 3 разрядов операндов; при этом на его выходах управления 8 и 9 формируются сигналы "00" или "11" и, в случае комбинации "00", открыты первый 12 и второй

13 МДП-транзисторы р-типа, закрыты пер- 25 вый 17 и второй 18 МДП-транзисторы и-типа, на входе элемента HE 22 устанавливается уровень "1", а на выходе 5

- переноса данного разряда формирователя — "0"; в случае комбинации "11", открыты О первый 17 и второй 18 МДП-транзисторы п-типа, закрыты первый 12 и второй 13

МДП-транзисторы р-типа, на входе элемента НЕ 22 устанавливается уровень "О", а на выхоце 5 переноса данного разряда форми- Э5 рователя — "1".

Разряд формирователя работает в режиме передачи GKaoSHoro переноса при несовпадении сигналов на его входах 2 и 3 разрядов операндов; при этом на его пер- 40 вом 8 и втором 9 выходах управления формируются соответственно "1" и "0", первый

12 и МДП-транзистор р-типа и второй 18

МДГИранзистор и-типа закрыты, первый 17 .

МДП-транзистор и-типа и второй 13 МДП- 45 транзистор р-типа открь(ты, и состояние сигнала на входе элемента НЕ 22 определяется уровнями сигналов на первом 6 и втором 7 входах управления данного разряда формирователя; а также уровнем сигнала на 50 его входе 4 переноса.

Так, если на входах 6 и 7 управления данного разряда формирователя установлена комбинация "ОО", соответствующая режиму генерации собственного переноса 55 соседнего младшего разряда формирователя, у рассматриваемого разряда формирователя открыты четвертый 15 и пятый 16

МДП-транзисторы р -типа, закрыты четвертый 20 и пятый 21 МДП-транзисторы п-типа, на входе элементе HE 22 устанавливается уровень "1". а на выходе 5 переноса данного разряда формирователя — "О". Если на входах 6 и 7 управления данного разряда формирователя установлена комбинация "11", также соответствующая режиму генерации собственного переноса соседнего младшего разряда формирователя, у рассматриваемого разряда формирователя открыты четвертый 20 и пятый 21 МДП-транзисторы п-типа, закрыты четвертый 15 и пятый 16

МДП-транзисторы р-типа, на входе элемента HE 22 устанавливается уровень "0", а на выходе 5 переноса данного разряда формирователя — "1", Если же на первом 6 и втором

7 входах управления данного разряда формирователя установлены состояния "1" и

"0", соответствующие режиму передачи сквозного переноса соседнего младшего разряда формирователя, у рассматриваемого разряда формирователя четвертый 15

МДП-транзистор р-типа и пятый 21 МДПтранзистор и-типа закрыты, пятый 16 МДПтранзистор р-типа и четвертый 20

МДП-транзистор и-типа открыты, на вход элемента HE 22 через третьи МДП-транзисторы 14 р-типа и 19 и-типа передается двоично-инверсное значение сигнала со входа

4 переноса, и на выходе 5 переноса данного разряда формирователя устанавливается уровень, соответствующий сигналу на его. входе 4 переноса; сочетание состояний "0" и "1" на первом 6 и втором 7 входах управления разрядов формирователя запрещено.

Для обеспечения правильности функционирования формирователя у самого младшего его разряда первый 6 и второй 7 входы управления соединены соответственно с "1" и "О", а входы 4 переноса у самой младшей пары его разрядов соединены со входом 25 начального переноса;

Пусть на вход 25 начального переноса формирователя подается прямое значение сигнала входного переноса. Тогда в режиме передачи сквозного переноса на выходах 5 его разрядов устанавливаются прямые значения поразрядных переносов, и в режиме генерации собственного переноса "О" на них соответствует комбинации "ОО" прямых значений сигналов входных операндов, а

"1" — комбинации "11" этих сигналов и т,д.

В таблице отображены возможные состояния на выходах 8 и 9 управления разрядов формирователя, из которой следует, что они могут быть описаны как:

F(8) = A1 V B - A * B, F(g) = A, * В = А1 Ч В .

Из изложенного видно, что все разряды входных операндов подаются на эаявляе1798778 мое устройство в одной фазе их двоичного представления, и.все сигналы поразрядного переноса формируются заявляемым устройством также в одной фазе их двоичного представления, все разряды заявляемого устройства имеют один и тот же функциональный состав, а входы управления каждого из них соединены напрямую с соответствующими выходами управления соседнего младшего разряда.

Таким образом, по сравнению с прототипом, заявляемое устройство обеспечивает упрощение конструкции формирователя переноса за счет увеличения регулярности его структуры и упрощает его применение в арифметических устройствах за счет одинакового поразрядного двоичного представления его входных операндов и выхода переноса, Формула изобретения

Формирователь переноса, каждый разряд которого содержит элемент И-НЕ, элемент ИЛИ вЂ” HE,. первый, второй, третий, четвертый и пятый МДП-транзисторы и-типа и первый, второй, третий, четвертый и пятый МДП-транзисторы р-типа, причем в каждом разряде выход элемента И-НЕ соединен.с аатворами первых МДП-транзисторов и-и р-типа, выход элемента ИЛИ-НЕ соединен с затворами вторых МДП-транзисторов п- и р-типа, затворы третьих МДПтранзисторов и-и р-тийа соединены с входом переноса данного разряда формирователя, затворы четвертых МДП-транзисторов и-и р-типа соединены с первым входом управления данного разряда формирователя, затворы пятых МДП-транзисторов и- и р-типа соединены с вторым входом управления данного разряда формирователя, истоки первого, четвертого и пятого

МДП-транзисторов р-типа соединены с шиной питания формирователя, истоки второго, четвертого и пятого МДП-транзисторов и-типа соединены с шиной нулевого потенциала формирователя, исток третьего МДПтранзистора р-типа соединен со стоком пятого МДП-транзистора р-типа, исток третьего МДП-транзистора и-типа соединен со стоком четвертого МДП-транзистора итипа, исток второго МДП-транзистора р-типа соединен со стоками третьего и четвертого МДП-транзисторов р-типа, исток первого МДП-транзистора и-типа соединен со стоками третьего и пятого МДП-транзисторов п-типа, стоки первых и вторых МДП5

10 транзисторов и-и р-типа соединены между собой, выходы элементов И вЂ” НЕ, ИЛИ-HE образуют соответственно первый и второй выходы управления данного разряда формирователя, а первый и второй входы каж15 дого из этих элементов соединены с соответствующим разрядом входов первого и второго операндов формирователя, выход переноса каждого четного разряда формирователя соединен с входом переноса следующего старшегО четного разряда

20 формирователя, выход переноса каждого

25 нечетного разряда формирователя соеди.нен с входом переноса следующего старшего нечетного разряда формирователя, входы переноса младшей пары разрядов формирователя соединены с входом начального мирователя соединены соответственно с шинами логической единицы и логического нуля, о тл и ча ю щ ий с я тем, что, с целью

35 упрощения, каждый разряд формирователя дополнительно содержит элемент НЕ, вход которого соединен со стоками первых и вторых МДП-транзисторов и-и р-типа, а выход элемента Н Е образует выход переноса дан40 ного разряда формирователя, первый и второй выходы управления каждого разряда формирователя соединены соответственно с первым и вторым входами управления смежного старшего разряда.

30 переноса формирователя, первый и второй входы управления младшего разряда фор1798778 | «? Д

° ° !

ltE

OJ ° с

Ф а

Составитель В.Курочкин

Редактор Т.Орловская Техред М,Моргентал Корректор О.Гyсти

Заказ 772 Тираж Подписное

BHMMOM Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", r. Ужгород. ул.Гагарина, 101