Аналоговый коммутатор

Иллюстрации

Показать всеРеферат

Изобретение относится к радиоэлектронике и может быть использовано в аналоговых и зналого-цифровых системах в качестве аналоговых коммутаторов и ключей, а также в устройствах выборки и хранения информации. Технической задачей, решаемой изобретением, является увеличение быстродействия при работе на последующие каскады со значительной емкости нагрузкой . Аналоговый коммутатор содержит блок управления, выполненный на двух транзисторах дифференциального каскада, источник тока, три змиттерных повторителя, построенных на транзисторах , два диода, два резистора, элемент смещения напряжений, два источника питания . 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)л Н 03 К 17/60

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4883895/21 (22) 16.11.90 (46) 28.02.93. Бюл. M 8 (71) Центральное межотраслевое конструкторско-технологическое бюро робототехники с опытным производством Института физики АН Латвии (72) В.В.Мата вкин (56) Авторское свидетельство СССР

N 508930, кл. Н 03 К 17/04, 17/60, 1976.

Авторское свидетельство СССР

М 1660162, кл. Н 03 К 17/04, 1990, (54) АНАЛОГОВ6! Й КОММУТАТОР (57) Изобретение относится к радиоэлектронике и может быть использовано в аналогоИзобретение относится к радиоэлектронике и может быть использовано s аналоговой и аналого-цифровой технике, в том числе в устройствах выборки и хранения информации.

Целью предлагаемого устройства является увеличение быстродействия схемы аналогового коммутатора за счет применения транзистора другого типа проводимости на выходесхемы, который. включается в качестве дополнительного эмиттерного повторителя и обеспечивает тем самым улучшение быстродействия при увеличенных емкостных нагрузках.

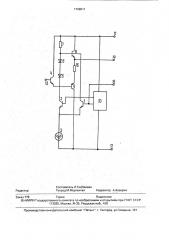

Предложенное устройство аналогового коммутатора представлено на чертеже.

Схема аналогового коммутатора, построенная на биполярных транзисторах, содержит схему управления на дифференциальном каскаде, выполнен ггую на первом 1, втором 2 транзисторах с источником тока 3 в цепи эмиттером этих транзисторов, первый эмиттерный повторитель

SU 1798911 А1 вых и аналого-цифровых системах в качестве аналогoBblx коммутаторов и ключей, а также в устройствах выборки и хранения информации, Техническои задачей, решаемой изобретением, является увеличение быстродействия при работе на последующие каскады со значительной емкости нагрузкой. Аналоговый коммутатор содержит блок управления, выполненный на двух транзисторах дифференциального каскада, источник тока, три змиттерных повторителя, построенных на транзисторах, два диода, два резйстора, элемент смещения напряжений, двэ источника питания. 1 ил, напряжения, построенный на третьем транзисторе 4, первом 5 и втором 6 диодах, одном резисторе 7, источником тока которого является транзистор 2, работающий в ключевом режиме, второй и третий змиттерные повторители, выполненные на четвертом 8 и пятом 9 транзисторах, причем пятый транзистор — другой проводимости, и схему смЕщения напряжений 10 цепей без транзисторов дифференциального каскада.

В качестве источников питания мохкет использоваться первый 11 и второй 12 источ-. кики питания, или один источник питания 11, В этом случае клемма, которая соединялась со вторым источником 12, подключается к общей шине. Входом схемы аналогового коммутатора является вывод 13, выходом вывод 14, а входом для подачи импульса сигнала управления — вйвод 15. В эмиттернуlo цепь транзистора 9 |ожет подключаться второй резистор 16.

Устройство работает следующим образом. При действии на выводе 15 нэпряже1798911 ния верхнего уровня импульса управления или его отсутствия ток источника 3 протекает через транзистор 1. Транзистор 2 при этом является закрытым. Протекание коллекторного тока транзистора 1 через резистор 7 вызовет падение напряжения на нем достаточное для запирания эмиттерного перехода транзистора 8 и диодов 5, 6, которые теоретически при отсутствии этого запирающего потенциала могли бы работать на токах утечки и токах обратно смещенных переходов транзисторов 2,9, Обесточивание первого эмиттерного повторителя из-за отсутствия тока в транзисторе 2 приводит также к закрытию транзисторов 4 и 9, переходу их в область отсечки, В этом случае сопротивление аналогового коммутатора как по входу, так и по выходу будет равно сопротивлению закрытых, обратно-смещенных переходов биполярных транзисторов.

При подаче на вход 15 напряжения нижнего уровня импульса сигнала управления произойдет закрывание эмиттерного перехода транзистора 1 и весь ток источника 3 пойдет через транзистор 2, Это приведет к открытию диодов 5, 6 и открытию транзисторов 4, 8, 9, то есть смещению в прямом направлении эмиттерных переходов этих транзисторов. При этом сопротивление схемы коммутатора по входу и выходу будет определяться соответствующими сопротивлениями эмиттерных повторителей (транзисторы 4, 8, 9). Включение в эмиттерную цепь транзистора 9 второго резистора

16 позволяет стабилизировать ток в начальном состоянии, протекающий через транзисторы 8 и 9 (сквозной ток).

Высокое быстродействие схемы коммутатор при увеличенной емкостной нагрузке определяется использованием на выходе схемы эмиттерных повторителей, выполненных на комплементарных транзисторах, Это позволяет увеличить быстродействие по сравнению с прототипом, у которого формирование отрицательного перепада напряжения идет со скоростью нарастания выходного напряжения. равного отношению тока источника 3 к величине емкости нагрузки.

Использование предлагаемого изобретения позволит значительно улучшить характеристики аналогового коммутатора и

1О прежде всего его быстродействие.

Формула изобретения

Аналоговый коммутатор, содержащий блок управления, выполненный в виде дифференциального каскада с источником тока в цепи эмиттером первого и второго транзисторов одного типа проводимости, два эмиттерных повторителя, выполненных на третьем и четвертом транзисторах того же типа проводимости, причем эмиттер треть2О его транзистора соединен с коллектором второго транзистора и катодом первого диода, анод которого соединен с катодом второго диода; а база четвертого транзистора соединена с анодом второго диода и первым выводом первого резистора, а также коллектором первого транзистора, второй вывод

nepsoro резистора подключен к.коллекторам третьего, четвертого транзисторов и клемме первого источника питания, а также элемент смещения напряжений, выходы которого подключены к базам первого и второго транзисторов дифференциального каскада, отличающийся тем, что, с целью увеличения быстродействия, введен

35 третий эмиттерный повторитель., выполненный на пятом транзисторе другого типа проводимости, причем база - данного транзистора соединена с коллектором второго транзистора, эмиттер пятого транзи40 стора подключен через второй резистор к эмиттеру четвертого транзистора и выходной шине, коллектор пятого транзистора соединен с клеммой второго источника питания.

1798911

Составитель Л.Скобелева

Техред M.Ìîðãåÿòàë Корректор А,Козориз

Редактор

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

Заказ 779 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35. Раушская наб., 4/5