Измеритель разности фаз

Иллюстрации

Показать всеРеферат

Изобретение относится к радиоизмерительной технике и может быть использовано для построения цифровых фазометров и измерителей фазовой задержки и группового времени запаздывания радиоустройств. Сущность изобретения: измеритель содержит двухканальный преобразователь разности фаз в интервалы времени и цифровой код по схеме с перекрытием и дополнительным опорным каналом для определения знака измеряемой разности фаз (фазовой задержки), включающий усилители-формирователи 1,2с элементами 3, 4 привязки, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ. 7,8,элементы И 10, 11, измерительные счетчики 13, 14 с информационными регистрами 16, 17, времязадающий счетчик 19 и счетчик 22 числа периодов с подключенными к ним управляющими 20(23) и информационными 21(24) регистрами, элемент ИЛИ 25, D-триггер 26, RS-триггер 27, генератор 28 счетных импульсов , а также микропроцессорный блок 30, который через общую шину 29 соединен с блоком 31 отображения информации, пультом 32 управления и другими программно управляемыми элементами устройства. Для повышения помехоустойчивости и расширения динамического диапазона в опорный канал измерителя включен блок 5 фильтрации ложных нулей, элемент 6 привязки и последовательно соединенные элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 9, И 12, измерительный счетчик 15 и информационный регистр 18. 4 ил. (Л С

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 G 01 R 25/00

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4904826/21 (22) 05.12.90 (46) 07.03.93. Бюл. ¹ 9 (71) Красноярский политехнический институт (72) А,C,Ãëèí÷eíêo и В.В.Моисеенко (56) Авторское свидетельство СССР

N. 1155957, кл. G 01 R 25/00, 1985

Авторское свидетельство СССР

N 1620986, кл. G 04 F 10/06, 1989. (54) ИЗМЕРИТЕЛЬ РАЗНОСТИ ФАЗ (57) Изобретение относится к радиоизмерительной технике и может быть использовано для построения цифровых фазометров и измерителей фазовой задержки и группового времени запаздывания радиоустройств.

Сущность изобретения; измеритель содержитдвухканальный преобразователь разности фаз в интервалы времени и цифровой код по схеме с перекрытие л и дополнительным опорным каналом для определения знака измеряемой разности фаз (фазовой

„„. Ж„„1800382 А1 задержки), включающий усилители-формирователи 1, 2 с элементами 3, 4 привязки„ элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 7,8,элементы И 10, 11, измерительные счетчики 13, 14 с информационными регистрами 16, 17, времязадающий счетчик 19 и счетчик 22 числа периодов с подключенными к ним управляющими 20(23) и информационными 21(24) регистрами, элемент ИЛИ 25, D-триггер 26, RS-триггер 27, генератор 28 счетных импульсов, а также микропроцессорный блок

30, который через общую шину 29 соединен с блоком 31 отображения информации, пультом 32 управления и другими программно управляемыми элементами устройства.

Для повышения помехоустойчивости и расширения динамического диапазона в опорный канал измерителя включен блок 5 фильтрации ложных нулей, элемент 6 привязки и последовательно соединенные элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 9, И 12, измерительный счетчик 15 и информационный регистр 18. 4 ил.

1800382

55

Изобретение относится к радиоизмерительной технике и может быть использовано для построения цифровых фазометров и измерителей группового времени запаздывания.

Цель изобретения — повышение помехоустойчивости измерителя и расширение его динамического диапазона.

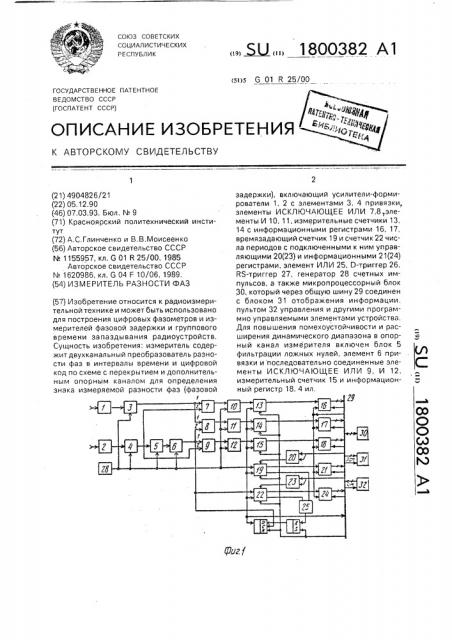

Структурная схема устройства приведена на фиг.1; на фиг.2 — блок-схема алгоритма обработки; на фиг.3 и 4 — структурная схема и диаграммы работы блока фильтрации ложных нулей, Устройство (фиг,1) содержит первый 1 и второй 2 усилители-формирователи с подключенными к ним первым 3 и вторым 4 элементами привязки, блок 5 фильтрации ложных нулей с подключенным к нему третьим элементов 6 привязки, первый 7, второй 8 и третий 9 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, которые входами соединены соответственно с выходами элементов 3 и 4, 3 и 6, 4 и 6 привязки, первый 10, второй 11 и третий 12 элементы И, соединенные первыми входами с выходами соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 7, 8, 9, первый 13, второй 14 и третий 15 измерительные счетчики, соединенные с выходами соответствующих элементов И 10, 11, 12, первый 16, второй 17 и пятый 18 информационные регистры, соединенные с выходами соответствующих измерительных счетчиков 13, 14 и 15, времязадающий счетчик 19 с подключенными к нему первым управляющим 20 и третьим информационным 21 регистрами, счетчик 22 числа периодов с подключенным к нему вторым управляющим 23 и четвертым 24 информационным регистрами, элемент ИЛИ 25, соединенный с времязадающим счетчиком 19 и счетчиком 22 числа периодов, соединенные между собой 0-триггер 26 и RS-триггер

27, который соединен с выходом элемента

ИЛИ 25 и совместно с D-триггером 26 — с входом пуска устройства, к которому подключены также входы начальной установки всех счетчиков 13, 15, 19, 22, входы разрешения счета которых соединены с выходом

D-триггера 26, соединенного С-входом с выходом третьего элемента 6 привязки, к которому подключены также счетный вход счетчика 22 числа периодов, генератор 28 счетных импульсов, соединенный с элементами 3, 4, 6 привязки, блоком 5 фильтрации ложных нулей, вторыми входами элементов

И 10„12 и счетным входом времязадающего счетчика 19, общую шину 29, через которую микропроцессорный блок 30 сопрягается с блоком 31 отображения информации и пультом 32 управления, с информационными

16..18, 21, 24 и управляющими 20, 23 регистрами, а также выходом D-триггера 26 и входом пуска устройства.

Блок 5 фильтрации ложных нулей (фиг.3) содержит инвертор 33, первый 34 и второй

35 счетные триггеры, первый 36 и второй 37 реверсивные счетчики, RS-триггер 38, первый 39 и второй 40 элементы И с инверсией.

При этом сигнальный вход блока соединен с входом инвертора 33, К-входом счетного триггера 34, входом направления счета 0/D реверсивного счетчика 37 и первым входом элемента И 40, Выход инвертора 33 соединен с R-входом счетного триггера 35, входом направления счета U/D реверсивного счетчика 36 и первым входом элемента И 39.

Тактовый вход блока соединен со счетными входами счетных триггеров 34, 35 и реверсивных счетчиков 36, 37, которые выходами соединены соответственно с R-входом и Sвходом RS-триггера 38. Входы счетных триггеров 34, 35 подключены к первым входам разрешения счета V> соответствующего реверсивного счетчика 36, 37, которые вторыми входами разрешения счета Vz соединены с выходами соответствующих элементов И

39, 40, подключенных вторыми входами соответственно к инверсному и прямому выходам RS-триггера 38, прямой выход которого является выходом блока.

Работает устройство следующим образом. Гармонические сигналы измерительного и опорного каналов поступают на входы соответственно первого 1 и второго 2 усилителей-формирователей, где преобразуются в последовательности прямоугольных импульсов с фронтами, привязанными к моментам переходов этих сигналов через нулевой уровень, С помощью элементов 3, 4 привязки фронты Прямоугольных импульсов синхронизируются квантующей последовательностью от генератора 28 счетных импульсов, Опорный сигнал с выхода второго элемента 4 привязки поступает на блок 5 фильтрации ложных нулей, который формирует второй опорный сигнал, задержанный относительного первого на время г сл . примерно равное четверти периода сигнала, а также обеспечивает исключение ложных нулей в опорном сигнале, вызываемых входнымии собственными широкополосными шумами. Этот сигнал также привязывается к квантующей последовательности третьим элементом 6 привязки. Функции элементов 3, 4, 6 привязки могут выполнять, например, 0-триггеры, Опорные сигналы с выходов элементов 4, 6 привязки поступают на входы третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 9 и вторые входы соответственно первого 7 и второго 8 элементов ИСКЛ ЮЧА1800382

ЮЩЕЕ ИЛИ, соединенных первыми входами с выходом первого элемента,3 привязки измерительного канала, Элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 7,8 преобразуют фазовые сдвиги p >, p гизмерительного сигнала 0 относительно первого и второго опорных сигналов Uo<, Uoz, в интервалы времени . На выходе третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 9 формируются интервалы времени 3, равные временному сдвигу т д, вносимому блоком 5 фильтрации ложных нулей.

Далее интервалы времени r 1, t z, r з в элементах И 10, 11, 12 заполняются счетными импульсами с периодом to (с частотой

fyð = 1/to), количество которых регистрируется измерительными счетчиками 13, 14, 15 и фиксируется в информационных регистрах 16, 17, 18. Начальная установка (обнуление) этих счетчиков осуществляется сигналом пуска устройства с микропроцессорного блока 30, которым также устанавливаются в единичное состояние RS-триггер

27 и в нулевое D-триггер 26, запрещая тем самым работу всех счетчиков. Предварительно микропроцессорным блоком 30 производится запись кодов времени измерения или числа периодов усреднения сигнала соответственно в первый 20 или второй 23 управляющий регистр.

С приходом первого импульса второго опорного сигнала с выхода третьего элемента привязки на С-вход D-триггера 26 последний переключается в единицу и разрешает счет всем счетчикам 13...15, 19, 22, По истечении заданного времени измерения или числа усредняемых периодов сигнала импульсом переноса с выхода времязадающего счетчика 19 или счетчика 22 числа периодов, прошедшим через элемент ИЛИ

25, устанавливается в ноль RS-триггер 27 и по ближайшему импульсу опорного сигнала с выхода третьего элемента 6 привязки Отриггер 26 переходит в нулевое состояние, запрещая счет всем счетчикам 13...15, 19, 22. Одновременно выходным сигналом "Готов" D-триггер 26 уведомляет о завершении измерительного цикла микропроцессорный блок 30, который затем управляющим сигналом "Запись" фиксирует выходные коды всех счетчиков 13...15, 19, 22 в соответствующих информационных регистрах 16, 18, 21, 24 и далее считывают их в собственную оперативную память. После этого микропроцессорный блок производит очередной запуск устройства и приступает к обработке полученной измерительной информации.

Обработка заключается в определении фазового сдвига и фазовой задержки изме5

55 рительного сигнала относительно опорного с учетом неоднозначной зависимости измеренного значения сдвига фаз и фазовой задержки от заданных значений в пределах

0...360 и О...Т, где Т вЂ” период сигнала, которая свойственна преобразователю фаза— интервалы времени на основе логических элементов ИСКЛЮЧАЮЩЕЕ ИЛИ. Обработка осуществляется на основе суммарных кодов измерительных счетчиков 13, 14, 15

N-,-,, N Ä., N,, суммарного кода времязадающего счетчика 19 NT,. и кода и счетчика 22 числа периодов. При этом в качестве отсчетного принимается тот из кодов N;,, N; которому соответствует фазовый сдвиг

Р р1, р2 измерительного сигнала относительно основного и задержанного опорных сигналов, более близкий к 90, или фазовая задержка, более близкая к Т/4. B случае использования кода N,.îñóùåcòâëÿåòcÿ его коррекция кодом N,,-, соответствующим взаимной задержке ойорных сигналов. Алгоритм обработки измерительной информации приведен на фиг.2.

При понижении частоты и/или уровня сигнала на входах измерителя за счет внешних и внутренних широкополосных шумов в выходных сигналах усилителей-формирователей 1, 2 и соответственно элементов 3, 4 привязки возникают ложные нули. Наличие ложных нулей в измерительном сигнале не влияет на работоспособность преобразователей на элементах ИСКЛЮЧАЮЩЕЕ ИЛИ вследствие их высокой помехоустойчивости. Присутствие ложных нулей в опорном сигнале, по которому формируется дополнительный задержанный опорный сигнал и осуществляется счет числа усредняемых периодов сигнала, без принятия специальных мер, как это имеет место, например, в прототипе, приводит к сбою соответствующих элементов и неработоспособности измерителя на низких частотах и малых уровнях сигнала на опорном входе, Повышение помехоустойчивости измерителя по опорному входу достигается путем использования для формирования задержанного опорного сигнала специального блока 5 фильтрации ложных нулей, который обеспечивает одновременно автоматическую задержку сигнала на время, равное примерно четверти периода сигнала, независимо от его частоты и эффективное подавление ложных нулей:

В одном из вариантов реализации блока 5 (фиг.3) счетные триггеры 34, 35 во время действия одной из полуволн ограниченного сигнала опорного канала (прямого U2 или инверсного

U2 с выхода инвертора 33) производят деление на два тактовой частоты

1800382

=2f„. Их выходы управляют входами разрешения счета Ч реверсивных счетчиков 36, 37, так что в режиме суммирования они ведут счет импульсов с частотой 2f<>, а в режиме вычитания — с частотой 1кв. В моменты достижения нулевых выходных кодов в режиме суммирования переключается RSтриггер 38, при этом на выходах элементов

И 39, 40 формируются уровни, запрещающие по входам Vz счет реверсивных счетчиков 36, 37 на суммирование до начала следующей полуволны сигнала. В результате на прямом выходе RS-триггера 38 получается меандр, сдвинутый во времени примерно на четверть периода относительно входного сигнала. Исключение ложных нулей достигается за счет цифрового интегрирования полуволн сигнала в реверсивных счетчиках 36, 37. Работу блока иллюстрируют временные диаграммы фиг,4, Блок 5 фильтрации ложных нулей может быть выполнен также, в соответствии с авт. св. СССР N. 789855, 1980, при этом тактовым входом блока является вход распределителя импульсов.

Все узлы заявляемого устройства реализуются на типовых интегральных схемах.

Так, составляющие наибольший объем аппаратной части измерителя счетчика 13..15, 19, 22, управляющие 20, 23 и информационные 16.„18, 21, 24 регистры реализуются на двух БИС программируемого таймера

К580ВИ53, включающего в себя также буферные схемы для сопряжения с общей шиной 29, Микропроцессорный блок 30 реализуется по типовой структуре на серийных МПК БИС. Функции этого блока, а также блока 31 отображения информации и пульта 32 управления может выполнять универсальная микроЭВМ. В качестве реверсивных счетчиков 36, 37 блока 5 фильтрации ложных нулей можно использовать микросхемы К531ИЕ17. Следует отметить, что реализация заявляемого измерителя является более простой, чем известных триггерных фазоизмерителей.

Как показано в книге Цифровые методы измерения сдвига фаз, Новосибирск, Наука, 1979, с, 91 — 111, ложные нули возникают при значении параметра m = gF/fm< 2,5, где q =

=Um/ o uj — отношение амплитуды сигналы

Um к среднеквадратическому значению шума аш; F — частота сигнала; fm — среднеквадратическая частота шума, определяемая шумовой полосой усилителяформирователя. Задаваясь отношением

F/fLu = 10, найдем q = 2,5 * 10, При оы "40 мкВ это соответствует U < = М,Значения q

= 2,5* 10 и Ощипан = 1 в определяют поме4

55 хоустойчивость и динамический диапазо прототипа по опорному входу. Указанные выше известные блоки фильтрации ложны> нулей, используемые в заявляемом устрой стве, характеризуются помехоустойчиво стью q = (5...10) и при о ш = 40 мкЕ обеспечивают U> = (200...400) мкВ.

Таким образом, благодаря введению новых элементов и связей обеспечивается повышение помехоустойчивости измерителя и расширение его динамического диапазона по опорному входу на три и более порядка при высокой помехоустойчивости по измерительному входу. В результате данное устройство может быть использовано как универсальный измеритель разности фаз, превосходящий по большинству параметров известные триггерные измерители.

Формула изобретения

Измеритель разности фаз, содержащий первый и второй усилители-формирователи, входы которых являются входами соответственно измерительного и опорного каналов устройства, соединенные с ними первый и второй элементы привязки, две цепочки из первых и вторых последовательно соединенных элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, элемента И, измерительного счетчика и информационного регистра, а также генератор счетных импульсов, элемент ИЛИ, RS-триггер, D-триггер, времязадающий счетчик с подключенными к входу предустановки первым управляющим регистром и к выходу— третьим информационным регистром, счетчик числа периодов с подключенным к входу предустановки вторым управляющим регистром и к выходу — четвертым информационным регистром, микропроцессорный блок, который через общую шину соединен с блоком отображения информации и пультом управления, а также с входами записи, чтения и выходами всех информационных регистров, с выходом О-триггера, с информационными входами и входами записи управляющих регистров и S-входом RSтриггера, являющимся входом пуска устройства, с которым соединены также R-вход

D-триггера и входы начальной установки всех счетчиков, которые входами разрешения счета подключены к выходу D-триггера, который D-входом соединен с выходом RSтриггера, выход элемента ИЛИ соединен с

R-входом RC-триггера, а его входы — с выходами переноса соответственно счетчика числа периодов и времязадающего счетчика, выход первого элемента привязки соединен с первыми входами первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выход второго элемента привязки соединен с вто1800382

10 рым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход генератора счетных импульсов соединен с синхровходами обоих элементов привязки, вторыми входами элементов И и счетным входом времязадающего счетчика, отличающийся тем, что, с целью повышения помехоустойчивости и расширения динамического диапазона, в него введены последовательно соединенные блок фильтрации ложных нулей, третий элемент привязки, третий элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, третий элемент И, третий измерительный счетчик и пятый информационный регистр, при этом сигнальный вход блока фильтрации ложных нулей соединен с выходом второго элемента привязки, а его тактовых вход, синхровход третьего элемента привязки и второй вход третьего элемента И вЂ” с выходом генератора счетных импульсов, выход второго элемента привязки соединен с вторым входом третьего элемен5 та ИСКЛЮЧАЮЩЕЕ ИЛИ, выход третьего элемента привязки соединен с вторым входом второго элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ, а также со счетным входом счетчик числа периодов и С-входом D-триггера, ко10 торый выходом соединен с входом разрешения счета третьего измерительного счетчика, подключенного входом начальной установки к входу пуска устройства, входы записи-чтения и выход пятого ин15 формационного регистра через общую шину соединены с микропроцессорным блоком.

1800382

4. Шлшщшшшшлш(шшцшш!

И2 т иг. 4

Составитель А.Глинченко

Техред М.Моргентал Корректор Н. Кешеля

Редактор

Заказ 1162 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул,Гагарина, 101

l б