Преобразователь кода спектра звукового сигнала

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и связи. Его использование в цифровых системах записи, хранения звуковой информации, в системах воспроизведения и передачи звуковых сигналов позволяет повысить точность преобразования за счет снижения шумов квантования. Преобразователь содержит запоминающий узел I, детектор 2 порядка максимальной составляющей, регистр 3 кода порядка, формирователь 4 разрядностей мантисс, селектор 6 мантисс, запоминающий блок 8 и синхронизатор 9. Благодаря введению регистра 5 разрядностей мантисс и блока 7 суммирования качество звучания восстанавливаемого после передачи звукового сигнала улучшается. 1 з,п.ф-лы. 10 ил.

1800618 А1

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР

{ГОСПАТЕНТ СССР) 1 ур

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4833840/24 (22) 31.05.90 (46) 07.03.93. Бюл. М 9 (71) Всесоюзный научно-исследовательский институт радиовещательного приема и аку. стики им. А,С. Попова (72) M.Н. Моисеев, А.Н. Абрамов, А.С. Грудинин и П.П. Котов (56) Caine С.R., English А.К., О Clearey J.M, И!CAM — ill — near-instanteneusly companded

digitai transmission system for high-quality

sound programmes. — The Radio and

Electronic. Eng. 1980, ч. 50, М 20.

Авторское свидетельство СССР

М 1624702, кл. Н 04 L 17/30, 1982.

Авторское свидетельство СССР

N 1711331, кл. Н 03 М 3/00, 1987. (5t)s Н 03 M 3/00, Н 04 B 1/64, 14/04 (54) ПРЕОБРАЗОВАТЕЛЬ КОДА СПЕКТРА

ЗВУКОВОГО СИГНАЛА (57) Изобретение относится к вычислительной технике и связи, Его использование в . цифровых системах записи, хранения звуковой информации, в системах воспроизведения и передачи звуковых сигналов позволяет повысить точность преобразования за счет снижения шумов квантования.

Преобразователь содержит запоминающий узел l, детектор 2 порядка максимальной составляющей, регистр 3 кода порядка, формирователь 4 разрядностей мантисс, селектор 6 мантисс, запоминающий блок 8 и синхронизатор 9. Благодаря введению регистра 5 разрядностей мантисс и блока 7 суммирования качество звучания восстанавливаемого после передачи звукового сигнала улучшается. 1 з.п.ф-лы. 10 ил.

1800618

Изобретение атносится к вычислительной технике и связи и может быть использовано в цифровых системах записи, хранения звуковой информации, в системах воспроизведения, а также передачи звуковых сигналов (3 С).

Цель изобретения — повышение точности преобразования за счет снижения шумов квантования, что приводит к увеличению пропускной способности канала связи.

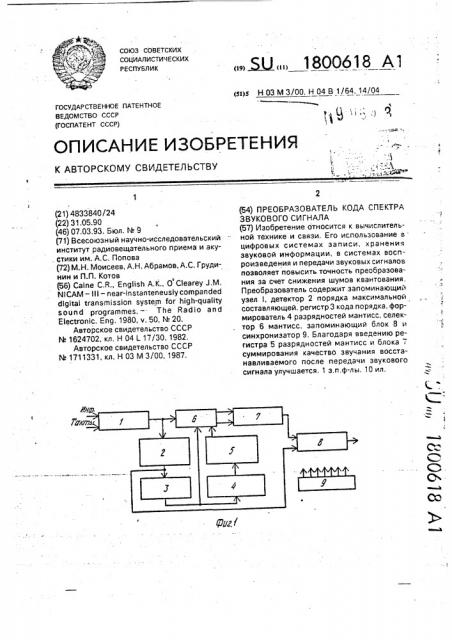

На фиг.1 изображена структурная схема преобразователя кода; на фиг.2 — структурная схема запоминающего узла; на фиг.3— схема, формирующая заданную задержку в блоках управляемой задержки; на фиг.4— временная диаграмма ее работы для длины входной выборки N=8; на фиг.5 — структурная схема блока оперативной памяти; на фиг.б — структурная схема регистра кода порядка; на фиг,7 — структурная схема формирователя разрядностей мантисс и регистра разрядностей мантисс; на фиг.8— структурная схема селектора л1антисс и блока суммирования; на фиг.9 — структурная схема запоминающего блока; на фиг.10— временные диаграммы, поясняющие работу синхронизатора.

Преобразователь кода содержит запоминающий узел 1, детектор порядка максимальной составляющей 2, регистр кода порядка 3, формирователь разрядностей мантисс 4, регистр разрядностей мантисс 5, селектор мантисс 6, блок суммирования 7, запоминающий блок 8 и синхронизатор 9.

Входные отсчеты спектра звукового сигнала поступают на информационный вход 10 запоминающего узла и сопровождаются синхроимпульсами, поступающими на тактовый вход 11. Блок оперативной памяти, запоминающего узла 1 имеет два буфера памяти и соответственно два режима работы: 1) первый буфер накапливает новую выборку входных отсчетов, а второй выдает на выход накопленную выборку для обработки, 2) наоборот — второй накапливает, а первый выдает на выход. Обработка выборки, накопленной в блоке оперативной памяти, имеет четыре последовательные во времени фазы:

1) Разбиение выборки на частотные группы и определение величины порядка (при представлении с плавающей запятой) в каждой группе.

2) Определение требуемой разрядности мантисс для каждой группы.

3) Усечение мантисс в соответствии с полученной разрядностью.

4) Ожидание начала новой выборки.

30

В первой фазе информации с выхода запоминающего узла 1 подается на вход детектора порядка максимальной составляющей 2, который исходя из величин максимальных составляющих в группах определяет порядки для каждой группы, и эти порядки записываются в регистр 3 кода порядка и запоминающий блок 8.

Во второй фазе коды порядков из регистра 3 подаются на формирователь разрядностей мантисс 4, который определяет необходимую длину мантисс в каждой частотной группе и записывает ее в регистр разрядностей мантисс 5.

В третьей фазе входные отсчеты из запоминающего узла 1, коды порядков из регистра 3 и коды разрядностей мантисс иэ регистра 5 подаются на селектор мантисс 6, который выделяет разряды мантисс, подлежащие передаче по каналу связи;- С-помощью блока 7 суммирования эти разряды корректируются для уменьшения шума квантования и записываются в запоминающий блок (ЗБ) 8, в который поступают и коды порядков иэ регистра 3.

После обработки информация из ЗБ 8 равномерным потоком считывается в канал связи, а преобразователь находится в режиме ожидания начала следующей выборки.

Работа всех блоков происходит под управлением синхронизатора, соответствующие выходы которого подключены ко входам синхронизации всех блоков- преобразователя.

5 Структурная схема запоминающего узла приведена на фиг.2.

Выборка из N спектральных отсчетов со входа 10 подается на вход демультиплексора 12 и сопровождается синхроимпульсами

0 11, поступающими на вход счетчика 13. Демультиплексор 12 по управляющему сигналу от счетчика 13 подключает- вход поочередно K 1-му и 2-му выходам и пропускает нечетные отсчеты на вход первого

5 блока управляемой задержки (БУЗ1) 14, а четные — на вход второго (6Y32) 15. Блоки управляемой задержки 14 и 15 также управляются сигналом от счетчика 13, который подсчитывает количество пришедших на вход спектральных отсчетов. Управление происходит таким образом, на нечетные отсчеты 1,3,...,N-1 (как правило используются значения N, равные степени двойки) после задержки имеют положение с 1 по М/2, а четные — 2,4...„N — положение с N/2+1 по й.

Для этого 1-й отсчет задерживается в БУЗ 1

14 на время N/2-1, 3-й — на время N/2-2.

5-й — на N/2-3,...,(N-t)-й íà N/2-N/2=0. БУЗ2

15 обеспечивает задержку 2-го отсчета на время N-2. 4-го — íà N-З....,N-го — нз N/2-1.

1800618

Затем сигналы с выходов. блоков управляемой задержки 14 и 15 записываются в блок оперативной памяти 16.

Блоки управляемой задержки 14 и 15 реализуются на базе оперативного запоминающего устройства (для этого можно использовать ОЗУ блока оперативной памяти

16) с использованием управления адресами записи и считывания.

Чтобы получить требуемую перестановку входных данных, описанную выше, необходимо записать нечетные отсчеты; 1-й отсчет по адресу 1, 3-й — по адресу 2, 5-й— по адресу 3, 7-й — по адресу 4...; (N-1)-й — по адресу N/2, а четные: 2-й — по адресу

N/2+1, 4-й — по адресу N/2+2, 6-й — по адресу N/2+З,...,N-й — по адресу N.

Схема, формирующая указанные адреса, приведена на фиг.3, а временные диаграммы, поясняющие его работу, для случая

N=8 — на фиг,4.

Входные данные с информационного входа 10 (фиг.3) поступают на вход О блока оперативной памяти 16. Работа начинается с приходом от синхронизатора 9 импульса частоты блока 17. который подается на вход

Я счетчика импульсов 13 и обнуляет его.

Синхроимпульсы с тактового входа 11 подаются на счетный вход С счетчика импуль- сов 13, выходные разряды которого, сдвинутые на 1 (т.е. -деленные в 2 раза), подаются на-первый вход сумматора 18, а младший разряд управляет мультиплексором 19. который поочередно пропускает на второй вход сумматора 18 либо О, либо N/2.

На временной диаграмме (фиг.4) изображены следующие сигналы: а) частота блока; б) синхроимпульсы 11 входных отсчетов; в) значение первого входа сумматора

18; г) управляющий вход мультиплексора

19; д) смещение на втором входе сумматора

18; е) адрес записи на выходе сумматора

18;

Структурная схема блока оперативной памяти (БОП) 16 приведена на фиг.5. Входная информация поступает на вход 20 БОП (фиг.5) и с помощью демультиплексора 21 записывается в одно из двух ОЗУ: 22 или 23, . Выбор ОЗУ осуществляется счетным триггером 24, на вход которого поступают импульсы частоты блока 17. которые показаны на фиг. 4 а). Таким образом, БОП 16 имеет два режима: первый — ОЗУ 22 принимает информацию, а ОЗУ 23 выдает на выход; второй— наоборот. При приеме информации адреса по входу,30. Демультиплексоры 31 и 32 работают аналогично демультиплексору 21 и

25 переключают адресные входы ОЗУ либо на

5

ОЗУ перебираются последовательно от 1 до

N nо управляющим сигналам 25 от синхронизатора. При выводе информации ОЗУ работает в первой и третьей фазе. B первой: информация из ОЗУ последовательно поступает на выход 26 и обрабатывается детектором порядка максимальной составляющей 2; при этом работа селектора мантисс 6 приостановлена, В третьей фазе информация иэ ОЗУ поступает последовательно на выход 26 и используется для работы селектора мантисс 6. при этом работа детектора 2 уже закончена. В первой фазе

ОЗУ управляется адресами .считывания при формировании порядков в группах (вход 27), а в третьей — адресами считывания при усечении мантисс (вход 28), Во второй и в четвертой фазе БОП 16 е обработке информации не участвует. Переключение адресовна ОЗУ в различных фазах работы происходит с помощью мультиплексора 29, управляемого сигналами от блока синхронизации считывание, либо на запись. Мультиплексор

33 аналогично подключает к выходу 28 поочередно оба ОЗУ.

Детектор 2 порядка максимальной составляющей полностью аналогичен соответствующему блоку прототипа. Он разбивает все входные коэффициенты на группы, находит максимальный коэффициент в каждой группе и по этому коэффициенту определяет порядок для всей группы.

Порядки всех групп записываются в регистр кода порядка 3. B первой фазе обработки порядки групп из детектора 2 поступают на вход 26 (фиг,6) и записываются в ОЗУ 34. Во второй фазе информация считывается на выход 35 и используется формирователем разрядностей мантисс 4, В третьей фазе порядки поступают на выход и обрабатываются селектором мантисс 5.

Адреса управления 03Y so всех режимах (входы 36, 37, 38) формируются блоком синхронизации и коммутируются на адресные входы ОЗУ с помощью мультиплексора 39, управляемого аналогично мультиплексору

29 сигналом по входу 30.

Формирователь разрядностей мантисс

4 выполняет функцию блока формирования адреса считывания мантисс прототипа (3).

Но если в прототипе при определении разряда данных, подлежащего передаче, он немедленно передавался в канал связи, то в предлагаемом устройстве формирователь 4 вырабатывает сигнал для регистра 5, в котором записывается длина мантисс, подлежащих передаче в каждой группе.

1800618

20

25 применение при передаче сигналов звукового вещания и стереосопровождения телевидения.. 30

1-8. Кроме того, временные диаграммы, поясняющие работу синхронизатора. приведены на фиг.10 для случая, когда в-первую группу "входит коэффициент 1, во вторую—

2, в третью — 3. Кроме того, этот пример приведвн для случая, когда для коэффициента i=1: порядок равен макс=2 (т.е, производятся два сдвига по сдвигающему входу регистра 60, два такта на синхровыход 68 в это время не проходят), а разрядность мантиСсы равна трем (проходят три такта на синхровыход 68); для второго коэффициента: порядок равен мак=1, а разрядность мантиссы равна трем; для третьего коэффициента: порядок равен макс-3, а . разрядность мантиссы равна двум. По синхросигналу 88 равномерно за время длительности выборки (частота F блока) счи-тываются Вма<с разрядов мантисс и коды Крр штук порядков (при 16 разрядных коэффициентах величина порядка от 0 до 15, что может кодировзться четырьмя битами).

Предлагаемое устройство предполагается использовать в системе формирования позывных радиовещания при хранении звуковых Сигналов в твердотельных запоминающих устройствах. Возможно также его

Преобразователь кода опробован во

ВНИИРПА им. А,С. Попова на сигнале звукового вещания высшего класса (Faepx. = 22 Кгц, Ед -48 Кгц, ИКМ- lб разрядов).

Измерения проводились следующим образом: один и тот же сигнал обрабатывался с помощью устройства, выбранного в качестве прототипа, и предлагаемого устройства и вычислялось среднеквадратичное отклонение (СКО) для каждой обработанной выборки. Всего испытательный звуковой фрагмент содержал 2220 выборок, что составляет около 8 сек звучания.

Субъективно-статистическая экспертиза подтвердила, что предлагаемого устройство улучшает качество звучания восстановленного сигнала.

Предложенное решение позволит в синтезаторах позывных снизить шумы квантования и тем самым исключить необходимОсть в наращивании сложных, дорогостоящих ЗУ.

Формула изобретения

1. Преобразователь кода спектра звукового сигнала, содержащий запоминающий

55 узел, выход которого соединен с первым информационным входом селектора мантисс и информационным входом детектора порядка максимальной составляющей, выход которого подключен к информационному входу регистра кода порядка, выход которого соединен с информационным входом формирователя разрядностей мантисс и вторым информационным входом селектора мантисс, запоминающий блок, выход которого является выходом преобразователя, и синхронизатор, соответствующие выходы которого подключены к входам синхронизации всех блоков преобразователя, о тл и ч а ю шийся тем, что, с целью повышения точности преобразования за счет снижения шумов квантования, в преобразователь введены регистр разрядностей мантисс и блок суммирования, выход формирователя разрядностей мантисс соединен с информационным входом регистра разрядностей мантисс, вход синхронизации которого и вход синхронизации блока суммирования подключены к соответствующим выходам синхронизатора, выход регистра разрядностей мантисс соединен с третьим информационным входом селектора мантисс, первый и второй выходы которого подключены к одноименным входам блока суммирования, выход которого соединен с первым информационным входом запоминающего блока, второй информационный вход которого подключен к выходу детектора порядка максимальной составляющей, информационный и тактовый входы запоминающего узла являются одноименными входами преобразователя.

2. Преобразователь по п,1, о т л и ч а юшийся тем, что запоминающий узел содержит счетчик импульсов, первый и второй блоки управляемой задержки, блок оперативной памяти и демультиплексор, информационный вход которого и вход счетчика импульсов являются соответственно информационным и тактовым входами узла, выход счетчика импульсов соединен с управляющими входами блоков управляемой задержки и демультиплексора, первый и второй выходы которого подключены к информационным входам соответственно первого и второго блоков управляемой задержки, выходы которых объединены и соединены с входом блока оперативной памяти, выход которого является выходом узла.

1800618

I а

I

М

f з

1800618