Устройство автоматической подстройки частоты

Иллюстрации

Показать всеРеферат

Использование: радиотехника. Сущность изобретения: точность подстройки при частых пропаданиях сигнала повышается путем обеспечения режима памяти и отключения цепи автоподстройки частоты при частом пропадании входного сигнала. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5!)5 Н 03 (7/00

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

С>

Од

V !

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) 1698987 (21) 4867919/09 (22),21.09.-90 (46) 3,03,93. Бюл, М 11 (71) осковский институт инженеров железнод рожного транспорта (72) А.Ф.Фомин, В.А.Бахарев, И.Н.Малышев В.И,Шелухин, О,И.Шелухин, В.М.Артюшенко и В.А.Парилов (56) авторское свидетельство СССР

М 1 98987, кл, Н 03 1 7/00, 04.12.89. зобретение относится к радиотехнике и мо ет быть использовано в качестве следящ х измерителей и демодуляторов.

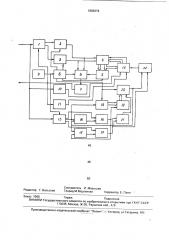

Цель изобретения — повышение точности г ри частых пропаданиях входного сиг- . нала. а чертеже приведена блок-схема устройства автоматической подстройки частоты.

Устройство автоматической подстройки часто1гы содержит: цифровой фазовый де1 тектор 1, устройство усреднения канала добавления 2, устройство усреднения канала вычитания 3, цифровой интегратор 4, преобразователь код-частота 5, устройство добавления ;вычитания 6, основной делитель 7, распределитель импульсов 8, опорный генератор 9, первый выделитель фронта 10, второй выделитель фронта 11, блок частотной подстройки 12, дополнительный распределитель импульсов 13, первый дополнительный R5-триггер 14, второй дополнительный

RS-триггер 15, первый элемент И 16, второй элемент И 17, первый счетчик 18, регистр 19, второй счетчик 20, элемент ИЛ И 21 и третий дополнительный RS-триггер 22. Первый

„„Я2„„1803976 А2

2 (54) УСТРОЙСТВО АВТОМАТИЧЕСКОЙ

ПОДСТРОЙКИ ЧАСТОТЫ (57) Использование: радиотехника. Сущность изобретения: точность подстройки при частых пропаданиях сигнала повышается путем обеспечения режима памяти и отключения цепи автоподстройки частоты при частом пропадании входного сигнала. 1 ил. вход цифрового фазового детектора 1 объединен с входом первого выделителя фронта

11 и входом синхронизации дополнительного распределителя импульсов 13 и является входом устройства. Выход основного делителя 7 является выходом устройства и, кроме того, соединен с входом второго выделителя фронта 11 и вторым входом цифрового фазового детектора 1, первый выход которого соединен с первым входом устройства усреднения канала добавления

2, а второй выход цифрового фазового детектора 1 соединен с первым входом устройства усреднения канала вычитания 3, выход которого соединен с входом импульсов вычитания цифрового интегратора 4 и первым входом устройства добавления-вычитания

6. Выход устройства усреднения канала добавления 2 соединен с вторым входом устройства добавления-вычитания 6 и входом импульсов добавления цифрового интегратора 4, выходы которогосоединены с информационными входами преобразователя код-частота 5, тактовым входом соединенного с первым выходом распределителя импульсов 8, а выход преобразователя

1803976

20

35

55 код-частота 5 соединен с третьим входом устройства добавления-вычитания 6, четвертый вход которого соединен с вторым выходом распределителя импульсов 8, соединенного с вторым выходом устройства усреднения канала вычитания 3. Четвертый выход распределителя импульсов 8 соединен с вторым входом устройства усреднения канала добавления 2, а вход распределителя импульсов 8 объединен с тактовым входом дополнительного распределителя импульсов 13 и соединен с выходом опорного генератора 9. Кроме того, выход устройства добавления-вычитания 6 соединен с входом основного делителя 7, Выходы первого выделителя фронта 10 и второго выделителя фронта 11 соединены соответственно с первым и вторым входами блока частотной подстройки 12. Информационные выходы блока частотной подстройки 12 подключены к старшим входам цифрового интегратора 4, а информационные входы блока частотной постройки 12 подключены к N старшим выходам цифрового интегратора 4, Выход блока частотной подстройки 12 соединен с входом цифрового интегратора 4, Кроме того, один из входов первого элемента И 16 соединен с первым выходом дополнительного распределителя импульсов 13, а другой вход — с выходом первого дополнительного RS-триггера 14, Sвход которого объединен с входом сброса первого счетчика 18 и соединен с вторым выходом дополнительного распределителя импульсов 13, третий выход которого соединен с одним из входов второго элемента И

17, а другой его вход соединен с выходом второго дополнительного RS-триггера 15, Sвход которого объединен с тактовым входом регистра 19 и подключен к выходу первого элемента И 16. Таковые входы счетчиков 18, 20 подключены к пятому дополнительному выходу распределителя импульсов 8, причем выход первого счетчика 18 соединен с информационным входом регистра 19, а его выход соединен с входом предварительной установки со сдвигом на один разряд вправо второго счетчика 20, вход управления предварительной записью которого подключен к выходу элемента ИЛИ 21, Вход сигнала переполнения второго счетчика 20 подключен к S-входу третьего дополнительного триггера 22, к одному из входов элемента ИЛИ 21 и R-входам первого и второго дополнительных RS-триггеров 14, 15. Другой вход элемента ИЛИ 21 и R-вход третьего дополнительного RS-триггера подключены к выходу второго элемента И 17, а выход третьего дополнительного RS-триггера 22 подключен к входу блокировки блока частотной подстройки 12.

Формула изобретения

Устройство автоматической подстройки частоты по авт, св. N 1698987, о т л и ч а ющ е е с я тем, что, с целью повышения точности при частых пропаданиях входного сигнала, в него введены дополнительный распределитель импульсов, тактовый вход и вход синхронизации которого подключены соответственно к выходу опорного генератора и входу устройства, последовательно соединенные первый дополнительный RSтриггер и первый элемент И, последовательно соединенные второй дополнительный

RS-триггер и второй элемент И, последовательно соединенные первый счетчик и регистр, а также второй счетчик, элемент ИЛИ и третий дополнительный RS-триггер, при этом распределитель импульсов снабжен пятым выходом, подключенным к тактовым входам первого и второго счетчиков, выход сигнала переполнения второго счетчика подключен к S-входу третьего дополнительного RS-триггера, к одному из входов элемента ИЛИ и R-входам первого и второго дополнительных RS-триггеров, другой вход элемента ИЛИ и R-вход третьего дополнительного RS-триггера подключены к выходу второго элемента И, первый выходдополнительного распределителя импульсов подключен к другому входу первого элемента И, второй выход — к S-входу первого дополнительного RS-триггера и входу сброса первого счетчика, а его третий выход — к другому входу второго элемента И, выход первого элемента И подключен к S-входу второго дополнительного RS-триггера и тактовому входу регистра, выход регистра подключен к входу предварительной установки со сдвигом на один разряд вправо второго счетчика, вход управления предварительной записью которого подключен к выходу элемента ИЛИ, а выход третьего дополнительного RS-триггера подключен к входу блокировки по меньше мере одного из блоков, включенных между выходами первого и второго выделителей фронтов и входам управления параллельной записью старших разрядов и информационными входами N старших разрядов цифрового интегратора, 1803976

Составитель И, Малышев

Редактор Г. Бельская Техред М.Мор гентал Корректор Е. Папп

Заказ 1060 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101