Устройство для преобразования цифровых сигналов

Иллюстрации

Показать всеРеферат

| Изобретение относится к электросвязи и может быть использовано в системах телефонрой связи с дельта-модуляцией с цифровым инерционным компандированием. Цель изобретения - повышение помехоустойчивости . Дельта-п-разрядный двоичный регистр сдвига 1, n-разрядного буферного регистр-сдвига 2, ключ 4, счетчик 5, дешифратор б, триггер 7, блок синхронизации 8 и управляемый генератор 9, шину тактовых импульсов 3, слоговый фильтр 10, амплитудно-импульсный модулятор 11, интегратор 12, выходной фильтр нижних частот 13 и обеспечивает сведение к нулю воздействие случайных ошибок с вероятностью менее 3,3 на работу блока компандирования. 2 ил., 1 табл.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 Н 03 М 5/00

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР

g OCllATEHT CCCP) ()ПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

6/Х (2i1) 4912381/24 (2 ) 20.02.91 (46) 23.03,93. Бюл. N 11 (71) Грузинский технический университет (7 ) Н.Г.Харатишвили, В.В.Нанобашвили, P. Ã.ÑBàíèä3å и Г.Ш.Джавахишвили (56) Патент Великобритании ¹ 2004165, кл1,. Н 03 К 19/30, опублик. 1979.

Авторское свидетельство СССР

N."1109925, кл. Н 04 1 3/02, 1982. (5 ) УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАН Я ЦИФРОВЫХ СИГНАЛОВ (5 Изобретение относится к технике электроЯЛ 1803982 А1 связи и может быть использовано для преобразования цифровых сигналов линейного тракта при передаче информации по волоконно-оптическому кабелю в цифровой информационный сигнал. Цель изобретения— расширение области применения устройства за счет преобразования не только сигнала CMI, но и линейных сигналов RZ, Bl-L u

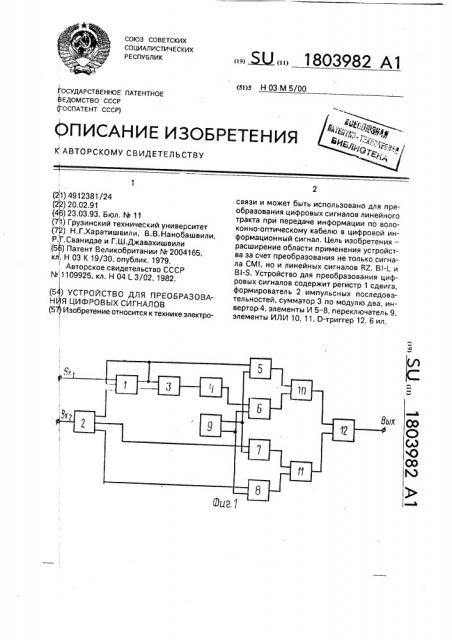

Bl-S. Устройство для преобразования цифровых сигналов содержит регистр 1 сдвига. формирователь 2 импульсных последовательностей, сумматор 3 по модулю два, инвертор4, элементы И 5 — 8, переключатель 9, элементы ИЛИ 10, 11, 0-триггер 12. 6 ил.

1803982 ся от символа, расположенного на аторои Bb

Изобретение относится к технике электросвязи и может быть использовано для преобразования цифровых сигналов линейного тракта при передаче информации по волоконно-оптическому кабелю в цифровой информационный сигнал NRZ-1 .

Цель изобретения — расширение области применения устройства за счет преобразования не только сигнала CM 1, но и линейных сигналов RZ, 81-1 и BI-S.

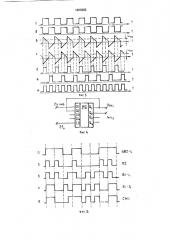

На фиг. 1 представлена структурная электрическая схема устройства для преобразования цифровых сигналов; на фиг, 2— принципиальная схема формирователя импульсных последовательностей; на фиг. 3— временные диаграммы, характеризующие работу формирователя импульсных последовательностей; на фиг. 4 — схема включения регистра сдвига; на фиг. 5 — алгоритмы преобразования исходного сигнала NRZ-L в линейные сигналы RZ, В1-1, Bl-S |4 CM I; на фиг. 6 — временные диаграммы, характеризующие работу устройства, Устройство для преобразования цифровых сигналов содержит регистр 1 сдвига, формирователь 2 импульсных последовательностей, сумматор 3 по модулю два, инвертор 4, элементы И 5 — 8, переключатель 9, первый и второй элементы ИЛИ 10, 11, 0триггер 12.

Формирователь 2 импульсных последовательностей предназначен для формирования сигнала удвоенной тактовой частоты

2fT, а также двух последовательностей сигналов тактовой частоты fT, сдвинутых друг относительно друга по фазе на 1800.

Устройство для преобразования цифровых сигналов работает следующим образом, На первый вход устройства (вход Dl регистра сдвига, фиг. 4) подается любой из линейных сигналов — RZ, BI-L, Bl-S u DBI.

Эти сигналы получаются с помощью преобразования сигнала NRZ-L (фиг. 5а) на передающей стороне, Алгоритмы такого преобразования приведены на фиг. 5.

Сигнал RZ (фиг. 5б) формируется из сигнала NRZ-L путем уменьшения длительностей токовых посылок в два раза, B сигнале Bl-1 (фиг. 5в) исходные символы "1и и мОн представляются соответственно блоками линейного кода 01 и 10.

Сигнал BI-S(фиг,,5г) характеризуется наличием переходов 1 — 0 и 0 - 1 в начале каждого тактового интервала, а также наличием перехода в середине тактового интервала при наличии символа "Он в исходном сигнале. При этом символ на первой половине любого тактового интервала отличает5

55 половине предыдущего тактового интервала, Сигнал CMI (фиг. 5г) характеризуется чередованием в токовых и бестоковых посылок при передаче символов "1м исходной последовательности, а сигнал нОн исходной последовательности передается блоком символов 01:

На тактовый (второй) вход регистра 1 сдвига подается сигнал удвоенной тактовой частоты 2fT, формируемый на первом входе формирователя 2 (фиг. 2ж), формирование этого сигнала происходит следующим образом.

На вход формирователя 2 (фиг. 2) поступает сигнал тактовой частоты fT (фиг. 3a). Он подается на вход первой дифференцирующей цепи C. Инвертированный сигнал (фиг. Зб) подается на вход второй дифференцирующей цепи СгВ2. Выходные сигналы дифференцирующих цепей (фиг, 3 в, г) подаются на входы ключей-повторителей Э2 и Эз нэ выходах которых сигналы имеют форму, приведенную на диаграммах фиг, 3, д. е. Выходы элементов 3z и Эз являются соответственно вторым и третьим выходами формирователя импульсных последовательностей, Сигналы д и е являются. сигналами тактовой частоты, сдвинутыми друг относительно друга по фазе на 1800. Эти сигналы объединяются с помощью логического элемента ИЛИ (Э4), вследствие чего на выходе последнего формируется сигнал удвоенной тактовой частоты 2fT (фиг, Зж).

Рассмотрим процессы преобразования линейных сигналов RZ и ВI-L(фиг, 6 а, б).

Под воздействием сигнала 2fT (фиг, бд) на первом Qi и втором 02 выходах регистра

1 сдвига (фиг. 4) формируются соответственно входная последовательность и ее копия, сдвинутая относительно последовательности на выходе Q< во времени на Т/4 (где Т— длительность тактового интервала ). Последовательность с выхода Qi (фиг, 6з в случае сигнала RZ и фиг. 6 и в случае сигнала Bl-1) поступает на первый вход элемента И 5, на второй вход которого подается уровень м1н с переключателя 9, предварительно переключенного в положение, соответствующее декодированию сигналов RZ u Bl-L. При этом положении переключателя 9 отпирается также элемент И 7 и запираются элементы И 6 и 7, на вторые входы которых подаются нулевые уровни. В результате декодируемый сигнал (RZ или ВН ) через элемент ИЛИ 10 поступает на D-вход

0-триггера 12, а на С-вход подается сигнал тактовой частоты (фиг, Зе, фиг, 6ж) с второго хода формирователя 2 через элементы И

1803982

7 и ИЛИ 11. От положительного фронта этого сигнала D-триггер срабатывает и на его прямом выходе. В обоих случаях формируется исходный информационный сигнал

NRZ-1 (фиг. 6к).

В случае преобразования сигналов Bl-S и CMI (ôèã, 6 в, г) сигналы, формируемые на первом и втором выходах регистра 1 сдвига (фиг. 6 л, м в случае сигнала Bl-S и фиг. 6 п, Д в случае сигнала СМ 1), суммируются в сумматоре 3 по модулю два (фиг. 6, н в случае сигнала Bl-$ и фиг. 6, с в случае сигнала CMI), результат инвертируется (фиг.

8, о в случае сигнала Bl-S и фиг. 6т в случае сигнала CM 1), а затем через элемент И 6, который отпирается переключением переключателя 9 в другое состояние (при этом на вторые входы элементов И 5 и 7 подается уровень "0", а на вторые входы элементов И

6 и 8 уровень "1"), и через первый элемент

1Р ИЛИ подается íà D-вход D-триггера 12.

Одновременно через элемент И 8 и второй элемент ИЛИ 11 на С-вход D-триггера пос1упает сигнал тактовой частоты (фиг, 6е) с третьего выхода формирователя 2 (фиг. 2). В результате на прямом выходе D-триггера в о оих случаях формируется информационн4й сигнал NRZ-L (фиг, 6у).

Формула изобретения

Устройство для преобразования цифровых сигналов, содержащее регистр сдвига, первый вход которого является первым входом устройства, первый элемент ИЛИ, выход которого соединен с D-входом Отриггера, выход которого является выходом устройства,отл ич а ю щееся тем, что, с целью расширения области применения ус5 тройства за счет преобразования линейных сигналов RZ, BI-L u BI-S, в него введены сумматор по модулю два, инвертор, переключатель, элементы И, второй элемент

ИЛИ и формирователь импульсных после10 довательностей, вход которого является вторым входом устройства, первый, второй и третий выходы формирователя импульсных последовательностей соединены соответственно с вторым входом регистра

15 сдвига, первым входом первого элемента И и первым входом второго элемента И, первый выход регистра сдвига соединен с первыми выходами сумматора по модулю два и третьего элемента И и третьим входом реги20 стра сдвига, второй выход которого соединен с вторым входом сумматора по модулю два, выход которого через инвертор соединен с первым входом четвертого элемента

И, первый выход переключателя соединен с

25 вторыми входами первого и третьего элементов И, выходы которых соединены с первыми входами соответственно второго и первого элементов ИЛИ, второй выход переключателя соединен с вторыми входами

30 второго и четвертого элементов И, выходы которого соединены с вторыми входами соответственно второго и первого элементов

ИЛИ, выход второго элемента ИЛИ соединен с С-входом D-триггера, пор

bX., !

3803982

Фи>. 5

I (NRZ-L

1803982

%вмеюй

Редактор С.Иванова

Заказ 1061 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

Q б

5 ! д

Составитель Н.Бочаров

Техред М.Моргентал Корректор С.Пекарь