Выходной блок тестера для контроля цифровых блоков

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может использоваться в составе тестеров для контроля цифровых блоков. Цель изобретения - расширение области применения и повышение достоверности контроля. Блок содержит шифратор логических состояний, триггер, инвертор с открытым коллектором, элемент равнозначности , элемент И, триггер, узел согласования нагрузки, входной регистр, элементы развязки, токозадающие элементы, выходной регистр, вход/выход, информационные выходы, выход сигнала Короткое замыкание , вход задания режима работы, тактовый вход, вход строба, вход сброса и входы задания типа нагрузки. Цель достигается за счет обеспечения возможности контроля устройств с различной схемно-технологической реализацией микросхем, а также возможности определения короткого замыкания двунаправленного вывода объекта контроля.2 ил. Ё

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) ОПИСАНИЕ ИЗОБРЕТЕН

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ,> (21) 4842870/24 (22) 25,06.90 (46) 30.03.93. Бюл. ¹ 12 (71) Специальное проектно-конструкторское и технологическое бюро реле и автоматики (72) А.П, Вишняков, А.А. Вдовиченко, Д,И, Павлив (56) Авторское свидетельство СССР

N 822190, кл. G 06 F 11/00, 1979.

Авторское свидетельство СССР

¹ 1213444, кл. G 01 R 31/28, 1984. (54) ВЫХОДНОЙ БЛОК TECTEPA ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ БЛОКОВ (57) Изобретение относится к вычислительной технике и может использоваться в составе тестеров для контроля цифровых блоков. Цель изобретения — расширение обИзобретение относится к вычислительной технике и может быть использоваться в составе тестеров для контроля цифровых логических блоков ТТЛ, КМОП и других совместимых с ними по уровням сигналов, Цель изобретения — расширение области применения и повышение достоверности контроля.

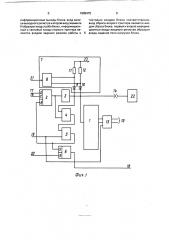

На фиг.1 представлена схема блока; на фиг.2 — временная диаграмма его работы.

Блок содержит шифратор 1 логических состояний, триггер 2, инвертор 3 с открытым коллектором, элемент 4 равнозначности, элемент И 5, триггер 6, узел 7 согласования нагрузки, входной регистр 8, элементы 9, 10 развязки, токозадающие элементы 11, 12, выходной регистр 13, вход/выход 14, информационные выходы 15, выход 16 сигнала

"Короткое замыкание", вход 17 задания ре,, Ы„„1805470 А1 (si)s G 06 F 11/00, G 01 R 31/28 ласти применения и повышение достоверности контроля. Блок содержит шифратор логических состояний, триггер, инвертор с открытым коллектором, элемент равнозначности, элемент И, триггер, узел согласования нагрузки, входной регистр, элементы развязки, токозадающие элементы, выходной регистр, вход/выход, информационные выходы, выход сигнала "Короткое замыкание", вход задания режима работы, тактовый вход, вход строба, вход сброса и входы задания типа нагрузки. Цель достигается за счет обеспечения возможности контроля устройств с различной схемно-технологической реализацией микросхем, а также возможности определения короткого замыкания двунаправленного вывода объекта контроля. 2 ил. жима работы, тактовый вход 18, вход 19 строба, вход 20 сброса и входы 21 задания типа нагрузки, На чертеже показаны также объект 22 контроля и шина 23 логической единицы, Выходной блок работает следующим образом.

Циклом проверки объекта контроля (О К)

22 считается фиксированный поток цифровых последовательностей, повторяющийся через определенные (обычно равные) промежутки времени, При этом выходной блок тестера, подключенный к двунаправленному выводу ОК 22, может работать как в режиме выдачи, так и в режиме приема информации.

В режиме выдачи на вход 17 подается как "1", так и "0", которые, проходя через триггер 2 и инвертор 3 с открытым коллекто1805470 ром, определяют входные логические уровни для ОК 22 соответственно как "0" и "1".

При этом "0" на входе 17 переводит инвертор 3 в пассивное состояние, а уровень "1" формируется узлом 7.

В режиме выдачи определяется короткое замыкание двунаправленного вывода

0К, при котором сигналы на выходе триггера 2 и инвертора 3 совпадают по уровню. В результате на выходе элемента 4 формиру- 10 ется уровень "1", что приводит при наличии строба на входе 19 к установке триггера 6 в

"1" и появлению сигнала на выходе 16 блока.

Одновременно сигнал с выхода элемента И 5 устанавливает в "0" триггер 2. По окончании строба сигнал сброса снимается и в триггер 2 можно записывать информацию со входа 17.

В те моменты времени, когда по логике 20 проверки двунаправленный вход ОК 22 должен перейти в режим выдачи, а выходной блок — в режим приема информации, на вход

17 подается уровень "0", инвертор 3 переводится в пассивное состояние и двоичная последовательность с выхода ОК 22 принимается шифратором 1, Значение третьего состояния на входе шифратора 1 кодируется им как "1","0", логической единицы — как "1", "1" и логического нуля — как "0", "0", Результат фиксируется в регистре 13 с помощью строба на входе 19, местоположение которого внутри такта выдачи данных можно менять, На фиг.2 показан фрагмент цифровой 35 последовательности (фиг.2,6) от ОК 22 и два примера поступления строба, Если фронты реального сигнала значительно отличаются от эталонного (фиг,26, пунктир), то цифровой код; формируемый шифратором 1, будет 40 также отличаться от эталонного и квалифицироваться как ошибочный (фиг.2,6), Изменяя при разных проверках местонахождение строба, можно добиться эталонной цифровой последовательности (сдвиг 45 по времени в дальнейшей обработке сигнала корректируется), определив с определенной дискретностью динамические искажения реального сигнала (фиг.2,е).

Для нормальной работы инвертора 3 с 50 открытым коллектором к его выходу через диоды 9 и 10 подключаются резисторы 11 и

12, входные выводы которых соединены с шиной+5 В. Подключение резисторов к выходу инвертора 3 осуществляется с помощью кода, записанного в регистр 8 по входам 21. Резисторы 11 и 12 имеют разное сопротивление: один из низ — величиной порядка сотен Ом, второй — единиц КОм, Ноль на каком-либо выходе регистра шунтирует соответствующий резистор и, следовательно, отключает его от инвертора 3, Подключая тот или другой резистор или оба сразу, можно изменить величину сопротивления в широких пределах, Уменьшая величину общего сопротивления на выходе инвертора 3, можно увеличить крутизну фронтов цифрового сигнала, исправить искажения формы, возникающие из — за влияния емкости монтажа. Увеличивая сопротивление, можно снизить потребление тока от объекта 22 контроля и проверить микромощную логику, например

КМОП.

При отключенном объекте контроля можно проверить правильность работы тестера, в состав которого входит данный выходной блок, кодируя с помощью шифратора 1 цифровые последовательности формируемые тестером.

Формула изобретения

Выходной блок тестера для контроля цифровых блоков, содержащий первый триггер, элемент И и шифратор логических состояний, вход которого является входом — выходом блока для подключения к двунаправленному выводу объекта контроля, отличающийся тем, что с целью расширения области применения и повышения достоверности контроля, в него введены выходной регистр, второй триггер, инвертор с открытым коллектором, элемент равнозначности и узел согласования нагрузки, содержащий входной регистр, два токозадающих элемента и два элемента развязки, причем первый и второй разрядные выходы входного регистра соединены с первыми выводами соответственно первого и второго токозадающих элементов и с анодами соответственно первого и второго элементов развязки, вторые выводы первого и второго токозадающих элементов подключены к шине логической единицы, выход первого триггера соединен с первым входом элемента равнозначности, через инвертор с открытым коллектором — с катодами первого и второго элементов развязки, с входом шифратора логических состояний и вторым входом равнозначности, выход которого соединен с первым входом элемента И, выход которого соединен с входом сброса первого триггера и с установочным входом второго триггера, выход которого является выходом сигнала "Короткое замыкание" блока, первый и второй выходы шифратора логических состояний соединены с первым и вторым информационными входами выходного регистра, первый и второй разрядные выходы которого образуют

1805470 информационные выходы блока, вход записи выходного регистра и второй вход элемента

И образуют вход строба блока, информационный и тактовый входы первого триггера являются входом задания режима работы и 5 тактовым входом блока соответственно, вход сброса второго триггера является входом сброса блока, первый и второй информационные входы входного регистра образуют входы задания типа нагрузки блока.

1805470

40

50

Составитель 3, Моисеенко

Техред М.Моргентал Корректор С, Пекарь

Редактор

Производственно-издательский комбинат "Патент", г,. Ужгород, ул.Гагарина, 101

Заказ 943 Тираж Подписное

ВНИИПИ

ИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб„4/5