Устройство для адресации памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств. Цель изобретения - повышение быстродействия устройств. Устройство содержит преобразователь кода адреса, регистр, приоритетный шифратор, коммутатор, группу элементов ИЛИ, адресные вход и выход, синхронизирующий и управляющие входы, управляющий выход и вход признаков. Адреса загружаемых и освобождаемых зон памяти фиксируются признаками, запоминаемыми в регистре. По состоянию регистра приоритетный шифратор формирует коды адресов свободных зон. Наличие группы элементов ИЛИ позволяет вести не только последовательную , но и параллельную фиксацию в регистре признаков загружаемых и освобождаемых зон. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)л G 06 F 12/08

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

В ЕДОМСТВО СССР (ГОСПАТЕНТ СССР) (21) 4879154/24 (22) 31.10.90 (46) 30,03.93. Бюл, N 12 (71) Львовский политехнический институт им, Ленинского комсомола (72) И,Б.Боженко и О.К.Мешков (56) 1. Авторское свидетельство СССР

N. 980159, кл, G 11 С 7/00, 1981, 2. Авторское свидетельство СССР

¹ 11448811885511,, кКл, G 11 С 7/00, 1987. (54) УСТРОЙСТВО ДЛЯ АДРЕСАЦИИ ПАМЯТИ (57) Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств. Цель

Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств.

Цель изобретения — повышение быстродействия устройства.

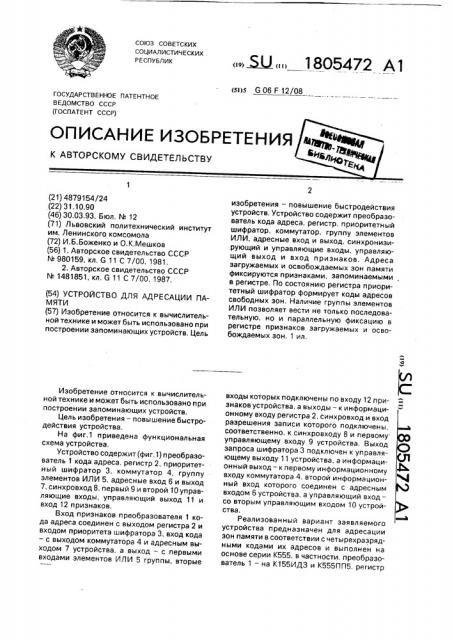

На фиг,1 приведена функциональная схема устройства, Устройство содержит (фи г,1) и реоб разователь 1 кода адреса, регистр 2, приоритетный шифратор 3, коммутатор 4, группу элементов ИЛИ 5, адресные вход 6 и выход

7, синхровход 8, первый 9 и второй 10 управляющие входы, управляющий выход 11 и вход 12 признаков, Вход признаков преобразователя 1 кода адреса соединен с выходом регистра 2 и входом приоритета шифратора 3, вход кода — с выходом коммутатора 4 и адресным выходом 7 устройства, а выход — с первыми входами элементов ИЛИ 5 группы, вторые

„„5U„„1805472 А1 изобретения — повышение быстродействия устройств, Устройство содержит преобразователь кода адреса, регистр, приоритетный шифратор, коммутатор, группу элементов

ИЛИ, адресные вход и выход, синхронизи.рующий и управляющие входы, управляющий выход и вход признаков. Адреса загружаемых и освобождаемых зон памяти фиксируются признаками, запоминаемыми в регистре, По состоянию регистра приоритетный шифратор формирует коды адресов свободных зон. Наличие группы элементов

ИЛИ позволяет вести не только последовательную, но и параллельную фиксацию в регистре признаков загружаемых и освобождаемых зон, 1 ил. входы которых подключены по входу 12 признаков устройства, а выходы — к информационному входу регистра 2, синхровход и вход разрешения записи которого подключены, соответственно, к синхровходу 8 и первому. управляющему входу 9 устройства. Выход запроса шифратора 3 подключен к управляющему выходу 11 устройства, а информационный выход — к первому информационному входу коммутатора 4. второй информационный вход которого соединен с адресным входом 6 устройства, а управляющий вход— со вторым управляющим входом 10 устройства.

Реализованный вариант заявляемого устройства предназначен для адресации зон памяти в соответствии с четырехразрядными кодами их адресов и выполнен на основе серии К555, в частности, преобразователь 1 — на К155ИДЗ и К555ПП5. регистр

1805472

2 — на К555ТМ8, шифратор 3 — на К555ИВ1, состояния регистра 2. По СИ модифицирокоммутатор — на ванный код заносится через элементы ИЛИ

Устройство работает следующим обра- 5 регистр 2 и в его соответствующем разряде признак занятости снимается, При норСовокупность управляющих сигналов 5 мальной очистке модифицированныи код на входах устроиства задает р е различные ре- признаков поступает на информационный жимы его работы. вход регистра 2 через элементы ИЛИ 5 со

Режим загрузки задается установкой в входа 12, "1" сигнала на входе и в" "

ЗАГР 9 и в "0" сигнала режим поиска свободной зоны задается

ПОИСК на входе 10; Коммутатор 4 подклю- "0 уровнями "0" на входе 9 и "1" на входе 10. чен вход 6 к выходу 7, При параллельной Коммутатор 4 подключает ко входу кода вхо 12 поступает код призна- преобразователя 1 и выходу 7 устройства ков занятости, который устанавливается на информационный выход дешифратора выходах элементов ИЛИ 5 и по отрицатель- Код адреса первой из свободных зон опреному фронту, сигнала на в

СИ а входе 8 в тех "5 деляется шифратором 3 по состоянию региразрядах регистра 2, которые соответству- стра т а2, ют занятым зонам, устанавлив станавливается "1". В режиме поиска свободных зон с их

При последовательнои в тельной загрузке код загру- последующей загрузкой сигнал ПОИСК до. П изнаки заняжаемой зоны поступает п

ы поступает по входу 6, В преоб- полняется сигналом ЗАГР. ризнаки заняразователе из это

1 этого двоичного кода 20 тости устанавливаются в регистре в формируется унитарныи код, в к отором раз- соответствии с кодом на информационном ряд, соответствующии и оступившему дво- выходе шифратора 3 аналогично работе в в егист 2 заноичному коду; фиксируется уровнем "0", а режиме загрузки, По СИ в регистр занопрочие разряды — уровнем "1", Этот код сится новое состояние на выходе преобрасравнивается в кодом пр о ом признаков на выходе 25 зователя 1 и шифратор 3 формирует код

2. П и совпадении уровня "0" со- очередной свободной зоны, регистра . р его разряда унитарного кода, Таким образом, устро ф ру йство икси ет ответствующег сформированного из двоичного кода на вхо- адреса свободных зон и ущ н и ос ествляет их ко а и еоб азователя 1 с признаками приоритетный поиск, При этом, если в устсвобо ной зоны соответствующего разряда 30 ройстве-прототипе о ущ ос ествляются лишь кода на входе признаковпреобразователя 1 последовательные загрузка и очистка зон в этом разряде на выходе пре образователя памяти, то в предлагаемом устройстве воз1ф формирует сяпризнакзанятости "1",впро- можна и параллельная фиксация зон, что тве н в еализочих же разрядах подтве тверждаются предыду- при адресации шестнадцати зо р щие состояния, Модифицированный код, 35 ванном вариантепредлагаемогоустройства б еля 1 через составит выигрыш в быстродействии максиэлементы ИЛИ 5 по СИ устанавливается в мум в 16 раз при работе в указанных режирегистре 2, При установке признака занято; сти в последнем из разрядов регистра 2 шиф атор 3 вырабатывает сигнал запроса и 0 Ф о р м у л а р

40 м ла изоб етения на выход 11 поступает сигнал полной заня- Устройство для адресации памяти, содержащее преобразователь кода адреса, тости памяти ПЗ.

B ежиме обмена на выходах 9, 10 уста- регистр, приоритетный шифратор и коммурежиме о мен новлен "0", Адреса зон передаются со входа татор, выход которого явля др г является а есным

6 через коммутатор на выход . з

4 7. И менение 45 выходом устройства и подключен к входу ков в егист е 2 блокируется. кода преобразователя кода, вход признаков вхо ом и ио итетного

Режим очистки задается повторной ус- которого соединен с в д р р тановкой "1" на входе и н

9 и "0" на входе 10. шифратора и выходом регистра, синхровПри последовательной очистке н с ке на вход 6 ход которого является соответствующим поступает код адрес а реса подлежащей очистке 50 входом устройства, а вход разрешения зазоны, который в преобразователе 1 сравни- писи — первым управляющим входом уствается с кодом признаков реги знаков регистра 2, При ройства, выход запроса шифратора совпадении уровня в

"0" в том разряде уни- является управляющим выходом устройсттарного кода, которыи о ый соответствует коду ва, а информационный выход шифратора адреса очищаемой зоны, с уровнем "1" 55 подключен к первому информационному признака занятости соответствующего входу коммутатора, второй информационразряда регистра, в этом разряд азряде на выхо- ный вход которого является адресным вхооб азователя 1 устанавливается дом устройства, а управляющий вход— де прео разователя

"0", а в прочих разрядах на выходе преоб- вторым управляющим вход у р х ом ст ойства, разователя 1 подтверждаются предыдущие о т отл ичающееся тем.что. с целью

1805472

30

40

50

Составитель H. Чуев

Техред М.Моргентал Корректор С. Патрушева

Редактор

Заказ 943 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб„4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101 повышения быстродействия, оно содержит группу элементов ИЛИ, первые входы которых соединены с выходом преобразователя кода адреса, вторые являются входом признаков устройства, а выходы подключены к информационному входу регистра.