Устройство для вычисления экстремумов

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для цифровой фильтрации сигналов и изображений или в устройствах распознавания сигналов. Цель изобретения - расширение функциональных возможностей устройства. Устройство содержит входные регистры 1,2,3 и коммутаторы 4,5, три компараторных переключателя 6,7,8, элементы 9 задержки, элементы И 10, блок 11 выбора номера числа , сумматор 12 трех чисел и генератор 13 тактовых импульсов. За счет параллельноконвейерного режима работы устройство обладает возможностью работы в реальном времени. 2 ил.

СОЮЗ COBF.1 ;ÊÈÕ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5!)5 G 06 Р 7/06

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (Гoc0ATE нт - с с с p) ОПИСАНИЕ ИЗОБРЕТЕНИ к Клокам

r,ã,ç, Е,T8g цгг

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4771320/24 (22) 19.1>.89 (46) 07.04,93. Бюл. М 13 (71.) Физико-механический институт им. Г, В. Карпен ко (72) А.Е,Батюк, А.Н.Бондарь, В.В,Грицык, А,В.Демидов, А,Ю.Луцык, Р,М,Паленичка

О,В.Подрубный и А.Н.Семашко (56) Авторское свидетельство СССР

Рл 1290295, кл.G 06 F 7/02, опублик. 1987, Авторское свидетельство СССР

М 1096638, кл.G 06 F 7/02, опублик. 1984, (54) УСТРОЙ СТВ,О ДЛ Я В Ы Ч И СЛ Е Н ИЯ

ЭКСТРЕМУМОВ,, Я) „1807476 А1 (57) Изобретение относится к вычислительной технике и может быть использовано для цифровой фильтрации сигналов и изображений или в устройствах распознавания сигналов. Цель изобретения — расширение функциональных возможностей устройства.

Тстройство содержит входные регистры

1,2,3 и коммутаторы 4,5, три компараторных переключателя 6,7,8, элементы 9 задержки, элементы И 10, блок 11 выбора номера числа, сумматор 12 трех чисел и генератор 13 тактовых импульсов. За счет параллельноконвейерного режима работы устройство обладает возможностью работы в реальном времени. 2 ил.

>8nrnS6

35

45

Изобретение относится к вычислитель ной технике и технической кибернетике и может быть использовано в системах корреляционного распознавания изображений или я устройствах обработки и распознавания одномерных сигналов.

Цель изобретения — повышение быстродействия и расширение области применения за счет возможности одновременного вычисления максимума, минимума, медианы из трех m-разрядных чисел, а также их суммы.

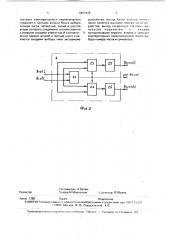

На фиг,1 представлена структурная схема устройства для вычисления экстремумов; на фиг.2 — структурная схема компараторного переключателя.

Устройство для вычисления экстремумов содержит первый 1, второй 2 и третий 3 входные регистры, первый 4 и второй 5 коммутаторы, первый 6, второй 7 и третий 8 компараторные переключатели, первую 9.1, вторую 9,2 и третью 9.3 группы задержки, первый 9.4, второй 9.5 и третий 9.6 элементы задержки, первую 10,1, вторую 10.2 и третью 10.3 группы элементов И, селектор

11 номера числа, сумматор 12 и генератор тактовых импульсов (ГТИ) 13.

На фиг,1 показаны также первый 14, второй 15 и третий 16 информационные входы устройства, вход 17 выбора кода устройства, выход 18 наращивания устройства, вход 19 выбора типа экстремума, первый 20

-и второй 21 выходы устройства.

Компараторный переключатель содержит компаратор 22, третий 23 и четвертый

24 коммутаторы (мультиплексоры), первый

25 и второй 26 регистры-фиксаторы.

Формула изобретения

Устройство для вычисления экстремумов, содержащее группу элементов И, компараторный переключатель. первый входной регистр и генератор тактовых импульсов, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия и расширения области применения за счет возможности одновременного вычисления максимума, минимума. медианы из трех mразрядных чисел, а также их суммы, в него введены второй и третий входные регистры, первый и второй коммутаторы, второй и третий компараторные переключатели. три группы элементов задержки, три элемента задержки, вторая и третья группы элементов И, блок выбора номера числа. выполненный на ПЗУ. и сумматор, причем первый информационный вход устройства соеди нен с информацинными входами первого входного ppf истра. а второй и третий инфор мационные входы устройства соединень с информационными входами первых групп соответственно парвоiо и ятороiо квммута торов. выходы которых подклю гены к информационным входам соответственно второго и третьего входных регистров. а информационные входы вторых групп коммутаторов соединены соответственно с выходами разрядов первого входного регистра соединенными с входами элементов задержки первой группы и с выходами разрядов второго входного регистра, соединенными с входами первой группы первого компараторного переключателя, входы второй группы которого соединены с выходами разрядов третьего входного регистра и выходами наращивания устройства, вход выбора кода которого подключен к управляющим входам первого и второго коммутаторов, выходы элементов первой группы задержки соединены с входами первой группы второго компараторного переключателя, информационные выходы первой группы которого соединены с входами элементов задержки второй группы, выходы которых соединены с первыми входами элементов И первой группы, выходы которых соединены с входами первой группы сумматора, информационные выходы первой группы первого компараторного переключателя соединены с входом второй группы второго компараторного переключателя. информационные выходы второй группы которого соединены с входами первой группы третьего компараторного переключателя, информационные выходы первой группы которого соединены с первыми входами элементов И второй группы, выходы которых соединены с входами второй группы сумматора, информационные выходы второй группы первого компараторного переключателя соединены с входами элементов задержки третьей группы, выходы которых соединены входами второй группы третьего компараторного переключателя, информационные выходы второй группы которого соединены с первыми входами элементов И третьей группы, выходы которых соединены с входами третьей группы сумматора, выходы которого являются выходами экстремума устройства, выход результата сравнения первого компараторного переключателя соединен с входом первого элемента задержки, выход которого соединен с входом второго элемента задержки, выход которого соединен с первым входом блока выбора номера числа, выход результата сравнения второго компараторного переключателя соединен с входом третьего элемента задержки, выход которо го соединен с вторым входом блока выбора номера числа, выход результата сравнения

1807476

B хр

Sro82 ко< Я

Составитель А,Батюк

Редактор Техред М.Моргентал Кзвректор И,Шулла

Заказ 1380 Тираж Подписное

ВНИИГ1И Государ, венного комитета по изобретениям и открытиям при ГКНТ СС(..Р

113035. Москва. Ж-35. Раушская наб., 4/5

Производственно нздмельскпй комбинат "Патент". r. Ужгород ул.Гагарина, 101 третьего компараторного переключателя гоединен с третьим входом блока выбора номера числа, четвертый, пятый и шестой входы которого соединены соответственно с вторыми входами элементов И соответственно первой, второй и третьей групп и являются входами выбора типа экстремума устройства, выход блока выбо1;а н н рл числа является выходом номерэ числа у л ройства, выход генератора rar nr t v импульсов подключен к входам

5 синхронизации первого. второй и третьего компараторных переключателей. блока выбора номера числа и сумматора.