Буферное запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и автоматике и может быть использовано в различных устройствах обработки и передачи информации. Целью изобретения является упрощение устройства . Устройство предназначено для буферного запоминания входной информации и выдачи на устройства обработки (накопления) при согласовании скоростей работы входных и выходных устройств. Устройство содержит блок памяти, дешифратор записи, дешифратор считывания, счетчик адреса записи , счетчик адреса считывания, блок сравнения для управления разрешением записи - считывания, первый и второй элементы И, первый и второй элементы И-НЕ, RS-триггер, соответствующие связи. За счет введения элементов И-НЕ, RS-триггера и новых связей удалось исключить из схемы устройства счетчик и схему сравнения, являющиеся более сложными устройствами, чем введенные в элементы И-НЕ и RS-триггер. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51) 5 G 1 1 С 19/00

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) ОПИСАНИЕ ИЗОБРЕТЕНИЯ, К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4920622/24 (22) 05.02.91 (46) 07.04.93. Бюл, N 13 (71) Центральный научно-исследовательский институт "Комета" (72) А, В, Куренной и И. B. Пахомов (56) Авторское свидетельство СССР

N 1550585, кл, G 11 С 19/09, 1988.

Авторское свидетельство СССР

N 1544031, кл, 6 11 С 19/00, 1988. (54) БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО (57) Изобретение относится к вычислительной технике и автоматике и может быть использовано в различных устройствах обработки и передачи информации. Целью изобретения является упрощение устройстИзобретение относится к импульсной и вычислительной технике и может быть использовано в различных устройствах обработки и передачи информации.

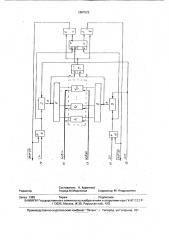

Целью изобретения является упрощение схемы устройства, На чертеже приведена функциональная схема устройства, Буферное запоминающее устройство содержит блок 1 накопителя, счетчик 2 адреса считывания, счетчик 3 адреса записи, элементы И вЂ” НЕ 4 и 8, дешифраторы 5 и 6 адресов считывания и записи, схему 7 сравнения; элементы 9 и 10 совпадения, RS-триггер 11, шину установки 12, шину 13 данных записи, шину

14 данных считывания, шину 15 управления записью, шину 16 управления считыванием и соответствующие связи.

„.,5U „„1807522 А1 вэ. Устройство предназначено для буферного запоминания входной информации и выдачи нэ устройства обработки (накопления) при согласовании скоростей работы входных и выходных устройств, Устройство содержит блок памяти, дешифратор записи, дешифратор считывания, счетчик адреса записи, счетчик адреса считывания, блок сравнения для управления разрешением записи — считывания, первый и второй элементы И, первый и второй элементы И вЂ” НЕ, RS-триггер, соответствующие связи. За счет введения элементов И вЂ” НЕ, RS-триггера и новых связей удалось исключить из схемы устройства счетчик и схему сравнения, являющиеся более сложйыми устройствами, чем введенные в элементы И вЂ” НЕ и RS-триггер. 1 ил.

Буферное запоминающее устройство работает следующим образом, Перед началом работы по шине 12 поступает импульс установки, обнуляющий счетчи- О© ки 2 и 3 и устанавливающий триггер 11 в и0н —, C) состояние, при котором на прямом выходе— низкий потенциал, на выходе "=" схемы срав- (Л нения 7- высокий уровень напряжения и на в) выходе элемента 4 — низкий уровень и, следовательно, чтение запрещено.

Запись высоким уровнем на выходе алемента 8 разрешена.

При приходе импульса записи счетчик 3 изменяет свое состояние и на выходе схемы

7 — нйзкий уровень, который разрешает и запись, и считывание. При количестве чтений, равном количеству записей, чтение опять запрещается. В ситуации, когда чтение отсутствует, а происходит только за1807522 пись. т.е, буфер заполняется при появлении на выходе схемы 7 высокого уровня, происходит запрет записи высоким уровнем с прямого выхода триггера 11. В остальном функционирование аналогично прототипу.

Таким образом, при сохранении функционирования устройства схемная реализация проще. чем в прототипе.

Формула изобретения

Буферное запоминающее устройство, содержащее блок памяти, дешифратор записи, дешифратор считывания, первый и, второй элементы И, блок сравнения, счетчик адреса записи и счетчик адреса считывания, причем входы установки счетчика адреса записи и счетчика адреса считывания объединены. и являются входом установки устройства, входы дешифратора записи и входы первой группы блока сравнения объединены и подключены к выходу счетчика адреса записи, счетный вход которого соединен с выходом первого элемента И, первый и второй входы которого являются соответственно входом записи устройства и входом запрета записи устройства, выходы дешифратора записи соединены с соответствующими адресными входами записи блока памяти информационные входы которого являются информационными входами устройства, информационными выходами которого являются выходы блока памяти, адресные входы считывания которого соединены с соответствующими выходами дешифратора считывания, входы которого и входы второй группы блока сравнения объединены и подключены к соответствующим выходам счетчика адреса считывания, счетный вход которого соединен с выходом второго элемента И, первый и второй входы которого

1О являются соответственно входом считывания устройства и входом запрета считывания устройства, отличающееся тем,что,сцелью упрощения устройства, в него введены первый и второй элементы И-НЕ и RS-триггер, "5 первый вход сброса которого соединен с входом установки устройства, счетный вход счетчика адреса считывания соединен с вторым входом сброса RS-триггера, вход установки которого Соединен со счетным входом счетчика адреса записи, прямой выход RS-триггера соединен с первым входом первого элемента И вЂ” НЕ, второй вход которого и второй вход второго элемента И-НЕ объединены и подключены к выходу блока сравнения, вы25 ход первого элемента И-НЕ соединен с вторым входом первого элемента И, второй вход второго элемента И соединен с выходом второго элемента И вЂ” НЕ, первый вход которого соединен с инверсным выходом

ЗО RS-триггера.

1807522

Составитель А, Куренной

Техред М,Моргентал Корректор М. Андрушенко

Редактор

Производственно-издательский комбинат "Патент", г Ужгород, ул. Гагарина, 101

Заказ 1383 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Mocxsa, Ж-35, Раушская наб„4/5