Буферное запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использовано в различных устройствах автоматики и вычислительной техники. Цель изобретения - упрощение устройства. Устройство отличается простотой схемного решения за счет упрощения блоков сравнения и уменьшения числа связей между элементами. Устройство предназначено для согласования скоростей передающего и принимающего информацию устройств. Буферное запоминающее устройство содержит блок памяти, дешифратор записи , дешифратор считывания, счетчик адреса считывания, счетчик адреса записи, счетчик адреса считывания, счетчик управления , первый и второй элементы И, первый и второй бло.ки сравнения. 1 ил.

i 1К iз r < Г11 .ktIX (:О(Ц1А ПИ 1И IF < .КИХ

РГСFIYF IÈÊ

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4925672/24 (22) 18.01.91 (46) 07.04.93. Бюл. ¹ 13 (71) Центральный научно-исследовательский институт "Комета" (72) А. В. Куренной и И. В. Пахомов (56) Авторское свидетельство СССР

N 1550585, кл, 6 11 С 19/00, 1988.

Авторское свидетельство СССР

N 1547031, кл. G 11 С 19/00, 1988. (54) БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО (57) Изобретение относится к импульсной технике и может быть использовано в разИзобретение относится к импульсной технике и может быть использовано в различных устройствах автоматики и вычислительной техники.

Цель изобретения — упрощение схемы устройства за счет уменьшения числа связей.

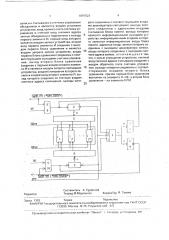

На чертеже приведена функциональная схема устройства.

Устройство содержит блок 1 памяти, счетчики адресов считывания 2 и записи, счетчик 4 управления (реверсивный), дешифраторы адресов считывания 5 и записи 6, блоки сравнения 7 (все "0") и 8 (все "1"), элементы И 9 и 10 и соответствующие связи.

Буферное запоминающее устройство работает следующим образом, Перед началом работы импульс по шине

"УСТ" приводит счетчики 2-4 в нулевое состояние, что приводит к появлению на выходе блока 7 низкого, запрещающего считывание уровня, а на выходе блока 8—..5U,«, 1807523 А1 личных устройствах автоматики и вычислительной техники. Цель изобретения — упрощение устройства. Устройство отличается простотой схемного решения за счет упрощения блоков сравнения и уменьшения числа связей между элементами. Устройство предназначено для согласования скоростей передающего и принимающего информацию устройств. Буферное запоминающее устройство содержит блок памяти, дешифратор записи, дешифратор считывания, счетчик адреса считывания. счетчик адреса записи, счетчик адреса считывания, счетчик управления, первый и второй элементы И, первый и второй блоки сравнения. 1 ил, высокого, разрешающего запись уровня.

Таким образом разрешается запись в блок памяти. При приходе записывающих и считывающих импульсов счетчик 4 следит за тем, чтобы его состояние не было равно "0" (буфер пуст) или все разряды не были равны QQ

"1", что указывает на переполнение буфера, (. при этом срабатывает блок 8, вырабатывая на выходе низкий уровень запрета записи. (Л

Таким образом, при сохранении функционального назначения буферное запоминающее устройство имеет более простую схемную реализацию.

Формула изобретения

Буферное запоминающее устройство, содержащее блок памяти, дешифратор записи, дешифратор считывания, счетчик адреса записи, счетчик адреса считывания.. счетчик управления, первый и второй элементы И, первый и второй блоки сравнения, причем входы установки счетчиков адреса

180 t523

Г и

Составитель А, Куренной

Техред М.Моргентал Корректор Н, Гунько

Редактор

Заказ 1383 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб.. 4/5

Производственно-издательский комбинат "Патент". г Уж ород, ул.Гагарина, 10 записи и считывания и счетчика управления объединены и являются входом установки устройства, вход прямого счета счетчика управления и счетный вход счетчика адреса записи объединены и подключены к выходу первого элемента И, первый вход которого является входом записи устройства, второй вход первого элемента И соединен с выходом первого блока сравнения и является входом запрета записи устройства, входы. "0 первого блока сравнения соединены с соответствующими выходами счетчика управления, выход второго блока сравнения соединен с первым входом второго элемен,та И и является входом запрета считывания 15, устройства, входом считывания которого является второй вход второго элемента И, выход которого соединен со счетным входом счетчика адреса считывания, выходы кото20 рого соединены с соответствующими входами дешифратора считывания, выходы которого соединены с адресными входами считывания блока памяти, выходы которого являются информационными выходами устройства, информационными входами которого являются информационные входы блока памяти, адресные входы записи которого соединены с выходами дешифратора записи, входы которого соединены с выходами счетчикаадресазаписи, отличающееся тем, что, с целью упрощения устройства, счетный вход счетчика адреса считывания соединен с входом обратного счета счетчика управления, выходы которого соединены с соответствующими входами второго блока сравнения, причем первый блок сравнения выполнен на элементе И вЂ” НЕ, а второй блок сравнения — на элементе ИЛИ,