Устройство для обнаружения симметричных сигналов

Иллюстрации

Показать всеРеферат

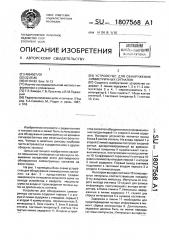

Сущность изобретения: устройство содержит 3 линии задержки 1, 2 и 11, 2 коммутатора 3 и 4, 1 перемножитель 5, 1 интегратор 6,1 блок памяти 7, 1 блок взятия отсчета 8, 1 тактовый генератор 9, 1 счетчик 10, 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 Н 04 В 1/10

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) 11 / чЭ! г;М

F - -k-, ".--- -".Эт H p 1

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCКОМУ СВИДЕТЕЛЬСТВУ (21) 4694507/09 (22) 22.05.89 (46) 07.04,93. Бюл. ¹ 13 (71) Научно-исследовательский институт информатики и управления (72) Т.Е.Замора, Г.В.Лукьянец и В.M.Ïîäæàрый (56) Радиотехнические цепи и сигналы /Под ред. К.А,Самойло, М.: Радио и связь, 1987, с. 518.

Изобретение относится к радиотехнике и технике связи и может быть использовано для обнаружения симметричных во времени сигналов {четных или нечетных) на фоне помех. Четные и нечетные сигналы наиболее часто встречаются в радиотехнике и других областях техники

Целью настоящего изобретения является повышение отношения сигнал-шум и повышение вследствие этого достоверности обнаружения симметричных сигналов на фоне помех.

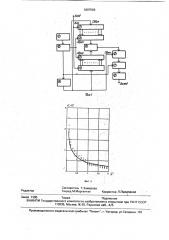

На фиг. 1 приведена блок-схема устрой; ства для обнаружения симметричных сигналов; на фиг. 2 — представлен график зависимости отношения мощности шума на выходе устройства к квадрату мощности шума на входе от произведения полосы шума на длительность сигнала, Устройство для обнаружения симметричных сигналов содержит первую 1 и вторую 2 линии задержки с отводами, первый 3 и второй 4 коммутаторы, перемножитель 5, интегратор 6, блок памяти 7, блок 8 взятия отсчета, тактовый генератор 9, счетчик 10 и третью линию задержки 11. Входом устройЯ2 1807568 А1 (54) УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ

СИММЕТРИЧНЫХ СИГНАЛОВ (57) Сущность изобретения: устройство содержит 3 линии задержки 1, 2 и 11, 2 коммутатора 3 и 4, 1 перемножитель 5, 1 интегратор 6, 1 блок памяти 7, 1 блок взятия отсчета 8, 1 тактовый генератор 9, 1 счетчик

10,2 ил. ства являются обьединенные информацион- ) ные входы первой 1 и второй 2 линий задержки. Выходом устройства является выход блока 8 взятия отсчета. На входы первой 1 и второй 2 линий задержки поступает входной сигнал, дискретизированный во времени.

Тактовый генератор 9 вырабатывает тактовые импульсы, поступающие не вход счетчика 10. Коэффициент пересчета N счетчика 10 равен количеству отводов первой 1 и второй 00

2 линий задержки. Первый выход счетчика С) подключен к тактовым входам первого 3 и второго 4 коммутаторов. Ql

На втором выходе счетчика 10 генериру- 0 ются импульсы .соответствующие каждому Ор

N-му входному импульсу, Импульсы со второго выхода счетчика 10 служат для записи информации, поступающей с выхода интегратора, в блоке памяти 7. Импульсы, задер-жанные в линии задержки 11, служат для сброса интегратора 6 в нулевое состояние.

Задержка в линии 11 необходима для предотвращения потери информации в момент сброса интегратора 6. Длительность задержки должна быть не менее периода тактовых импульсов. Импульсы с выхода ли1807568 нии задержки 11 служат для сдвига входной информации в первой 1 и второй 2 линиях задержки. За время между импульсами, поступающими на тактовые входы линий задержки 1 и 2, происходит опрос всех отводов . линий задержки коммутаторами 3 и 4.

Таким образом на входы перемножителя поступает информация со всех выходов линий задержки 1 и 2, причем, благодаря тому, что первый 3 коммутатор подключен к входам первой 1 линии задержки в прямом порядке, а второй 4 коммутатор подключен к входам второй 2 линии задержки в обратном порядке; на выходе интегратора 6 формируется сигнал, аналогичный све )тке в конечных пределах: ь

Sn(I,k) I1/N)* (S(-k)*S {- +k), (1)

k=1 где St — входной сигнал; .

Я(— сигнал на выходе перемножителя;

1 — номер отсчета входного сигнала;

k = О...N — индекс суммы, определяемый адресом коммутаторов 3 и 4, поступающим иэ счетчика 1,0, N — Число отсчетоЬ, хранящихся в линиях задержки 1 и 2.

Интегратор„б. прбизводит вычисление . среднего значения произведения входных отсчетов по индексу k. Окончательное зна-. чение суммы на выМде интегратора 10 запоминается в блоке памяти 7. Блок 8 взятия отсчета служйт/ для определения момента

: доьс/тижения сигналом максимума и запоминания этого значения.

Если время появления сигнала известно; то в качесгве блока 8 может быть исполь зовано устройство выборки хранения.

Если в/ремя появления сигнала не извест. но, то в качестве блока,8 может использо-. ваться пороговое устройство. При этом порог устанавливается, исходя из требуейых статистических параметров обнаружения.

Устройство. для обнаружения может быть выполнено на элементах цифровой или комбинированной аналого-цифровой техники. Коэффициент перерасчета N счетчика 10

50 линий задержки. и частота ft тактового генератора 9 определяется из следующих соотношений:

N - Tc/tg, (2)

tg = N/ft 1/2fo (3) где Тс — длительность сигнала;

tg — время дискретизации сигнала;

4 — максимальная частота спектра сигнала.

Выбрав tg из условия (3),опререляем N из

10 соотношения (2) и находим ft - N /Tc Например f() = 1 кГц, Т - 1 мс, тогда tg <0,5 мс, Примем tg = 0,1 мс, отсюда N = 10, ft = 50, кГц.

Применение дополнительных узлов и связей между ними выгодно отличает пред15. лагаемое устройство для обнаружения симметричных сйгналов- от устройства прототипа, т.к. пбзцоляет повысить отноше.ние сигнал-шум, а значит улучшить достоверность обнаружения сигналов.

Формула изобретения

Устройство для обнаружения симметрйчных сигналов, содержащее блок взятия отсчета, перемножитель, выход которого со- един/ен с первйм входом uHierðaòoðà, о т - .

25 л и и а ю щ е е с я тем, что, с целью йовышения достоверности обнаружения симметричных сигналов, введены три линий задержки, два коммутатора, блок памяти, : счетчик и тактовый генератор, выход «ото30 рого соедийен с входом счетчика, первый вйход которого соединен с тактовыми входами первого и второго коммутаторов, выходы которйх подключены соответственно к первому и второму входам перемножителя, 35 при этом второй выход счетчика соединен с тактовым. входом блока памяти и с входом третьей линии задержки, выход которой соединен с тактовым входом интегратора и с тактовыми входами первой и второй линий

40 задержки, выходы которых подключены к информационйым входам соответствейно первого и второго коммутаторов, выход интегратора соединен с информационным входом блока памяти, выход которого под45 ключен к входу блока взятия отсчета, выход которога является выходом устройства, входом которого являются объединенные информационные входы первой и второй

1807568 д Л

05 фиг 2

Составитель Т,Заморова

Техред M. Моргентал Корректор Л.Пилипенко

Редактор

Производственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарина, 101

Заказ 1385: Тираж Подписное, ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5