Устройство синхронизации по циклам

Иллюстрации

Показать всеРеферат

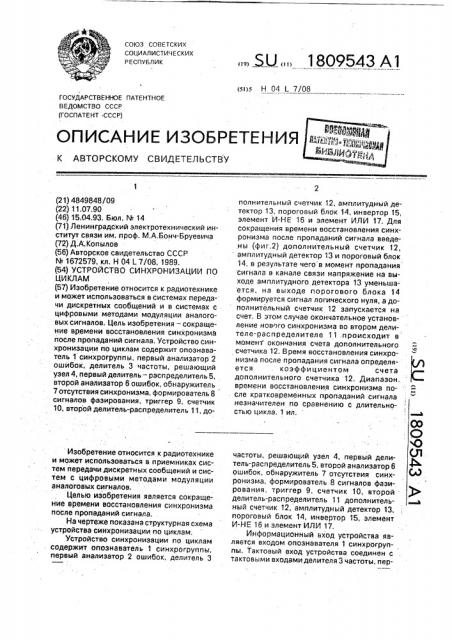

Изобретение относится к радиотехнике и может использоваться в системах передачи дискретных сообщений и в системах с цифровыми методами модуляции аналоговых сигналов. Цель изобретения -сокращение времени восстановления синхронизма после пропаданий сигнала. Устройство синхронизации по циклам содержит опознаватель 1 синхрогруппы, первый анализатор 2 ошибок, делитель 3 частоты, решающий узел 4, первый делитель - распределитель 5, второй анализатор 6 ошибок, обнаружитель 7 отсутствия синхронизма, формирователь 8 сигналов фазирования, триггер 9, счетчик 10, второй делитель-распределитель 11, доИзобретение относится к радиотехнике и может использоваться в приемниках систем передачи дискретных сообщений и систем с цифровыми методами модуляции аналоговых сигналов. Целью изобретения является сокращение времени восстановления синхронизма после пропаданий сигнала. На чертеже показана структурная схема устройства синхронизации по циклам, Устройство синхронизации по циклам содержит опознаватель 1 синхрогруппы, первый анализатор 2 ошибок, делитель 3 полнительный счетчик 12, амплитудный детектор 13, пороговый блок 14, инвертор 15, элемент И-НЕ 16 и элемент ИЛИ 17. Для сокращения времени восстановления синхронизма после пропаданий сигнала введе- .ны (фиг.2) дополнительный счетчик 12, амплитудный детектор 13 и пороговый блок 14, в результате чего в момент пропадания сигнала в канале связи напряжение на выходе амплитудного детектора 13 уменьшается , на выходе порогового блока 14 формируется сигнал логического нуля, а дополнительный счетчик 12 запускается на счет. В этом случае окончательное установление нового синхронизма во втором делителе-распределителе 11 происходит в момен-f окончания счета дополнительного счетчика 12. Время восстановления синхронизма после пропадания сигнала определяетсякоэффициентом счета дополнительного счетчика 12. Диапазон, времени восстановления синхронизма после кратковременных пропаданий сигнала незначителен по сравнению с длительностью цикла. 1 ил. частоты, решающий узел 4, первый делитель-распределитель 5, второй анализатор 6 ошибок, обнаружитель 7 отсутствия синхронизма , формирователь 8 сигналов фазирования , триггер 9, счетчик 10, второй делитель-распределитель 11 дополнительный счетчик 12, амплитудный детектор 13. пороговый блок 14, инвертор 15, элемент И-НБ 16. и элемент ИЛИ 17. Информационный вход устройства является входом опознавателя 1 синхрогруппы . Тактовый вход устройства соединен с тактовыми входами делителя 3 частоты, перел с 00 о ю ел N СО

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (st)s Н 04 1 7/08

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

В (21) 4849848/09 (22) 11.07.90 (46) 15.04,93. Бюл. ¹ 14 (71) Ленинградский электротехнический институт связи им. проф. М,А,Бонч-Бруевича (72) Д,А .Копылов (56) Авторское свидетельство СССР № 1672579, кл. Н 04 7/08, 1989. (54) УСТРОЙСТВО СИНХРОНИЗАЦИИ ПО

ЦИКЛАМ (57) Изобретение относится к радиотехнике и может. использоваться в системах передачи дискретных сообщений и в системах с цифровыми методами модуляции аналоговых.сигналов. Цель изобретения — сокращение времени восстановления синхронизма после пропаданий сигнала. Устройство синхронизации по циклам содержит опознаватель 1 синхрогруппы, первый анализатор 2 ошйбок, делитель 3 частоты, решающий узел 4, первый делитель — распределитель 5, второй анализатор 6 ошибок, обнаружитель

7 отсутствия синхронизма, формирователь 8 сигналов фаэирования, триггер 9, счетчик

10, второй делитель-распределител ь 11, доИзобретение относится к радиотехнике и может использоваться в приемниках систем передачи дискретных сообщений и систем с цифровыми методами модуляции аналоговых сигналов.

Целью изобретения является сокращение времени восстановления синхронизма после пропаданий сигнала.

На чертеже показана структурная схема устройства синхронизации по циклам, Устройство синхронизации по циклам содержит опознаватель 1 синхрогруппы, первый анализатор 2 ошибок, делитель 3

„„50 ÄÄ 1809543 А1 полнительный счетчик 12, амплитудный детектор 13, пороговый блок 14, инвертор 15, элемент И-НЕ 16 и элемент ИЛИ 17. Для сокращения времени восстановления синхронизма после пропаданий сигнала введены (фиг,2) дополнительный счетчик 12, амплитудный детектор 13 и пороговый блок

i4, в результате чего в момент пропадания сигнала в канале связи напряжение на выходе амплитудного детектора 13 уменьшается, на выходе порогового блока 14 формируется сигнал логического нуля, а дополнительный счетчик 12 запускается на счет. В этом случае окончательное установление нового синхронизма Во втором делителе-распределителе 11.происходит в момент окончания счета дополнительного счетчика 12. Время восстановления синхронизма после пропадания сигнала определяется коэффициентом счета дополнительного счетчика 12. Диапазон. времени восстановления синхронизма после кратковременных пропаданий сигнала незначителен по сравнению с длительностью цикла, 1 ил. частоты, решающий узел 4, первый делитель-распределитель 5, второй анализатор 6 ошибок, обнаружитель 7 отсутствия синхронизма, формирователь 8 сигналов фазирования, триггер 9, счетчик 10, второй делитель-распределитель 11 дополнительный счетчик 12, амплитудный детектор 13, пороговый блок 14, инвертор 15, элемент

И-НЕ 16 и элемент ИЛИ 17, Информационный ьход устройства является входом опознавателя 1 синхрогруппы. Тактовый вход устройства соединен с тактовыми входами делителя 3 частоты, пер1809543 вого и второго делителей-распределителей

5, 11, счетчика 10 и дополнительного счетчика 12. Дополнительный вход устройства является входом амплитудного детектора 13, Выход опознавателя 1 синхрогруппы соединен с первыми входами. первого и второго анализаторов 2, 6 ошибок. Первый и второй выходы первого анализатора 2 ошибок соединены, соответственно, с первым и вторым входами делителя 3 частоты, а также, соответственно, с первым и вторым входами решающего узла 4. Первый выход решающего узла 4 соединен с управляющим входом делителя 3 частоты. Второй выход решающего узла 4 соединен с первым входом формирователя 8 сигналов фазирования. Выход декителя 3 частоты соединен со вторым входом первого анализатора 2 ошибок и со вторым входом формирователя 8 сигналов фазирования. Первый и второй выходы вто- 20 рого анализатора 6 ошибок соединены, соответственно, с первым и вторым входами обнаружителя 7 отсутствия синхронизма.

Выход обнаружителя 7 отсутствия синхро-низма соединен с установочным входом триггера 9 и первым входом элемента И-Н Е

16. Выход элемента И-НЕ 16 соединен с управляющим входом счетчика 10. Выход счетчика 10 соединен с первым входом элемента ИЛИ 17, Выход триггера 9 соединен 30 с третьим входом формирователя 8 сигналов фазирования. Первый выход формирователя 8 сигналов фазирования соединен со входами сброса обнаружителя 7 отсутствия синхронизма и триггера 9. Второй выход 35 формирователя 8 сигналов фазирования соединен с установочным входом первого де лителя-распределителя 5. Первый выход первого делителя-распределителя 5 соединен со вторым входом второго анализатора 40

6 ошибок и с четвертым входом формирователя 8 сигналов фазирования. Остальные выходы первого делителя-распределителя 5 соединены с соответствующимй установочными входами второго делителя-распреде- 45 лителя 11. Выход амплитудного детектора

13 соединен со входом порогового устройства 14. Выход порогового устройства 14 .. соединен с управляющим входом дополнительного счетчика 12. Выход дополнитель- 50 ного счетчика 12 соединен со входом инвертора 15 и со вторым входом элемента

ИЛИ 17. Выход инвертора 15 соединен со вторым входом элемента И-HE 16. Выход элемента ИЛИ 17 соединен с управляющим 55 входом второго делителя-распределителя

11, Выход второго делителя-распределителя 11 является выходом устройства.

Устройство синхронизации по циклам работает следующим образом, Считаем, что для обеспечения синхронизации по циклам приемного устройства в передающем устройстве в каждом цикле. состоящем из N тактов, на одних и тех же позициях цикла формируется сосредоточенная синхрогруппа фиксированного состава. На информационный вход устройства поступает последовательный цифровой информационный код с введенными в него синхрогруппами с выхода демодулятора. На выходе опознавателя 1 синхрогруппы образуются сигналы откликов как на синхрогруппу, так и на кодовые группы информационного сигнала, сходные с синхрогруппой. Эти сигналы откликов поступают на первые входы первого и второго анализаторов 2, 6 ошибок, на вторые входы которых подаются.сигналы опробования с выходов, соответственно, делителя 3 частоты и первого делителя-распределителя 5. Каждый из анализаторов 2, 6 ошибок вырабатывает на своем первом выходе сигнал правильного приема в случае, когда сигнал опробования совпадает по времени с откликом опознавателя 1 синхрогруппы. Если в момент прихода сигнала опробования сигнал отклика опознавателя 1 синхрогруппы отсутствует, то в этот момент на втором выходе соответствующего анализатора 2 или 6 ошибок формируется сигнал ошибки.

Первый анализатор 2 ошибки, деЛитель

3 частоты и решающий узел 4 служат для быстрого обнаружения отсутствия синхронизма, поиска и фиксации нового состояния синхронизма. При приходе подряд некоторого небольшого числа сигналов ошибки с выхода первого анализатора 2 ошибок решающий узел 4 переходит в режим поиска синхронизма и формирует на своем первом выходе управляющий сигнал, разрешающий управление делителем 3 частоты сигналами с выхода первого анализатора 2 ошибок. В этом случае остановка делителя

3 частоты осуществляется по первому сигналу ошибки, а запуск — по первому сигналу правильного приема синхрогруппы, После нахождения делителем 3 частоты нового состояния синхронизма и прихода подряд некоторого небольшого числа сигналов правильного приема синхрогруппы решающий узел 4 переходит в режим фиксации состояния синхронизма и формирует на своем первом выходе управляющий сигнал, обеспечивающий безостановочную работу делителя 3 частоты, а также, на своем втором выходе, сигнал, подготавливающий формирователь 8 сигналов фазирования к сравнению фаз делителя 3 частоты и пегвого делителя-распределителя 5.

1809543

20

30 своем втором выходе сигнал, производя- 35 щий установку фазы первого делителя-рас40

На входы обнаружителя 7 отсутствия синхронизма приходят сигнал правильного приема и сигнал ошибки с выходов второго анализатора 6 ошибок, На выходе обнаружителя 7 отсутствия синхронизма формируется сигнал отсутствия синхронизма положительной полярности, когда на его вход поступит подряд M сигналов ошибки, Сигналом отсутствия синхронизма триггер

9 устанавливается в положение, разрешающее сравнение фаз делителя 3 частоты и первого делителя-распределителя 5 в формирователе 8 сигналов фазирования. Кроме этого, в случае, когда на выходе инвертора

15 присутствует сигнал логической единицы, положительный сигнал отсутствия синхронизма на первом входе элемента И-НЕ 16 приводит к формированию на его выходе сигнала логического нуля, которым запускается на счет счетчик 10.

При установленном триггере 9 и при наличии на втором выходе решающего узла

4 сигнала, подготавливающего формирователь 8, сигналов фазирования, формирователь 8 сигналов фазирования осуществляет сравнение фаз делителя 3 частоты и первого делителя-распределителя

5, формируя в этот момент на своем первом выходе сигнал, осуществляющий сброс триггера 9 и обнаружителя 7 отсутствия синхронизма, Кроме этого, в случае расхо>кдения фаз делителя 3 частоты и первого делителя-распределителя 5, формирователь 8 сигналов фаэирования формирует на пределителя 5 в соответствии с фазой делителя 3 частоты, После запуска счетчика 10 сигналом отрицательной полярности с выхода элемента

И-НЕ 16 счетчик 10 начинает считать импульсы тактовой частоты и формирует в это время на своем выходе сигнал логической единицы. По истечении К тактовых интервалов счетчик 10 прекращает счет и формирует на своем выходе сигнал логического нуля, оставаясь в этом состоянии вплоть до прихода следующего запускающего сигнала.

На дополнительный вход устройства поступает сигнал непосредственно с выхода канала связи. Амплитудный детектор 13 формирует на.своем выходе сигнал высокого напряжения, когда сигнал на выходе канала связи присутствует, и сигнал низкого напряжения, когда в канале связи происходят пропадания сигнала. Пороговое устройство 14 сравнивает напряжение на своем входе с пороговым уровнем, равным примерно полусумме максимального и минимального значений входного напряжения, 45

При превышении входным наг1ряжени-.м порогового уровня на выходе порогового устройства 14 формируется сигнал логической единицы, в противном случае — сигнал логического нуля, Поэтому когда сигнал в канале связи присутствует . выходной сигнал порогового устройства 14 — логическая единица, а в момент пропадания сигнала-логический ноль. При приходе на управляющий вход дополнительного счетчика 12 сигнала логического нуля он начинает считать импульсы тактовой частоты и формирует в это время на своем выходе сигнал логической единицы. По истечении L тактовых интервалов дополнительный счетчик 12 прекращает счет и формирует на своем выходе сигнал логического нуля, оставаясь в этом состоянии вплоть до прихода следующего запускающего сигнала. Когда на выходе дополнительного счетчика 12 присутствует сигнал логической единицы, нулевой сигнал на выходе инвертора 15 запрещает счетчику 10 переходить в режим счета. На выходе элемента ИЛИ 17 формируется сигнал логической единицы, когда хотя бы один из счетчиков 10, 12 находится в режиме счета и формирует на своем выходе сигнал логической единицы.

Второй делитель-распределитель 11, при приходе нулевого управляющего сигнала с выхода элемента ИЛИ 17, игнорирует сигнал тактовой частоты, а пропускает на свой выход сигналы с установочных входов, т,е, сигналы с выходов первого делителяраспределителя 5. При поступлении логической единицы на управляющий вход второго делителя-распределителя 11 он игнорирует сигналы установочных входов, а продолжает считать импульсы тактовой частоты, начиная с того состояния (той фазы), которое было записано с установочных входов перед переходом управляющего сигнала из нуля в единицу, В засинхронизированном режиме, когда сигналы опробования делителя 3 частоты и первого делителя-распределителя 5 cosпадают по времени с откликами опознанателя 1 синхрогруппы, а ошибки и пропадания сигнала в канале связи отсутствуют, анализаторы 2 и 6 ошибок формируют только сигналы правильного приема. В этом случае решающий узел 4 находится в режиме фиксации синхронизма, обнаружитель 7 отсутствия синхронизма и триггер 9 находятся в сброшенном состоянии, формирователь 8 сигналов фазирования не производит сравнение фаз делителя 3 час1оты и первого делителя-распределителя 5, счетчики 10, 12 остановлены и формируют на своих выходах сигналы логического нуля, в результате чего

1809543

25

50

55 зи. фаза второго делителя-распределителя 11 все время совпадает с фазой первого делителя-распределителя 5 и совпадает с истинной цикловой фазой, Если в засинхронизированном режиме из-за ошибок в канале связи некоторые синхрогруппы оказываются искаженными, то анализаторы 2 и б ошибок выдают в эти моменты сигналы ошибок, и решающий узел 4 может перейти в режим поиска синхронизма и заставить делитель 3 частоты останавливаться первым сигналом ошибки и запускаться на счет первым сигналом правильного приема. Однако в этом случае неправильная установка делителей-распределителей 5, 11 черезвычайно маловероятна. поскольку для этого необходимо одновременное выполнение двух независимых маловероятных условий, Во-первых, для обнаружения отсутствия синхронизма в обнаружителе 7 отсутствия синхронизма, необходимо, чтобы искаженными оказались M синхрогрупп подряд, Вовторых, решающий узел 4 должен зафиксировать неправильное состояние синхронизма, то есть в информационном сигнале в нескольких циклах подряд на одних и тех же позициях цикла должны сформироваться группы сигнала, сходные с синхрогруппой.

Если обнаружитель 7 отсутствия синхронизма не вырабатывает сигнал отсутствия синхронизма, то, независимо от работы решающего узла 4 формирователь 8 сигналов фазирования не производит сравнение фаз делитегя 3 частоты и первого делителяраспределителя 5, в результате чего первый делитель-распределитель 5 остается в режиме правильного синхронизма, а счетчик

10 при этом на счет не запускается, Если при этом отсутствуют пропадания сигнала в канале связи, то дополнительный счетчик 12 также не запускается на счет, на выходе элемента ИЛИ 17 формируется сигнал логического нуля, второй делитель-распределитель 11 повторяет выходные сигналы первого делителя-распределителя 5, и выходной сигнал устройства соответствует истинной цикловой фазе. Если обнаружитель

7 отсутствия синхронизма вырабатывает ложный сигнал отсутствия синхронизма, а решающий узел 4 фиксирует правильное состояние синхронизма, то формирователь 8 сигналов фазирования сравнивает фазы делителя 3 частоты и первого делителя-распределителя 5, и, поскольку в этом случае они совпадают, вырабатывает сигнал только на первом своем выходе, сбрасывая обнаружитель 7 отсутствия синхронизма и триггер 9, Фаза первого делителя-распределителя 5 остается при этом неизменной и соответствует истинной цикловой фазе.

Если при этом отсутствуют пропадания сигнала в канале связи, то в момент появления сигнала на выходе обнаружителя 7 отсутствия синхронизма счетчик 10 переходит в режим счета, и в течение последующих К тактовых интервалов формирует на своем выходе сигнал логической единицы, В течение этих К тактовых интервалов второй делитель-распределитель 11 находится в режиме самостоятельного счета. Однако это не мешает второму делителю-распределителю 11 все время находиться в состоянии правильного синхронизма. Поскольку фаза первого делителя-распределителя 5 все время остается неизменной и соответствует истинной цикловой фазе, то и фаза второго делителя-распределителя 11 не может отличаться от истинной цикловой фазы, в какой бы момент не перешел второй делитель-распределитель 11 в режим самостоятельного счета, и в какой бы момент он не перешел обратно в режим повторения сигналов на его входах, Если в канале связи произошло пропадание сигнала, не приведшее к сбою цикловой синхронизации, то в этот момент происходит запуск на счет дополнительного счетчика 12, который в течение последующих L тактовых интервалов находится в режиме счета и формирует на своем выходе сигнал логической единицы. В течение указанных L тактов счетчик 10 не может перейти в режим счета, если на выходе обнаружителя 7 отсутствия синхронизма формируется сигнал обнаружения отсутствия синхронизма, а на выходе элемента

ИЛИ 17 в течение этих L тактовых интервалов присутствует сигнал логической единицы.,Значит в этом случае второй делитель-распределитель 11 находится в режиме самостоятельного счета в течение L тактов с момента пропадания сигнала. Однако, как и в предыдущем случае, это не приводит к отклонению фазы второго делителя-распределителя 11 от истинной цикловой фазы в связи с тем, что первый делитель-распределитель 5 все время находится в состоянии синхронизма.

Таким образом, устройство синхронизации по циклам обеспечивает высокую помехоустойчивость сохранения цикловой синхронизации как в случае неприема синхрогрупп из-за ошибок в канале связи, так и в случае пропаданий сигнала в канале свяРассмотрим работу устройства синхронизации по циклам после сбоя синхронизаI ции, Наиболее вероятной причиной сбоя цикловой синхронизации является сбой глстемы тактовой сиIIхронизации, или про1809543 скальзывание тактовых импульсов. Причиной такого проскальзывания могут быть llo мехи или пропадания сигнала в канале связи. Проскальзывание может иметь разный знак: при пропуске или приходе лишнего тактового импульса.

Если проскальзывание тактовых импульсов.произошло, когда пропадания сигнала в канале связи отсутствуют, то в этом случае дополнительный счетчик 12 остановлен и формирует на своем выходе сигнал логического нуля, т.е. дополнительный счет1 чик 12 не принимает участия в процессе восстановления синхронизма. Условно считаем, что проскальзывание тактовых импульсов произошло внутри 1-го цикла. Тогда к концу М-ro цикла второй анализатор 6 ошибок сформирует М сигналов ошибки подряд, Значит обнаружитель 7 отсутствия синхронизма выработает сигнал отсутствия синхронизма в конце М-ro цикла (при лишнем тактовом импульсе) или в начале (M+1)ro цикла (при пропуске тактового импульса).

Параметры решающего узла 4 выбираются таким образом, чтобы к моменту обнаружения отсутствия синхронизма делитель 3 частоты уже нашел новое состояние синхронизма, а решающий узел 4 зафиксировал это новое состояние синхронизма и сформировал на своем втором выходе сигнал, подготавливающий формирователь 8 сигналов фазирования к сравнению фаз делителя 3 частоты и первого делителя-распределителя 5. Значит, сравнение фаз делителя 3 частоты и первого делителя-распределителя 5 происходит в момент прихода первого циклового импульса делителя 3 частоты после обнаружения отсутствия синхронизма в обнаружителе 7 отсутствия синхронизма. При лишнем тактовом импульсе момент сравнения фаз соответствует концу

М-го цикла, а при пропуске тактового импульса — концу (М+1)-го цикла, В этот момент происходит установление нового синхронизма в первом делителе-распределителе 5, Счетчик 10 начинает счет в момент обнаружения отсутствия синхронизма, то есть в конце М-ro или в начале (М+1)-ro цикла, Если коэффициент счета счетчика 10 К выбран равным 1,5 цикла (K=1,5N), то до середины (М+2)-го цикла второй делительраспределитель 11 находится в режиме самостоятельного счета, и его выходные сигналы соответствуют неправильной цикловой фазе. Окончательное установление нового синхронизма во втором делителераспределителе 11 происходит, когда он переходит в режим повторения сигналов на его входах, т.е. по окончании счета счетчика

10, что соответствует примерно середине (M+2)-ro цикла. Таким образом, момент окончательного установления нового синхронизма во втором делителе-распределителе 11 не зависит от знака проскальзывания тактовых импульсов. Значит и время с момента сбоя синхронизации и до окончательного установления нового синхронизма не зависит от знака проскальзывания тактовых импульсов, а зависит только от момента сбоя

10 синхронизации внутри первого цикла. При задержке информационного сигнала в приемном устройстве в цифровой линии задержки на M+1 цикл максимальное время несинхронной работы составляет половину цикла, что соответствует минимально возможной величине, когда момент сбоя синхронизации внутри цикла на приеме установить невозможно.

Если сбой тактовой синхронизации (проскальзывание тактовых импульсов) произошел в момент пропадания сигнала в канале связи, то с момента пропадания сигнала и в течение L тактовых интервалов дополнительный. счетчик 12 находится в режиме счета и формирует на своем выходе сигнал логической единицы. Если сбой синхронизации произошел в первом цикле, то первый делитель-распределитель 5 перехо20

25 дит в состояние нового синхронизма в конце M-го цикла (при лишнем тактовом

30 импульсе) или в конце (M+1)-го цикла (при пропуске тактового импульса), Выберем Коэффициент счета L дополнительного счетчика 12 равным M+1 циклов: L=(M+1) N, Тогда в момент обнаружения отсутствия синхронизма (конец М-го цикла) дополнительный счетчик 12 будет формировать на своем выходе сигнал логической единицы, запрещая счетчику 10 переходить в режим счета. Зналогического элемента ИЛИ 17 будет присутствовать сигнал логической единицы во время счета дополнительного счетчика 12. т,е. в течение L тактов с момента пропадания сигнала. В течение указанных 1 тактов второй

45 делитель-распределитель 11 находится в режиме самостоятельного счета, и его выходные сигналы соответствуют неправильной цикловой фазе. Момент окончательного

50 установления нового синхронизма во втором делителе-распределителе 11 соответствует моменту перехода второго делителя-распределителя 11 в режим повторения сигналов на его входах и определяется моментом окончания счета дополнительного счетчика 12, который находится внутри (M+2)-го цикла ровно через

М+1 цикл с момента пропадания сигнала, Поскольку момент сбоя синхронизации соответствует моменту пропадания сигнала, 40 чит в рассматриваемом случае на выходе

1809543

Составитель В.Евдокимова

Техред M.Moðãåíòàë Корректор М Петрова

Редактор

Заказ 1291 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарина, 101 то мо мент сбоя синхронизации внутри первого цикла фактически известен на приеме.

Время с момента сбоя синхронизации и до окончательного установления нового синхронизма во втором делителе-распределителе 11 равно L тактам (М+1 циклам) и не зависит ни от знака проскальзывания тактовых импульсов, ни от момента сбоя синхро, низации внутри первого цикла. При задержке информационного сигнала в приемном устройстве в цифровой линии задержки íà М+1 цикл время несинхронной работы после пропаданий. сигнала не превосходит длительность пропадания сигнала. При кратковременных пропаданиях это время мало по сравнению с длительностью цикла, Формула изобретения

Устройстао синхронизации по циклам, содержащее опознаватель синхрогруппы, выход которого соединен с первым входом первого анализатора ошибок, второй вход которого соединен с выходом делителя частоты, а выходы первого анализатора ошибок соединены с соответствующими входами делителя частоты непосредственно и через решающий блок, выход опознавателя синхрогруппы через второй анализатор соединен с входами обнаружителя отсутствия синхронизма, выход которого соединен с одним из входов триггера, выход которого соединен с входом первого делителя распределителя через формирователь сигналов фазирования, другие входы которого соединены соответственно с выходами решающего узла делителя частоты и первого

5 делителя-распределителя, а другой выход формирователя сигналов фазирования соединен с входами сброса обнаружителя отсутствия синхронизма и триггера, причем управляющий вход второго анализатора

10 ошибок соединен с выходом первого делителя-распределителя, тактовый вход которого является тактовым входом устройства и соединен с тактовыми входами делителя частоты, счетчика и второго делителя-рас15 пределителя, установочные входы которого соединены с соответствующими выходами первого делителя-распределителя, о т л и ч аю щ е е с я тем, что, с целью сокращения времени восстановления синхронизма после

20 пропаданий сигнала, введены элемент ИЛИ и последовательно соединенные амплитудный детектор, пороговый блок, дополнительный счетчик, инвертор и элемент И-НЕ, при этом выход обнаружителя отсутствия синхронизма

25 соединен через элемент И-ХЕ с управляющим входом счетчика, выход которого соединен с управляющим входом второго делителя-распределителя через элемент.

ИЛИ, другой вход которого соединен с вы30 ходом дополнительного счетчика, тактовый вход которого соединен с тактовым входом счетчика.