Многоканальное устройство для обмена данными между модулями вычислительной системы

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при построении многопроцессорных и многомашинных вычислительных систем с использованием общей памяти. Цель изобретения - повышение быстрбдействия. Поставленная цель достигается тем, что устройство содержит первый, второй и третий элементы И 9, 10,11, первый, второй и третий дешифраторы 12, 13. 14, блок 15 оперативной памяти, четвертый, пятый и шестой элементы И 16, 17, 18, первый, второй и третий элементы И-НЕ 19, 20, 21, с первого по девятый элементы ИЛИ-НЕ 22-30, блок 31 постоянной памяти, первый и второй коммутаторы 32 и 33. четвертый, пятый и шестой дешифраторы 34, 35 и 36. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)5 G 06 F 13/14

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) ОПИСАНИЕ ИЗОБРЕТЕНИЯ57

К АВТОРСКОМУ СВИДЕТЕЛ ЬСТВУ (21) 4747400/24 (22) 09;10.89 (46) 23.04.93. Бюл. N 15 (71) Московский научно-исследовательекий институт радиосвязи (72) А.С.Кабанов и Г.H,Ãðèãoðüåa (56) Авторское свидетельство СССР

N. 1179361, кл. G 06 F 13/14, 1983.

Авторское свидетельство СССР

М 1256037, кл. 6 06 F 13/14, 1985. (54) МНОГОКАНАЛЬНОЕ УСТРОЙСТВО

ДЛЯ ОБМЕНА ДАННЫМИ МЕЖДУ МОН УЛЯМИ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ (57) Изобретение относится к вычислительной технике и может быть использовано при построении многопроцессорных и многома-

З

1с

Й ф

М фф

47 ф7

Ô5 ф

„„Я „„1810891 А1 шинных вычислительных систем с использованием общей памяти. Цель изобретения— повышение быстрбдействия. Поставленная цель достигается тем, что устройство содержит первый, второй и третий элементы И 9, 10, 11, первый, второй и третий дешифраторы 12, 13; 14, блок 15 оперативной памяти, четвертый, пятый и шестой элементы И 16, 17, 18, первый, второй и третий элементы

И-НЕ 19, 20, 21, с первого по девятый элементы ИЛИ-НЕ 22-30, блок 31 "постоянной памяти, первый и второй коммутаторы 32 и

33, четвертый, пятый и шестой дешифраторы 34, 35 и 36. 1 ил.

1810891 осуществляется коммутаторами 32 и 33 под управлением ПЗУ 31, выполняющего функцию процессорного элемента. Размещение буферного ОЗУ в заданном адресном пространстве обусловливается дешифраторами 12, 13, 14 адреса страницы ЗУ.

Рассмотрим режим обращения в блок

15 rio первой СШ. При обращении в страницу ЗУ размещения блока 15 с дешифратора

12 на элемент 9 поступает сигнал разрешения. При отсутствии с текущий момент вре50

Изобретение относится к вычислительной технике и может быть использовано для построения многомашинных и многопроцессорных вычислительных систем.(ВС) с использованием общей памяти.

Целью изобретения является повышение быстродействия.

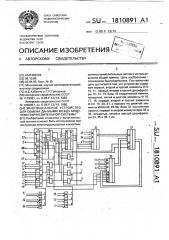

На чертеже представлена схема электрическая функциональная многоканального устройства для обмена данными между модулями вычислительной системы.

Устройство содержит первую, вторую, третью шины 1, 2, 3, чтения памяти, первую, вторую, третью шины 4, 5, 6 готовности устройства, шину 7 адреса, шину 8 данных устройства, первый, второй, третий элементы

9, 10, 11 И, первый, второй, третий дешифратор 12, 13, 14, блок оперативной памяти

15, четвертого по шестой элемента 16. 17, 18 20

И. с первого по третий элементы 19, 20, 21

И-НЕ, с первого по девятый элементы

22.„30 ИЛИ-НЕ, блок постоянной памяти

312, первый и второй коммутаторы 32 и 33, с четвертого по шестой дешифраторы 34, 35, 25

Зб, первую, вторую, третью шины 37. 38, 39 записи памяти, первую, вторую, третью шины 40, 41, 42 чтения ввода/вывода, первую, вторую, третью шины 46. 47, 48 подтверждения прерывания, первую, вторую, третью 30 шины 49, 50, 51 старших разрядов адреса, первую, вторую, третью шины 52, 53, 54 адреса страницы, первую, вторую, третью шину 55. 56, 57 младших разрядов адреса, первую, вторую„третью шины 58, 59, 60 35 да н н ых.

Устройство работает следующим образом.

Функциональное назначение устройства — соединение две и более ВС посредством обеспечения доступа к общей памяти в виде блока 15. Блок постоянной памяти 31 реализует процедуру обеспечения бесконфликтнога доступа к памяти при одновремен- 45 ном обращении нескольких ВС. Каждая иэ шин ВС идентична системной шине (СШ) микроЭВМ с ЦП типа INTEL 8080.

Коммутация шин адреса и данных BC мени обращения к внешнему устройству или выполнения процедур обусловленных запросов прерывания, с выхода элемента 9 на элемент 16 поступает сигнал разрешения.

При обращении по первой СШ к данному устройству с дешифратора 34 на элемент 16 поступает сигнал разрешения. далее с выхода элемента 16 на вход АЗ блока 31 поступает сигнал обращение к блоку 15 по первой

СШ, одновременно через элемент 30 на блок 31 поступает сигнал разрешения работы. В исходном состоянии на выходах блока

31 формируется лог,lll. При обращении по первой СШ после идентификации адреса страницы и старших разрядов шины адреса

СШ (ША СШ) на выходе 00 блока 31 формируется лог.О, разрешающий прохождение на блок 31 через элементы 22, 23, 28 и 29 сигналов "запись памяти" или "чтение памяти", одновременно на выходе элемента 19 логическим нулем формируется сигнал "готов", длительность лог,О составляется из времени задержки на элементах 22, 28, 31 и

19 в режиме чтения 23, 29, 31 и 19 в режиме записи, Формирование лог.О на 00 блока 31 обуславливает трансляцию коммутатором

32 младших разрядов ША первой СШ на адресные входы блока 15. Разрешение работы блока 31 обусловливает также разрешение работы блока 15. В режиме "запись памяти" с элемента 29 на вход WR блока 15 поступает сигнал разрешения записи логическим нулем, В режиме "запись в память" с 00 блока 31 на вход VA коммутатора 33 поступает лог.О, с выхода элемента 23 на вход VA — лог.1. Комбинация "01" на входах управления группой входов/выходов А коммутатора 33 обусловливает трансляцию сигналов с ША первой памяти первой ША СШ на.информационные входы блока 15, В режиме "чтение памяти" на входы управления

VA u VA поступает комбинация "00", обусловливающая трансляцию сигналов с выходов блока 15 Hà LLlA первой СШ (шина 58).

Рассмотрим режим обращения по вто рой СШ во время выполнения цикла команды обращения к памяти первой ВС. С выхода элемента 17 поступает сигнал разрешения, однако с 01 блока 31 лог."О" не поступает до окончания цикла обращения по первой СШ, в результате на выходе элемента 20 формируется логическим нулем сигнал

"готовность". По окончании процедуры на первой СШ на. 01 блока 31 устанавливается лог."О", на выходе элемента 20 формируется лог.1, что инициирует-процедуру обращения по второй СШ.

1810891

Рассмотрим режим одновременного обращения к устройству по первой и второй

СШ, В блоке 31 имеются сведения о приоритете каждой ВС. Если первая BC имеет более высокий приоритет, то при одновременном формировании сигналов

"чтение памяти" или "запись памяти" только на выходе 00 блока 31 появится лог."0", инициирующий процедуру обращения. После выполнения процедуры обращения от первой ВС формируется лог."0" на выходе 01 блока 15 и инициируется процедура обращения от второй ВС.

Аналогично решается конфликт ВС при иных комбинациях временных положений (совмещений) процедур обращений.

Весь возможный набор решений конфликтов вложен в блок 15.

Формула изобретения

Многоканальное устройство для обмена данными между модулями вычислительной системы, содержащее с первого по третий элементы И, с первого по третий дешифраторы и блок оперативной памяти, о т л и ч а ющ е, е с я тем, что, с целью повышения быстродействия, оно содержит с четвертого по шестой элементы И, с четвертбго по шестой дешифраторы, с первого по третий элементы И-НЕ, с первого по девятый элементы

ИЛИ-НЕ, блок постоянной памяти и первый и второй коммутаторы, причем, первый, второй и третий управляющие входы первой группы устройства.для подключения соответственно первого, второго и третьего каналов подключены соответственно к первым входам первого, второго и третьего элементов ИЛИ-НЕ, выходы которых подключены соответственно к первому, второму и третьему входам четвертого элемента

ИЛИ-НЕ, первый, второй и третий управляющие входы второй группы устройства для подключения соответственно первого, второго и третьего каналов подключены соответственно к первым входам пятого, шестого и седьмого элементов И, первый и второй входы признака ввода-вывода первой группы и первый вход подтверждения прерывания устройства для подключения соответственно первого, второго и третьего каналов подключены соответственно к первому, второму.и третьему входам первого элемента И, первый и второй входы призна° ка ввода-вывода второй группы и второй вход подтверждения прерывания устройства для подключения соответственно перво, го, второго и третьего каналов подключены

55 первого коммутатора, к второму адресному входу блока постоянной памяти, к BTophlM входам первого и пятого элементов ИЛИНЕ, к первому управляющему входу второго коммутатора и .второму входу первого элемента И-НЕ, выход которого подключен к соответственно к первому. второму и треть.ему входам второго элемента И, первый и второй входы признака ввода-вывода третьей группы и третий вход подтверждения прерывания устройства для подключения соответственно первого, второго и третьего каналов подкл ючены соответственно к первому, второму и третьему входам третьего элемента И. информационные входы первой, второй и третьей групп устройства для подключения соответственно первого, второго и третьего каналов подключен соответственно к

15информационным входам первого, второго и третьего дешифраторов, выходы которых подключены соответственно к четвертым входам первого, второго и третьего элементов И, выходы которых подключены соответ20 ственно к первым входам четвертого, пятого и шестого элементов И, информационные входы четвертой, пятой и шестой групп устройства для подключения соответственно первого, второго и третьего каналов подключены соответственно к информационным входам четвертого, пятого и шестого дешифраторов, выходы которых подключены соответственно к вторым входам четвертого, пятого.и шестого элементов И, 30 информационные входы седьмой, восьмой и девятой групп. устройства для подключения соответственно первого, второго и третьего каналов подключены соответственно к информационным входам первой, второй и

35 „третьей групп первого коммутатора, выходы которого подключены соответственно к адресным входам блока оперативной памяти, выходы которого подключены соответственно к информационным входам второго ком40 мутатора, выходы которого подключены к информационным входам блока оперативной памяти, информационные входы-выходы первой, второй и третьей групп второго

45 коммутатора подключены соответственно к информационным входам-выходам первой, второй и третьей групп устройства для подключения соответственно первого, второго и третьего каналов, выход четвертого эле50 мента И подключен к первым входам первого элемента И-НЕ, восьмого элемента

ИЛИ-HE и к первому адресному входу блока постоянной памяти, первый выход которого подключен к первому управляющему входу

1810891

Составитель Г,Смирнова

Техред M.Mîðråíòàë Корректор О.Густи

Редактор

Заказ 1446 Тираж Подписное

ВНИИПИ Государственного комитета rio изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж 35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент". r. Ужгород, ул.Гагарина, 101 первому выходу готовности устройства, второй выход блока постоянной памяти подключен к второму управляющему входу первого коммутатора, к третьему адресному входу блока постоянной памяти, к вторым входам второго и шестого элементов И-НЕ, к второму управляющему входу второго коммутатора и к первому входу второго элемента И-НЕ, выход которого годключен к второму выходу готовности устройства, третий выход блока постоянной памяти подключен к третьему управляющему входу первого коммутатора, к четвертому адресному входу блока постоянной памяти, к вторым входам третьего и седьмого элементов

ИЛИ-НЕ, к третьему управляющему входу второго коммутатора и к первому входу третьего элемента И-НЕ; выход которого подключен к третьему выходу готовности устройства, выход пятого элемента И подключен к второму входу второго элемента

И-НЕ, к пятому адресному входу блока постоянной памяти и к второму входу восьмого элемента И-НЕ, выход которого подключен к инверсным входам синхронизации блоков постоянной и оперативной памяти, выход шестого элемента И подключен к второму входу третьего элемента И-НЕ, к

5 .третьему входу восьмого элемента ИЛИ-HE и к шестому адресному входу блока постоянной памяти, выход четвертого элемента

ИЛИ-НЕ, подключен к седьмому адресному входу блока постоянной памяти, выход девятого элемента ИЛИ-НЕ подключен к восьмому адресному входу блока постоянной памяти и к входу записи-чтения блока оперативной памяти, выходь| пятого элемента

ИЛИ-НЕ подключены к первому входу девятого элемента ИЛИ-НЕ и к четвертому управляющему входу второго коммутатора, выход шестого элемента ИЛИ-НЕ подключен к второму входу девятого элемента

2р ИЛИ-НЕ и к пятому управляющему входу второго коммутатора, выход седьмого элемента ИЛИ-НЕ подключен к третьему входу девятого элемента ИЛИ-НЕ и к шестому уп. равляющему входу второго коммутатора, 25