Приемник биполярных импульсов

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть применено в системах передачи и приема цифровой информации по согласованным линиям связи между обрабатывающими средствами связи с удаленными терминалами, работающими с разными частотами передачи. Целью изобретения является расширение области применения приемника и повышение его помехоустойчивости. Приемник со держит узел приема биполярных сигналов, состоящий из входного трансформатора, трех компараторов, шести резистооов. трех диодов, одновибратора, и узел распознавания , состоящий из генератора высокочастотных сигналов, трех К-разрядных счетчиков, программируемого постоянного запоминающего устройства, двух элементов ИЛИ-НЕ на К-входов, четырех элементов 2 И, сдвоенного селектора-мультиплексора п , мульти плексора 4 - 1 и триггера, две выходные шины , шину адреса. 2 ил. ел С

СОГОЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (ч)s Н 03 К 5/01

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ! 00

С)

О

0 (21) 4937811/2.1 (22) 04,04,91 (46) 23.04.93. Бюл. ¹ 15 (71) Научно-исследовательский институт электронных вычислительных машин (72) М.А.Бокач, Л,Т.Пинчук и l0.М.Терешкин (56) Патент США ¹ 4153848, кл, Н 03 К 5/01, 1979.

Авторское свидетельство СССР

N 1394419, кл. Н 03 К 5/01, 1988, (54) ПРИЕМНИК БИПОЛЯРНЫХ ИМПУЛЬСОВ (57) Изобретение относится к вычислительной технике и может быть применено в системах передачи и приема цифровой информации по согласованным линиям связи между обрабатывающими средствами связи с удаленными терминалами, работаюИзобретение относится к импульсной технике и может быть использовано в системах цифроьой обработки сигналов для приема по линии связи цифровой информации от удаленных терминалов.

Цель изобретения — расширение области применения и функциональных воэможностей приемника и повышение его помехоустойчивости.

Введение в состав приемника биполярных импульсов программируемого постоянного. запоминающего устройства (ППЗУ), высокочастотного генератора и счетчиков позволяет произвести более точное измерение параметров входных сигналов, повысить селективность приемника и обеспечить большую достоверность распознавания информационных сигналов на нескольких частотах передачи без физической замены приемника-, ..ЬЦ 1810991 А1 щими с разными частотами передачи, Целью изобретения является расширение области применения приемника и повышение его помехоустойчивости. Приемник содержит узел приема биполярных сигналов, состоящий иэ входного трансформатора, трех компараторов, шести реэистооов, трех диодов, одновибратора, и узел распознавания, состоящий из генератора высокочастотных сигналов, трех К-разрядных счетчиков, программируемого постоянного запоминающего устройства, двух элементов ИЛИ вЂ” HE на

К-входов, четырех элементов 2 И, сдвоенного селектора-мультиплексора n - 1, мультиплексора 4 - 1 и триггера, две выходные шины, шину адреса, 2 ил.

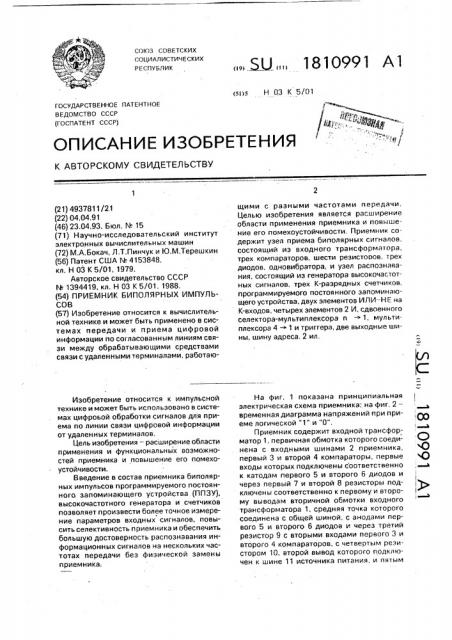

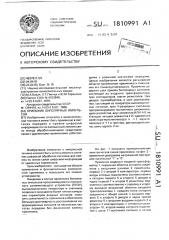

На фиг. 1 показана принципиальная электрическая схема приемника; на фиг. 2— временная диаграмма напряжений при приеме логической "1" и "0".

Приемник содержит входной трансформатор 1, первичная обмотка которого соединена с входными шинами 2 приемника, первый 3 и второй 4 компараторы, первые входы которых подключены соответственно к катодам первого 5 и второго 6 диодов и через первый 7 и второй 8 резисторы подключены соответственно к первому и второму выводам вторичной обмотки входного трансформатора 1. средняя точка которого соединена с общей шиной, с анодами первого 5 и второго 6 диодов и через третий резистор 9 с вторыми входами первого 3 и второго 4 компараторов, с четвертым резистором 10, второй вывод которого подключен к шине 11 источника питания, и пятым

1810991 резистором 12, второй вывод которого соединен с выходом одновибратора 13, первый вход которого соединен с выходом третьего компаратора 14, второй вход которого соединен с шиной источника опорного напряжения 15 и анодом третьего диода 16, катод: которого подключен к первому входу третьего компаратора 14 и через шестой резистор

17 к второму выводу вторичной обмотки входного трансформатора 1, триггер 18, выход которого соединен с первой выходной шиной

19 приемника, а также дополнительно введенные сдвоенный селектор-мультиплексор

2 - 1 20 и программируемое постоянное запоминающее устройство (ППЗУ) 21, первый

22, второй 23, третий 24 и четвертый 25 элементы 2 И, первый 26, второй 27 элементы ИЛИ вЂ” НЕ на К входов, мультиплексор

4 - 1 28, первый 29, второй 30 и третий 31 двоичные К-разрядные счетчики, первый 32 и второй 33 элементы 2ИЛИ вЂ” НЕ и генератор высокочастотных сигналов 34, причем выходы первого 3, второго 4 компараторов соединены с входами первого элемента 2 И

22 и соответственно с первыми входами первого 32 и второго 33 элементов 2ИЛИ—

НЕ, а выход генератора 34 соединен с первым входом второго элемента 2И 23 и с вторыми входами первого 32, второго 33 элементов 2ИЛИ-НЕ, выходы которых соединены соответственно со счетными входами первого 29, второго 30 и третьего 31

К-разрядных счетчиков, выходы которых последовательно соединены с адресными входами ППЗУ 21, вход разрешения работы которого соединен с выходом первого элемента 2И 22 и первым и вторым входами мультиплексора 4-1 28, à 2п выходов

ПОЗУ 21 соединены с соответствующими 2п входами сдвоенного селектора-мультиплексора n - 1 20, m-разрядный адресный вход которого соединен с- соответствующими разрядами дополнительного адресного входа 35 приемника, первый выход соединен с вторым выходом 36 приемника и входом параллельного занесения кода третьего счетчика 31, а второй выход соединен с входами сброса RS-триггера 18 и трех счетчиков 29-31, выходы первого 29 из которых соединены с К входами первого элемента

ИЛИ-НЕ 26, а второго 30 — с К входами второго элемента ИЛИ-НЕ 27, выход которого соединен с первым входом третьего элемента 2И 24 и вторым адресным входом мультиплексора 4 - 1 28, первый адресный вход которого соединен с выходом первого

К-входового элемента ИЛИ вЂ” НЕ, нулевой и третий входы соединены с общей шиной (что соответствует логическому нулю на этих

55 входах), а выход соединен с вторым входом второго элемента 2И 23, второй выход первого счетчика 29 соединен с вторым входом третьего элемента 2И 24, выход которого соединен с установочным входом RS-триггера 18, выход которого соединен с первым входом четвертого элемента 2И 25, выход которого соединен с вторым входом одновибратора 13, а второй вход — с вторым выходом второго счетчика 30.

Приемник работает следующим образом.

На входные шины 2 приемника с двухпроводной. согласованной линии связи поступают биполярные информационные сигналы: логическая "1" представлена положительным импульсом, вслед за которым поступает отрицательный, а логический "0" представлен биполярными импульсами в обратной последовательности (фиг. 2 а).

Форма и амплитуда входных импульсов приемника определяются параметрами линии связи. На фиг. 2 а пунктирной линией показан входной сигнал с минимальными искажениями, имеющий место в том случае, когда коэффициент передачи линии связи близок к единице, а время установления переходной характеристики линии значительно меньше длительности передаваемого импульса.

Импульсы с вторичной обмотки трансформатора 1 через ограничительные резисторы 7, 8 поступают на входы компараторов 3 и 4, на другие входы которых подается положительное напряжение смещения, формируемое с помощью резисторов 9 и 10, включенных между общей шиной, шиной 11 источника питания и блоком переключения порога срабатывания, образуемого совокупностью элементов 1317.

Если амплитуда импульсов на входах компараторов 3 и 4 превышает напряжение смещения, компараторы срабатывают и на их выходах формируются отрицательные импульсы, длительность которых определяется длительностью положительных и отрицательных составляющих (полуволн) биполярного сигнала на уровне входного порога срабатывания приемника(фиг, 2 б, e).

Компаратор 3 срабатывает на положительные входные импульсы, а компаратор 4 — на отрицательные, поэтому при приеме логической "1" сначала срабатывает компаратор 3, затем 4.

При приеме логической единицы врезультате совпадения низкого уровня сигнала на выходе компаратора 3 (фиг. 2 б) и сигналов высокочастотного генератора 34

1810991

15 вует либо синхроимпульс на выходах с1 или с2 (фиг. 2 с1, с2), либо сигнал сброса р1 или р2 (фиг, 2 р1, р2). Сигналы с1, р1 программируются для одной частоты приема, а с2; р2—

20 для другой, Количество распознаваемых ча25

30 Если параметры принятых сигналов не

40 ние триггера 18, выход которого соединен с

50 мультиплексора 20. (фиг. 2 г) на счетный вход счетчика 29 поступают импульсные сигналы (фиг, 2 д), количество которых определяется длительностью отрицательного выходного сигнала компаратора 3 (длительностью положительной полуволны входного биполярного сигнала) и периодом повторения То импульсов генератора 34.

Во время прохождения второй полуволны входного биполярного сигнала в результате совпадения низкого уровня выходного сигнала компаратора 4 (фиг. 2 в) и сигналов генератора 34 на счетный вход счетчика 30 с выхода элемента 33 также проходит определенное количество импульсов (фиг. 2 е), соответствующее длител ьности отрицательной полуволны входного биполярного сигнала.

При приеме с линии связи искаженных по форме биполярных сигналов между отрицательными выходными импульсами компараторов 3 и 4 может образовываться пауза, В момент паузы на выходе элемента 22 устанавливается уровень логической единицы (фиг, 2 ж).

Счетчик 31 служит для определения длительности паузы между полуволнами биполярного сигнала путем подсчета импульсов генератора 34 в момент паузы.

Если в счетчике 29 зарегистрирован прием положительной полуволны, то на выходе элемента 26 формируется низкий уровень (фиг. 2 и). Если же в счетчике 30 зарегистрирован прием отрицательной полуволны, то на выходе элемента 27 формируется низкий логический уровень (фиг. 2 к), Выходы элементов 26 и 27 соединены с адресными входами мультиплексора 28, на выходе которого возникает положительный: сигнал (фиг. 2 л) только при наличии высокого уровня сигнала на выходе элемента 22 (фиг. 2 ж) при условии, что только в одном счетчике 29 или 30 зарегистрирован прием одной иэ полуволн входного биполярного сигнала.

Логический уровень "1" на выходе мультиплексора 28 (фиг, 2 л) разрешает прохождение сигналов г высокочастотного генератора 34 на выход элемента 23 и на счетный вход счетчика 30 (фиг. 2 м).

При приеме первой полуволны сигнал с второго выхода счетчика 29 при нулевом состоянии счетчика 30 (фиг, 2 к) проходит через элемент 24 на вход S триггера 18 и устанавливает его в состояние логической 5

"1" (фиг. 2 н). При приеме второй полуволны единичного биполярного сигнала в результате совпадения высоких уровней сигнала на выходе триггера 18 и втором выходе счетчика 30 на выходе элемента 25 формируется положительный импульс, поступающий н» второй вход одновибратора 13 (фиг. 2 и).

После приема первой и второй полунолн биполярного сигнала состояние счетчике»

29 — 31 соответствует длительности этих пол уволн и паузы между ними. Каждая частота приема сигналов характеризуется определенными ограничительными параметрами длительности укаэанных сигналов, а следовательно, и допустимых состояний счетчиков, Выходы счетчиков соединены с адресными входами ППЗУ 21. Состояние выходов ППЗУ программируется таким образом, что в момент разрешения работы

ППЗУ (фиг. 2 ж) каждому адресу соответстстот приема лимитируется только количеством парных выходов ППЗУ и организацией мультиплексора 20. На фиг. i мультиплексор 20 организован для выбора одной иэ двух возможных частот приема в соответствии с уровнем сигнала на адресном входе 35 выбора частоты. Диаграмма напряжений на фиг. 2 соответствует выбору первой частоты приема. соответствуют требованиям первой частоты, то сигнал сброса р1 проходит на выход р мультиплексора 20 и сбрасывает счетчики и RS-триггер 18 в исходное состояние. При соответствии параметров формируется сигнал с1, который проходит на первый выход мультиплексора 20, на синхронизирующий выход 36 приемника, Выработанному синхросигналу соответствует единичное состояпервым информационным выходом 19 приемника. Сигнал е с выхода мультиплексора

20 устанавливает в единичное состояние все разряды счетчика 31, что приводит к изменению на входах ППЗУ 21 и, с некоторой задержкой, формированию сигнала сброса р на втором выходе мультиплексора

20. который приводит схему в исходное состояние, подготавливая ее тем самым к приему очередного биполярного сигнала а.

Длительность сигнала с (фиг. 2 с) на выходе мультиплексора 20 определяется временем срабатывания счетчика 31 по установочному входу, временем срабатывания ППЗУ и мультиплексора 20.

Длительность сигнала р (фиг. 2р) на выходе мультиплексора 20 определяется временем срабатывания счетчиков 29. 30 по входу R, временем срабатывания ППЗУ 21»

1810991

20

30

55

В качестве генератора 34, например, может быть использована серийно выпускаемая интегральная микросхема генератора

К531ГГ1П. в качестве селекторов-мультиплексоров 20, 28 — интегральные микросхемы

К531КП11, К531КП2 соответственно, в качестве счетчиков 29 — 31 — интегральные микросхемы К555ИЕ7, в качестве ППЗУ 21— интегральные микросхемы КР556РТ5, КР556РТ7, При приеме логического "0" схема блока работает аналогичным образом, только вследствие того, что сигналы е возникают ранее, чем д, нет необходимых условий совпадения сигналов на элементе 24 и триггер

18 остается в нулевом состоянии к моменту формирования синхросигнала с на выходе мультиплексора 20.

Длина линии определяет величину затухания электрического биполярного импульса, поэтому в зависимости от условий применения входные импульсы могут по амплитуде отличаться примерно на порядок.

Для повышения достоверности принимаемой информации необходимо, чтобы величина порога компараторов 3, 4 т.е. величина положительного напряжения на входах компараторов изменялась в зависимости от амплитуды принимаемых сигналов.

В противном случае величину nopora пришлось бы заведомо выбирать очень малой в расчете на худший случай. Но при больших амплитудах входного сигнала в линии связи возникают псмехи за счет переходных электрических процессов (например, при неполном согласовании линии связи) или за счет наводок от внешних источников помех, Эти помехи могут быть по величине соизмеримы с пороговым напряжением компараторов и приводить к их ложному срабатыванию. Чтобы этого не происходило, в схеме приемника используется узел переключения порога срабатывания на элементах 12-17, назначение которого — увеличить порог срабатывания компараторов 3, 4, если амплитуда входных импульсов превышает определенную величину.

Один из входов компаратора 14 подсоединен к источнику положительного опорного напряжения (шина 15), а другой вход через резистор 17 подсоединен к одной из вторичных обмоток трансформатора, Компаратор срабатывает в том случае, если амплитуда положительного импульса на этой обмотке превышает величину опорного напряжения, Если приемник воспринимает биполярный сигнал логической "1". то во время действия второй полуволны срабатывает компаратор 14 и на его выходе формируется отрицательный импульс. При этом на выхо-. де элемента 25 формируется положительный импульс (фиг. 2 n). Совпадение по времени этих двух импульсов приводит к запуску одновибратора с подтверждающим запуском 13, Положительный перепад напряжения с выхода одновибратора 13 (показан пунктиром на фиг, 2 т) через резистор 12 повышает напряжение порога компаратора

3, 4 и тем самым повышает помехоустойчивость приемника. Если же амплитуда входных импульсов недостаточна для переключения компаратора 14, то одновибратор 13 не запускается и приемник продолжает работать при низком напряжении порога компараторов3 и 4.

Процедура приема цифровой информации производится словами фиксированной длины, причем слово всегда начинается с

"1". Длительность выходного сигнала одновибратора 13 выбирается достаточно большой, чтобы заведомо перекрыть по времени длительность слова и паузу между словами

Одновибратор. с подтверждающим запуском (при поступлении входных запускающих импульсов как минимум в начале каждого слова) продолжает оставаться в квазиустойчивом состоянии неопределенно долгое время и удерживает высокое значение порога компараторов 3 и 4.

Диод 16 так же, как и диоды 5, 6, является защитным и предохраняет вход компаратора

14 от перенапряжений при поступлении отрицательных импульсов.

Наличие в приемнике двух выходов— синхронизирующего 36 и информационного

19, а также управление уровнем порога срабатывания компараторов 3 и 4 обеспечивает самосинхронизацию работы приемника и надежную передачу информации в логические схемы обработки.

Практическая реализация и экспериментальная обработка предлагаемого приемника на частотах приема 380 кГц и 860 кГц при частоте генерации сигналов (фиг, 2 г), равной 12160 кГц, показала высокую достоверность и помехозащищенность обмена информацией между устройствами управления и удаленными терминалами. Высокая степень дискредитации измеряемых счетчиками 29 — 31 сигналов позволяет с достаточно высокой степенью точности произвести их измерение и либо отвергнуть (формируется сигнал сброса P), либо принять как удовлетворяющие требованиям для данной частоты приема (формируется синхросигйал с на выходе 36).

При этом важно также и то, что в отличие от прототипа синхросигнал вырабатывается

1810991 мехам и сигналам "не своей" частоты. 5

Таким образом, предлагаемый прием10

30

35 не по переднему фронту второй полуволны, а в результате измерения обеих полуволн и паузы между ними, что позволяет повысить селективность приемника к любого вида поник биполярных сигналов по сравнению с известными имеет более высокую селективность по отношению к различного рода помехам и позволяет изменять частоту приема информации без его физической замены. В качестве каналов связи может применяться любой вид согласованной линии: коаксиальные несимметричные и симметричные линии, витые пары, телефонные провода.

Селективность приемника может быть повышена за счет использования более высокочастотного внутреннего или внешнего генератора, Исследования показали, что предлагаемый приемник обеспечивает уверенный прием биполярных сигналов с коаксиальной согласованной линии связи длиной до 2,5 км при частоте до 1 мГц.

При снижении частоты передачи в качестве линии связи могут быть использованы витые пары или телефонные провода, В настоящее время разработаны и используются несколько терминальных устройств, имеющих различную частоту передачи и приема биполярных сигналов.

Предлагаемый приемник обеспечивает их объединение в систему под управлением одного устройства в любом удобном для пользователя сочетании терминалов с различной частотой передачи без замены приемников или увеличения их числа, Формула изобретения

Приемник биполярных импульсов, содержащий входной трансформатор, первичная обмотка которого соединена с входными шинами, первый и второй компараторы, первые входы которых подключены соответственно к катодам первого и второго диодов и через первый и второй резисторы подключены соответственно к первому и второму выводам вторичной обмотки входного трансформатора, средняя точка которого соединена с общей шиной, с анодами первого и второго диодов и через третий резистор с вторыми входами первого и второго компараторов, с четвертым резистором, второй вывод которого подключен к шине источника питания, и с пятым резистором, второй вывод которого соединен с выходом одновибратора, первый вход которого соединен с выходом третьего компаратора, второй вход которого соединен с шиной источника опорного напряжения и

55 анодом третьего диода, катод кси цм- о под ключен к первому входу третьего компзратора и через шестой резистор к второму выводу вторичной обмотки входного рвнс. форматора, а также триггер, выход которого соединен с первой выходной шиной, о т л ич а ю шийся тем, что, с целью расширения области применения и повышения помехоустойчивости, в него введены шина адреса, сдвоенный селектор-мультиплексор. программируемое постоянное запоминающее устройство, четыре элемента 2 И, два К входовых элемента ИЛИ вЂ” НЕ, мультиплексор, три двоичных К-разрядных счетчика. два элемента 2ИЛИ вЂ” НЕ и генератор высокочастотных сигналов, причем выходы первого и второго компараторов соединены соответственно с входами первого элемента 2И и первыми входами первого и второго элементов 2ИЛИ-НЕ, а выход генератора соединен с первым входом второго элемента

2И и с вторыми входами элементов 2ИЛИНЕ, выходы которых соединены соответственно со счетными входами третьего, первого и второго К-разрядных c çò÷èêîa, выходы К-разрядных счетчиков последовательно соединены с адресными входами программируемого постоянного запоминающего устройства, вход разрешения работы которого соединен с выходом первого элемента 2И и первым и вторым входами мультиплексора, à 2п выходов программируемого постоянного запоминающего устройства соединены с соответствующими 2п входами сдвоенного селектора-мультиплексора, m-разрядный адресный вход которого (m = logan) соединен с соответствующими разрядами шины адреса. а первый выход соединен с второй выходной шиной и входом параллельного занесения кода третьего счетчика, а второй выход соединен с входами сброса RS-триггера и

К-разрядных счетчиков, выходы первого из которых соединены с К-входами первого элемента ИЛИ-НЕ, а второго — с К-входами второго элемента ИЛИ вЂ” НЕ, выход которого соединен с первым входом третьего элемента 2И и вторым адресным входом мультиплексора, первый адресный вход которого соединен с выходом первого К-входового элемента ИЛИ вЂ” НЕ, нулевой и третий входы подключены к общей шине, а выход соединен с вторым входом второго элемента 2ИНЕ, а второй выход первого счетчика соединен с вторым входом третьего элемента 2И, выход которого соединен с установочным входом RS-триггера, выход которого соединен с первым входом четвертого элемента 2 И, выход которого соединен с вторым входом одновибратора, а второй входс вторым выходом второго счетчика.

1810991

1810991

Тр г р .е

«Ж и сг

47

С

Составитель М. Бокач

Редактор Г, Бельская Техред М.Моргентал Корректор Л, Пилипенко

Заказ 1451 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарина, 101