Устройство для разделения направлений приема и передачи в дуплексных системах связи

Иллюстрации

Показать всеРеферат

Использование: в технике связи, в устройствах для передачи сообщений. Сущность изобретения: устройство содержит один блок согласования 1, один коммутатор 2, два цифроаналоговых преобразователя 3, 27, один аналого-цифровой преобразователь 4. один формирователь кодовых комбинаций 5, десять элементов И 6-8, 10, 11, 13, 15-18, два счетчика 9, 14, один триггер 12, три блока памяти 19,20,25, один элемент ИЛИ 21, один блок сравнения 22, один вычитатель 23, один генератор управляющих импульсов 24, один сумматор 26, один вход режима работы 28, один информационный вход 9, два выхода 30, 32, один выход готовности к работе 31. Точность работы устройства повышается за счет ликвидации случайных помех в подключенном канале связи в процессе обучения устройства, что приводит к повышению достоверности передаваемой информации. 2 ил.

сок з СОВ -тских

СОЦИАЛИСТИЧЕCKMX

РЕСПУБЛИК (ч)s Н 04 В 1/52

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) И1 " И1 Ж ь=йА

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЪСТВУ

2Ю юг. 1 (21) 4906290/09 (22) 10,12.90 (46) 23,04.93. Бюл. ¹ 15 (72) С.П.Присяжнюк, В.M,×èæ и И.В.Скакун (56) Авторское свидетельство СССР

¹ 1133675, кл. Н 04 В 1/52, 1983. (54) УСТРОЙСТВО ДЛЯ РАЗДЕЛЕНИЯ НАПРАВЛЕНИЙ ПРИЕМА И ПЕРЕДАЧИ В

ДУПЛЕКСНЫХ СИСТЕМАХ СВЯЗИ (57) Использование: в технике связи, в устройствах для передачи сообщений, Сущность изобретения: устройство содержит один блок согласования 1, один коммутатор

2, два цифроаналоговых преобразователя 3, 27, один аналого-цифровой преобразова,50„„1811009 А1 тель 4. один формирователь кодовых комбинаций 5, десять элементов И 6-8, 10, 11, 13, 15-18, два счетчика 9, 14, один триггер 12, три блока памяти 19,20,25, один элемент

ИЛИ 21, один блок сравнения 22, один вычитатель 23, один генератор управляющих импульсов 24, один сумматор 26, один вход режима работы 28, один информационный вход 9, два выхода 30, 32, один выход готовности к работе 31. Точность работы устройства повышается за счет ликвидации случайных помех в подключенном канале связи в процессе обучения устройства, что приводит к повышению достоверности передаваемой информации. 2 ил.

1811009

Изобретение относится к области связи и может найти применение в устройствах для передачи сообщений.

Цель изобретения — повышение точности работы устройства за счет исключения влияния случайных помех канала связи в процессе обучения устройства.

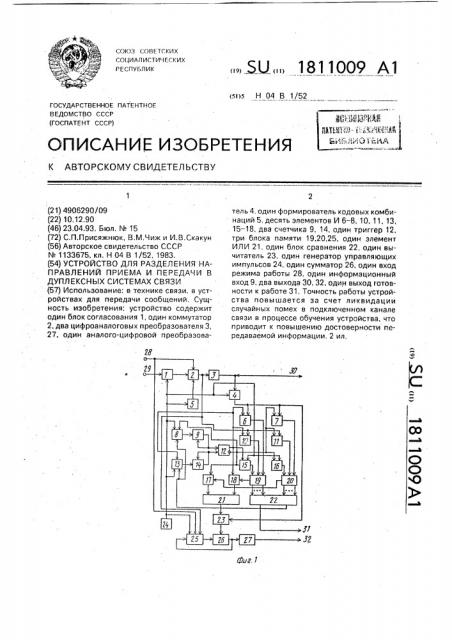

На фиг. 1 изображена функциональная электрическая схема устройства; на фиг. 2— эпюры напряжений, поясняющие его работу, Устройство для разделения направлений приема и передачи в дуплексных системах связи содержит блок 1 согласования, коммутатор 2, первый цифроаналоговый преобразователь 3, аналого-цифровой преобразователь 4, формирователь 5 кодовых комбинаций, первый 6, второй 7, третий 8 элементы И, первый счетчик 9, четвертый

10, пятый 11 элементы И, триггер 12, шестой элемент И 13, второй счетчик 14, седьмой

15, восьмой 16, девятый 17 и десятый 18 элементы И, второй 19 и третий 20 блоки памяти, элемент ИЛИ 21, блок 22 сравнения, вычитатель 23, генератор 24 управляющих импульсов, первый блок 25 памяти, сумматор 26, второй цифроаналоговый преобразователь 27, вход 28 режима работы, информационный вход 29, первый выход 30, выход 31 готовности к работе, второй выход 32.

Устройство работает следующим образом.

После включения питания устройство устанавливается в исхЬдное состояние, при этом счетчики 9, 14, триггер 12, блоки памяти 19, 25 устанавливаются в нулевое состояние, а блок памяти 20 — в единичное состояние (входы установки в исходное состояние условно не показаны).

Перед сеансом работы осуществляют обучение устройства с учетом параметров подключенного канала связи. Сущность обучения заключается в следующем.

Начало процесса обучения устройства осуществляется с появлением сигнала оконечного оборудования на входе 28 режима работы устройства и включением генератора 24 управляющих импульсов, который начинает генерировать управляющие импульсы для каждой кодовой комбинации формирователя 5 кодовых комбинаций, По сигналу оконечного оборудования коммутатор 2 подключает выход формирователя 5 кодовых комбинаций к входу первого цифроаналогового преобразователя 3. Формирователь 5 кодовых комбинаций поочередно выдает в двоичной форме соответствующие значения всех используемых для представления сигнала источника сообщений уровней. Сигналы, соответствующие уровням, используемым для представления сигнала источника сообщения, проходя через первый цифроаналоговый преобразова5. тель 3 и затем через аналого-цифровой преобразователь 4, появляются на первых входах элементов И 10, 11 для записи во второй 19 или третий 20 блоки памяти по адресам, определяемым двоичным числом, "0 отображающим величину уровня сигнала, проходящего в данный момент через коммутатор 2 и поступающего на первые входы элементов И 10, 11. Так как триггер 12 в начальный момент времени находится в ис15 ходном.(нулевом) состоянии, то потенциал единичного уровня с инверсного выхода триггера 12 поступает на третий вход элемента И 8 и открывает его для прохождения импульсов с генератора 24 управляющих

20 импульсов на счетный, суммирующий вход счетчика 9. Коэффициент пересчета счетчиков 9, 14 равен P (где P — число уровней, используемых для представления сигнала источника сообщений). После появления Pго импульса на счетном входе счетчика 9 появляется импульс на его выходе, который устанавливает счетчик 9 и, поступая на $вход триггера 12, переводит его в единичное состояние. Потенциалы с прямого и инверс30 ного выходов триггера 12 управляют записью информации соответственно в блоки памяти 19 и 20. Таким образом, в блоки 19 и

20 поступает информация о первом и втором циклах обучения устройства, Блок 22

35 сравнения осуществляет поразрядное сравнение соответствующих регистров блоков

19, 20 памяти. Наличие потенциала единичного уровня на выходе "Равно" блока 22 сравнения свидетельствует о том, что на

40 одинаковые соответствующие кодовые комбинации формирователя 5 кодовых комбинаций получены одинаковые соответствующие ответы-результаты из канала связи; следовательно, в процессе обу45 чения устройства в канале связи не присутствовала случайная помеха. Потенциал единичного уровня на выходе 31 устройства свидетельствует о готовности устройства к работе, а потенциал нулевого

50 уровня с выхода "Неравно" блока 22 сравнения закрывает элементы И 8, 13, В противном случае процесс обучения устройства продолжается. Таким образом, предлагаемое устройство является адаптивным.

После обучения по сигналу оконечного оборудования на входе 28 режима работы устройства оно переходит в режим работы, При этом коммутатор 2 подключает выход блока 1 согласования к входу первого цифроаналогового преобразователя 3. Отсчеты

1811009 сигнала U(t) (фиг, 2 а) с выхода источника сообщения через информационный вход 29 устройства в блоке 1 согласования преобразуются в двоичные комбинации. Эти комбинации, отображающие уровни входного сигнала, проходят через коммутатор 2 на вход первого цифроаналогового преобразователя 3, в котором превращаются в сигнал

U(t) (фиг. 2 б), подаваемый в канал связи, Сигнал U(t), складываясь с сигналом противоположной стороны Y(t) (фиг. 2 в), проходит через аналого-цифровой преобразователь

4, в котором суммарный сигнал X(t) приобретает цифровой вид X(k Л t) (фиг. 2 r). Кодовые комбинации, соответствующие отсчетам сигнала X(k Л t) = U Л n(kA т)+

+Y (k Л t), записываются в блоках 19, 20 памяти по адресам, определяемым сигналом с выхода коммутатора 2 и равным величине уровня сигнала U(t), представленного в двоичной форме в момент k Л t. Предварительно (до момента записи) считанный из рассматриваемой ячейки (регистра) памяти блока 19 (20), через элементы И 18 (17), ИЛИ

21 (в зависимости от состояния триггера 12), отсчет сигнала вычитается в вычитателе 23 из сигнала на выходе аналого-цифрового преобразователя 4 (фиг. 2 д).

Далее полученный результат разности

X>(k b, с) складывают в сумматоре 26 с содержимым ячейки первого блока 25 памяти, которая имеет такой же адрес, что и ячейка памяти второго 19 (третьего 29) блока памяти. Результат суммирования, представляющий собой в цифровой форме искомый сигнал Увых(К Л t) (фиг. 2 е), подают на второй цифроаналоговый преобразователь 27, где он превращается в исходную форму Y(t). Результат суммирова-. ния Y»>(k Л с) также. записывается в ту самую ячейку памяти первого блока 25 памяти, из которой было считано содержимое

Y(m Ь t) на второй вход сумматора 26.

На фиг, 2 а цифры под осью абцисс обозначают номера уровней, которые принимает сигнал U(t) в блоке 1 согласования, а на фиг. 2 д и фиг. 2 е цифры под осью абцисс обозначают соответственно номера ячеек второго 19 (третьего 20) и первого блоков памяти, откуда считывается, а затем записывается информация в соответствующие k Л t моменты времени.

Устройство не накладывает никаких ограничений. на соотношения скоростей манипуляции в обоих направлениях передачи, а также не требует использования сигналов с неперекрывающимися спектрами. Поэтому для передачи информации в обоих направлениях используются сигналы, ширина

55 устройства и соединен с вторым входом аналого-цифрового преобразователя, выход которого подключен к второму входу вычитателя, выход которого соединен с вторым входом сумматора, выход формирователя кодовых комбинаций соединен с третьим входом коммутатора, второй вход которого объединен с вторым входом первого блока памяти и является входом режима работы устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения точности за счет исключения вщ яния помех в начале связи, введены десять элементов И, триггер, перспектров Л F<, которых может быть выбрана равной ширине полосы пропускания канала Л Ек. При этом обеспечивается максимально возможная эффективность ис5 пользования полосы пропускания канала связи BMawc = 2Fk, эффективность использования полосы пропускания Э» = — 1.

В

Вмакс

Технико-экономический эффект от ис10 пользования предлагаемого устройства для разделения направлений приема и передачи в дуплексных системах связи состоит в том, что повышается точность работы устройства за счет ликвидации случайных по15 мех в подключенном канале связи в процессе обучения устройства, Это обстоятельство, в свою очередь, приводит к повышению достоверности передаваемой информации.

20 Формула изобретения

Устройство для разделения направлений приема и передачи в дуплексных системах связи, содержащее блок согласования, коммутатор, первый и второй цифроанало25 говые преобразователи, аналого-цифровой преобразователь, формирователь кодовых комбинаций, первый и второй блоки памяти, генератор управляющих импульсов, вычита-. тель и сумматор, причем выход генератора

30 управляющих импульсов соединен с входом формирователя кодовых комбинаций, с первыми входами блока согласования, аналогоцифрового преобразователя и первого блока памяти, выход которого соединен с

35 первым входом сумматора, выход которого соединен с четвертым входом первого блока памяти и с входом второго цифроаналогового преобразователя, выход которого является первым выходом устройства, 40 информационным входом которого является второй вход блока согласования, выход которого соединен с первым входом коммутатора, выход которого соединен с третьим входом первого блока памяти и входом пер45 вого цифроаналогового преобразователя, выход которого является вторым выходом

1811009

Составитель И. Скакун

Техред M.Ìîðãåíòàë Корректор

Редактор С. Кулакова

Заказ 1452 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб„4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101 вый и второй счетчики, третий блок памяти, элемент ИЛИ и блок сравнения, причем выход генератора управляющих импульсов соединен с первыми входами третьего и шестого элементов И, выходы которых соединены со счетными входами соответственно первого и второго счетчиков, выходы которых соединены со своими входами установки и соответственно с первым и вторым входами триггера, прямой выход которого соединен с вторыми входами первого, четвертого, седьмого и десятого элементов И и с третьим входом шестого элемента И, инверсный выход триггера соединен с третьим входом шестого элемента

И с вторыми входами второго, пятого, восьмого и девятого элементов И, выход аналого-цифрового преобразователя соединен с первыми входами первого и второго элементов И, выходы которых соединены с третьими входами соответствующих второго и третьего блоков памяти, выходы которых соединены с первыми входами соответствующих десятого и девятого элементов И, выходы которых соединены с входами эле5 мента ИЛИ, выход которого подключен к первому входу вычитателя, выход коммутатора соединен с первыми входами четвертого и пятого элементов И, выходы которых соединены с вторыми входами соответству10 ющих второго и третьего блоков памяти, выходы которых подключены к входам блока сравнения, выход "Равно" которого является выходом готовности к работе устройства, выход генератора управляющих импульсов

15 соединен с первыми входами седьмого и восьмого элементов И, выходы которых соединены с первыми входами второго и третьего блоков памяти, выход "Неравно" блока сравнения соединен с вторыми входа20 ми третьего и шестого элементов И.