Фильтр-реле тока

Иллюстрации

Показать всеРеферат

Сущность изобретения: введение канала , определяющего знак приращения амплитуды контролируемого сигнала и включающего формирователь средневыпрямленного значения, двухполупериодный выпрямитель, компаратор, RS-триггер, первый и второй элементы И, второй элемент НЕ, позволяет повысить чувствительность-в условиях изменения нагрузки. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК., . Ж „„1814131 А1 (51)я Н 02 Н 3/08

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

1фл,. „„ "" <.:. А,э,, ., э;,»э р;т,л

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

2 т (54) ФИЛЬТР-РЕЛЕ ТОКА (57) Сущность изобретения. введение канала, определяющего знак приращения амплитуды контролируемого сигнала и включающего формирователь средневыпрямленного значения, двухполупериодный выпрямитель, компаратор, RS-триггер, первый и второй элементы И, второй элемент

Н Е, позволяет повысить чувствительность- в условиях изменения нагрузки. 1 ил.

1 (21) 4922932/07 (22) 04.02.91, (46) 07.05.93, Бюл. hh 17 (71) Ленинградский государственный технический университет (72) А.И.Таджибаев, С.В.Чурсин: и П.М.Ширнин (561 Авторское свидетельство СССР

ЬЬ 1541700, кл. Н 02 Н 3/08, 1987.

Авторское свидетельство СССР

hh 1697138, кл, Н 02 Н 3/08, 1991. л

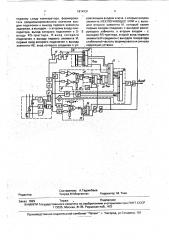

Изобретение относится к области авто- чающий аналого-цифровой преобразова- з матизации энергетических систем и может тель 29 и цифровой компаратор 30, реагирубыть использовано в релейной защите. и ющий элемент 31. Формирователь противоаварийной автоматике. средневыпрямленного значения 33, двухпоЦель изобретения — повышение чувст- лупериодный выпрямитель 34, компаратор вительности устройства в условиях измене- 35, RS-триггер 36, элементы И 32 и 37 и ния нагрузки. элемент НЕ 38.

На чертеже представлена схема фильтр- " Устройство работает следующим обра- ь реле тока. Фильтр-реле тока содержит фор- зом, На выходе формирователя 1 формиру- СО мирователь 1 контролируемого сигнала, ется сигнал 4 в виде напряжения,. включающий трансформаторы 2-4 тока; пропорциональнОго току прямой, обратной входные преобразователи 5-7 тока и фильтр или нулевой последовательности, или их

8симметричных составляющих, первый зле- комбинации. На выходе сумматора 27 выде мент задержки 10, фильтр 9 прямой после- ляется аварийная составляющая сигнала 0» Ы довательнрсти, амплитудный детектор 11, путем суммирования eio с выходным сигнаэлемент задержки йа срабатывание 12, эле- лом элемента задержки 10, представляюмент НЕ 13, элемент т1НЕ 14, элемент ИС- щим собой фелоний . фнлэтр с )»

КЛЮЧАЮЩЕЕ ИЛИ 15, блок формирования коэффициентом передачи по амплитуде, уставки 19, включающий фазовый детектор равным единице, и фазовым запаздывани20, второй элемент задержки 21, генератор ем, равным 1800, на частоте 50 Гц. Цифростабильной частоты 22, счетчик 23 и регистр вым компаратором 30 сравнивающего памяти 24, цифровой сумматор 25, ключ 26, блока 28 производится сравнение кода анасумматор 27, сравнивающий блок 28, BKhl0- . лого-цифрового преобразователя 29 Кцк и т

1814131 кода на выходе цифрового сумматора 25

Куст. Причем Куст - Козу + N op, где Кьзу— код на выходе мультиплексора 18, Ккор— код на выходе регистра памяти 24 блока 19 формирования сигнала коррекции уставки.

Значение кода уставки Козу может принимать два значения — N1 и N2, в зависимости от режима работы защищаемой линии. При частоте сигнала UK, равной 50 Гц, значение

N

36 и амплитудного детектора 11 соответствует логическому нулю. При этом ключ 26 замкнут, на выходе элемента И-НЕ 14 формируется сигнал логической единицы. В результате на выходе мультиплексора 18 в виде и-разрядного кода коммутируется уставка по входу Х вЂ” N1, заданная в формирователе кода уставок 17, путем подключения соответствующих входов Х1...Xp к шинам с потенциалами логических нуля и единицы, Уставка N1 выбирается исходя из отстройки макс

От МаКСИМаЛЬНОГО тОКа СаМОЗаПУСКа Iaap .Т,е. N1 k laan, ГДЕ k КОЭффИцИЕНТ преобразования, При включении линии под нагрузку на выходе формирователя 1 возникает напряжение U и формируется сигнал на выходах сумматора 27 и компаратора 35. Но этот сигнал не приводит к срабатыванию реагирующего элемента 31 и, следовательно, первого элемента 2И-HE 32, т.к. Nuy, < Куст =

Козу = N1. Появление напряжения нулевой последовательности приводит к срабатыванию амплитудного детектора 11 и с задержкой элемента 12 задержки на срабатывание.

Величина временц задержки определяется максимально возможной длительностью переходного процесса в элементе 10 задержки. После перехода в состояние логической единицы элемента 12 на выходе элемента

И-НЕ 14 появляется логический нуль. В результате на выходе мультиплексора 18 коммутируется уставка по входу Y-N2, определяемая исходя из величины.наибольшего броска тока нагрузки в нагрузочном рЕжИМЕ!нагр 6Р, N2 k нагр бР. ОЧЕВИДНО при этом, что N2 < N1..

В случае включения линии из отключенного состояния на короткое замыкание величина напряжения на выходе сумматора 27 пРевышает УставкУ N1, т.е. Nu > Куст = N1

Реагирующий элемент и элемент И 32 срабатывают, и линия отключается, В случае возникновения короткого замыкания на линии, включенной под нагруэ50

В случае отключения нагрузки защищаемой линии уровень скачка напряжения на выходе сумматора 27 и соответственно в цифровом коде на выходе преобразователя

29 также оказывается выше значения N2, срабатывает цифровой компаратор 30 и реагирующий элемент 31, на первый вход элемента И 32 поступает логическая единица.

Но выходной сигнал двухполупериодного выпрямителя 34, поступающий на неинвертирующий вход компаратора 35. оказываетку, уровень скачка напряжения на выходе сумматора 27 и соответственно в цифровом коде на выходе преобразователя 29 оказывается выше значения N2, срабатывает цифровой компаратор 30 и реагирующий элемент 31, на йервый вход элемента И 32 поступает логическая единица. Одновременно сигнал с выхода формирователя контролируемого сигнала поступает на вход

"0 двухполупериодного выпрямителя 34, на выходе которого формируются положительные полуволны напряжения, а через элемент задержки 10 — на вход формирователя средневыпрямленного значения ЗЗ. На выходе формирователя 33 появляется сигнал постоянного уровня, поступающий через цепи делителя напряжения на инвертирующий вход компаратора 35, на неинвертирующий вход которого через

20 соответствующий делитель напряжения поступает сигнал с выхода двухполупериодного выпрямителя 34, Параметры делителей напряжения выбираются так, что напряжение на инвертирующем входе было больше, 25 чем на неинвертирующем входе. В режль.тате этого компаратор 35 формирует импульсы, поступающие на S-вход

RS-триггера 36, íà R-вход которого поступают импульсы с генератора стабильной час30 таты 22 через элемент И 37. На выходе

RS-триггера 36 формируется сигнал логической единицы, поступающий на второй вход элемента И 32 и переводящий его в состояние логической единицы. Срабатывание

35 фильтра-реле тока приводит к размыканию ключа 26, обеспечивая надежное самоудерживание устройства в сработанном состоянии и подаче через элемент НЕ 38 логического нуля на первый вход элемента

40 И 37, с выхода которого сигнал логического нуля, поступающий на R-вход триггера 36 самоудерживает его в сработанном состоянии. Элемент И-НЕ 14 переходит в состояние логической единицы и в блоке задания уставок 16 происходит переключение уставки с N2 íà N1, Под действием выходного сигнала элемента И 32 происходит отключение защищаемой линии, и фильтр-реле тока возвращается в исходное состояние.

20

Ок импульс нулевого уровня, длительного .которого вафд пропорциональна отклойе нию частоты Ок, Генератор 22 вырабатывает 30 импульсы с частотой 1ги, которыми наполняется счетчик 23 за время вафд,.Сигнал в виде кода Йкор переписывается из счетчика 23 в регистр 24 памяти в момент появления импульса единичного уровня на выходе детек- 35 тора 20. Элемент задержки 27 В виде

RC-цепи служит для задержки noñòóïëåêèÿ импульса единичного уровня на R-вход счетчика 23 с целью надежного считывания кода

N

К д

Nypp > МнБ. ЗагРУбление фильтРа-Реле тока в этом случае происходит только при f =- 55

=тном.

Таким образом, введение канала, определяющего. знак приращения амплитуды контролируемого сигнала. позволяет обесся меньше. чем выходной сигнал формирователя средневыпрямленного значения 33, поступающий на инвертирующий вход компаратора 35, 8 результате этого на выходе компаратора 35 присутствует сигнал логического нуля, поступающий на S-входтриггера

36 и не приводящий к его срабатыванию, Следовательно, логический нуль, поступающий с выхода триггера 36 на второй вход элемента И 32, блокирует его срабатывание и соответственно всего устройства в целом.

При работе на номинальной частоте

fHoM входное и выходное напряжения элемента 10 задержки находятся в противофазе. На выходе фазового детектора 20 формйруется сигнал логической единицы, через элемент задержки 21 удерживая счетчик в обнуленном состоянии. В результате

Ngpp = О.„При отклонении частоты сигнала от номинальной (f + f p ) на выходе сумматора 27 возникает напряжение небапанса

Оне, а на выходе аналого-цифрового преобразователя 29 — код небаланса ИнБ, Одновременно фазовый сдвиг. входного и выходного напряжений элемента задержки

10 становится отличным на 1800, на выходе детектора 20 появляется дважды за период а где Кд — коэффициент деления счетчика 23.

Работа формирователя сигнала коррекции уставки идентична при f < 1н,м и f > fop, Цифровым сумматором 25 производится сложение КОДОВ |чБзУ и Nxpp т е Иуст = — N

Формула изобретения

Фильтр-реле тока, содержащий форми5 рователь контролируемого сигнала, выполненный в виде входных преобразователей тока, подключенных Входами к соответствующим трансформаторам тока линии, а выходами к входал1 фильтра симметричных составляющих, ВыхОд которого яВляется Выходом формирователя контролируемого сигнала и подключен к первому входу сумматора и через последовательно соединенные,первый элемент задержки и

5 информационный вход ключа к второму входу сумматора, выход которого соединен с первым входом сравнивающего блока. Выход которого соединен с входом реагирующего элемента, к выходам входных преобразователей тока формирователя контролируемого сигнала подключены последовательно соединенные фильтр прямой последовательности, амплитудный детектор и элемент задержки на срабатывание, 5 выход последнегО подключен к первому входу элемента MCKflfO×ÀÞÙEÅ ИЛИ и первому входу элемента И-НЕ, Второй вход которого соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, а выход — с первым входом блока задания уставки и с входом первого элемента НЕ, выход которого подключен к второму входу блока задания уставки, выход которого соединен с первыми входами цифрового сумматора, к вторым входам которого подключен выход формирователя сигнала коррекции уставки, выполненного В виде генератора стабильной частоты и последовательно соединенных фазового детектора, второго элемента задержки, R-входа счетчика и 0-входов регистра памяти, причел первый и второй входы фазового детектора подключены соответственно к входу и выходу первого элемента задержки, выход генератора стабильной частоты подключен к S-входу счетчика, выход фазового детектора также подключен к Свходу регистра памяти, выход которогс является выходом формирователя сигнала коррекции сигнала, выходы цифрового сумматора подключены к вторым входам сравнивающего блока, отличающийся тем, что, с целью повышения чувствительности в условияхизменения нагрузки, B негодополнительно Введены формирователь средневып° рямленного значения, двухполупериодный выпрямитель, компаратор, RS-триггер, первый и второй элементы И и второй элемент НЕ, причем двухполупериодный выпрямитель входом подключен к выходу формирователя контролируемого сигнала, а выходом — к

Составитель А.Таджибаев

Техред M.Ìîðãåíòàë Корректор М. Ткач

Редактор

Заказ 1829 Тираж . Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГККТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

П оиэводственно-издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101 роиэв

7 1814131 8

t первому ьходу компаратора, формирова- равляющим входом ключа, с вторым входом тель средневыпрямленного значения вхо- элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с выходом подключен к выходу первого элемента дом второго элемента И, который своим задержки, а выходом — к второму входу ком- первым входом соединен с выходом реагипаратора, выход которого подключен к $- 5 рующего элемента. а вторым входом — c входу RS-триггера, R-вход которого выходом RS-триггера. второй вход первого подключен к выходу первого элемента И, элемента И соединен с выходом генератора первый вход которого подключен к выходу стабильной частоты формирователя сигнала элемента НЕ, вход которого соединен с уп- . коррекции уставки.