Устройство для контроля микропроцессорной системы

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано для построения микропроцессорных систем на базе микропроцессора КР580ИЕ80А. Целью изобретения является повышение достоверности контроля. Цель достигается путем введения в устройство триггеров 2, 3, 4, 5, схем сравнения 10 и 11, элемента И 13, инвертора 15. Сущность изобретения состоит в обнаружении простоев микропроцессорной системы и увеличении числа контролируемых управляющих сигналов , формируемых на шине управления. 6 ил. ел с

союз соВетских социАлистических

РЕСПУБЛИК (я)5 G 06 F 11/00

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) ОПИСАНИЕ ИЗОБРЕТЕНИ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4880867/24 (22) 02.11.90 (46) 15.05.93, Бюл. ЬЬ 18 (72) М.П.Ткачев, М.В.Талейко и В.Ю.Пикин (56) Авторское свидетельство СССР

М 1417649, кл. G 06 F 11/00, 1988.

Авторское свидетельство СССР

М 1460722, кл. G 06 F 11/00, 1989. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ МИКРОПРОЦЕССОРНОЙ СИСТЕМЫ (57) Изобретение относится к автоматике и вычислительной технике и может быть ис„„ Ж„„1815638 А1 пользовано для построения микропроцессорных систем на базе микропроцессора

КР580ИЕ80А. Целью изобретения является повышение достоверности контроля. Цель достигается путем введения в устройство триггеров 2, 3, 4, 5, схем сравнения 10 и 11, элемента И 13, инвертора 15. Сущность изобретения состоит в обнаружении простоев микропроцессорной системы и увеличении числа контролируемых управляющих сигналов, формируемых на шине управления. 6 ил.

1815638

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении микропроцессорных систем на базе микропроцессора

КР580 ИЕ80А.

Целью изобретения является повышение достоверности контроля.

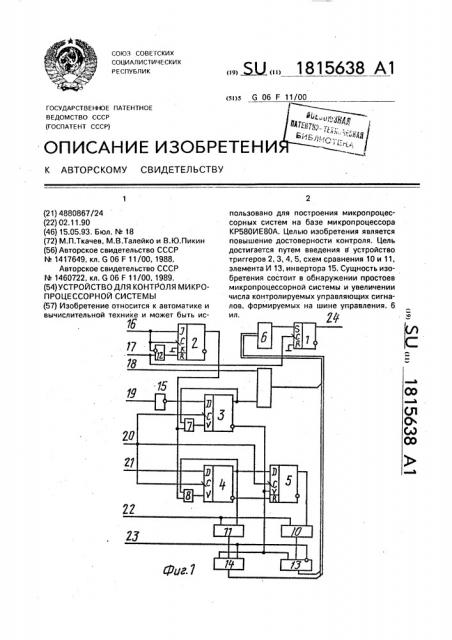

На фиг. 1 изображена функциональная схема устройства; на фиг.2-5 — временные диаграммы работы устройства в различных режимах, где использованы обозначения, введенные на фиг.1; на фиг.6 — алгоритм функционирования микропроцессора серии

К580ИКЯОА в режимах "ожидание" и "захват".

Устройство (см.фиг.1) содержит первый

1, второй 2, третий 3, четвертый 4 и пятый 5 триггеры, первый 6, второй 7 и третий 8 элементы ИЛИ, первую9, вторую 10 и третью 11 схемы сравнения, первый 12, третий 13 и второй 14 элементы И, элемент НЕ

15.

Входы устройства 16 — 23 соединены соответственно с входами (выходами) микропроцессора SYNC, F1, WAIT, READY, Fz, HOI О, HLDA, DBIN, Рассмотрим назначение элементов устройства (фиг.1). Первый триггер 1 предназначен для фиксации несовпадения сигналов, вырабатываемых микропроцессором и вырабатываемых устройством контроля, Фиксация осуществляется по каждому заднему фронту (спаду) синхроимпульсов . F>, формируемых микропроцессором. В исходном состоянии триггер установлен в "0", в случае ошибки (неисправности) микропроцессорной системы триггер устанавливается в 1". Триггер может быть выполнен на базе двухступенчатого RSC-триггера. Цели его начальной установки условно не показаны.

Второй триггер 2 предназначен для определения начала машинного цикла, Триггер по каждому импульсу БУМС, вырабатываемом микропроцессором в начале каждого машинного. цикла, устанавливается в единичное состояние, разрешая работу триггеров 3 и 4. Затем в каждом цикле триггер устанавливается в нулевое состояние, Триггер может быть выполнен на базе двухступенчатого ICK-триггера, Третий триггер 3 предназначен для фиксации сигнала запроса режима "ожидание", поступающего с выходом элемента НЕ15.

УсТВНоВКВ триггера осуществляется по заднему фронту синхроимпульсов фазы Fg микропроцессора: при установке в единичное состояние — синхроимпульсов Гр второ5

55 го такта (T2) работы микропроцессора, а при установке в нулевое состояние — синхроимпульсов того такта, в котором был снят запрос на "ожидание", Работа триггера 3 соответствует логике формирования сигнала на выходе микропроцессора WAIT. Триггер 3 может быть выполнен на

D С\/-триггере.

Четвертый 4 и пятый 5 триггеры предназначены для фиксации сигнала запроса состояния "захват" HOLD. поступающего на информационный вход четвертого триггера

4. Опрос и фиксации сигнала триггером 4 осуществляется по заднему фронту синхроимпульсов фазы Fz второго такта ТК (сигнал

"1" — запроса на "захват") и в каждом такте, следующем на Т2 (сигнал "0" — снятие запроса на "захват"), Пятый триггер 5 осуществляет опрос и фиксацию сигнала HOLD по синхроимпульсу фазы Fz такта ТЗ (сигнал "1" запрос на

"захват" и по синхроимпульсу Fz в каждом такте следующем на ТЗ, т.е. в тактах состояния "захват" (сигнал "0" запроса на "захват"). Оба триггера 4 и 5 формируют на своих прямых выходах сигналы подтверждения состояния "захват" в соответствии с логикой формирования аналогичного сигнала на выходе HLDA микропроцессора, Четвертый 4 и пятый триггеры могут быть вы пол не н ы на базе двухступенчатой D CVтриггеров. Формирование триггерами 3, 4 и

5 на своих выходах сигналов, точно соответствующих сигналам. формируемым микропроцессором. осуществляется по алгоритму функционирования микропроцессора, приведенному на фиг.6.

Первый элемент 6 ИЛИ предназначен для обобщения сигналов, формируемых на выходах схем сравнения 9 и третьего 13 и второго 14 элементов И.

Второй 7 и третий 8 элементы ИЛИ предназначены для разрешения работы третьего 8 и четвертого 4 триггеров в тактах. следующих за вторым, когда триггер 2, управляющий работой этих триггеров. уже сброшен в ноль и не обеспечивает опрос триггером 3 сигнала READY по импульсу фазы Fz в режиме "ожидание" и триггером 4 сигнала НО(О по импульсу фазы Fz в режиме "захват".

Первая 9, вторая 10 и третья 11 схемы сравнения предназначены для проверки правильности формирования микропроцессором сигналов подтверждения состояний

"ожидание" и "захват" (формируемых микропроцессором на выходах WAIT u HLDA соответственно) и аналогичных сигналов, 1815638 формируемых устройством контроля на выходах триггеров 4, 5 и 3.

Элементы И 13 и 14 предназначены для передачи сигнала несовпадения с выходов схем сравнения 10 и 11 соответственно в требуемые моменты времени, т.е. в точном соответствии с алгоритмом, приведенном на фиг,6.

Первый элемент 12 И предназначен для сброса второго триггера 2 в,ноль в каждом машинном цикле микропроцессора. Установка в ноль второго триггера осуществляется в такте, следующим за вторым тактом, по синхроимпульсу F>; . Элемент НЕ 15 предназначен для преобразования сигнала "готовность" (READY) в ийверсный сигнал, Это позволяет идентифицировать сигнал "готовность" в состоянии м1н на выходе инвертора — как сигнал запроса режима "ожидание", а в состоянии н0" — как сигнал отсутствия запроса.

Рассмотрим работу устройства. Для него характерны три режима работы (в соответствии с. алгоритмом,, приведенным на фиг.6):

1. Контроль режима "ожидание" (см.фиг.2, фиг.6);

2. Контроль режима "захват" в циклах .чтения и ввода или записи и. вывода (см.фиг.3, фиг.4, фиг.б);

3. Контроль режимов "ожидание" и нзахват" при одновременном запросе (см.фиг.5, фиг,б).

Устройство работает следующим образом.

В исходном состоянии все элементы па-. мяти находятся в нулевом состоянии (цепи сброса в нОм условно не погказайы).

В первом режиме (см.фиг.2, фиг.6) в каждом машинном, цикле по заднему фронту сигнала SYNG, поступающего на вход 16 устройства (см.фйг.2), срабатывает триггер

2 устанавливаяСь в состояние н1н (момент времени t2 íà фиг. 2 ) и разрешая тем самым запись сигнала READY (выход 15 на фиг,2) по заднему фронту импульса фазы Ег такта

Т2. При наличии сигнала запроса на "ожидание" READY = 1. Триггер 3 устанавливается в единичное состояние (момент времени т, фиг.2) формируя на своем прямом выходе копию сигнала подтверждения состояния

"ожидание", .аналогично формируемому микропроцессором сигналу на выходе

WAIT. Единичное состояние триггера 3 через элемент 7ИЛИ подтверждает сигнал разрешения записи информации с выхода йЕД13У на входе V триггера 3, в то время как второй триггер 2, ранее разрешающий рабому режиму во втором такте 12 осуществляется выработка единичного управляющего импульса на прямом выходетриггера2(промежуток времени ti...t4 фиг.3, фиг.4). Этот импульс разрешает работу четвертого триггера 4, который опрашивает сигнал HOLD no

55 заднему фронту импульса фазы Ег. В случае, если появился запрос "захват" (HOLD = 1 ), ту триггера 3, устанавливается в нулевое состояние по переднему фронту импульса фазы F1 в такте, следующим эа тактом Т2 (см.фиг.2)..

Таким образом, за счет единичного сигнала на выходе элемента Т ИЛИ тр иггер 3 осуществляет опрос сигнала READY в каждом такте Tw(такты состояния ножидание") по синхроимпульсу фазы Ер. При пропадании сигнала READY = 1, что соответствует снятию запроса на "ожидание", по заднему фронту импульса фазы Ег (момент м4 см.фиг.2) триггер 3 устанавливается в нулевое состоя н ие, блокируя свою работу до следующего такта Т2 (за счет нулевого сигнала на выходе элемента 7 ИЛИ, момент t5 на фиг.2). Установка. триггера 3 в нулевое состояние имитирует выход микропроцессора

20 иэ состояния "ожидания" и соответствующую этому установку нулевого уровня сигнала подтверждения "ожидания". На аналогичном выходе WAIT микропроцессора также формируется нулевой сигнал по переднему фронту импульса фазы F<. Таким образом, на выходе триггера 3 и выходе . триггера 3 и выходе микропроцессора WAIT формируются синхронные сигналы, которые сравниваются схемой сравнения 9. Реэуль30 тат сравнения фиксируется в триггере 1 по заднемуфронту импульса фазы F>. Дальнейшее распространение сигналов на выходах второй 10 и третьей 11 схем сравнения в режиме "ожидание" блокируется при помо35 щи элементов 13 и 14И, посредством нулевого сигнала на инверсном выходе 3 . (промежуток времени t>.. tq см.фиг.2). B дальнейшем работа устройства аналогична рассмотренной выше.

40 В случае отсутствия сигнала READY = 1 триггер 3 будет установлен в н0", и сигнал, соответствующий сигналу подтверждения ножидания", генерироваться не будет, подобно тому, как и не будет генерироваться

45 сигнал на выходе WAIT микропроцессора.

Йри этом триггер 1 останется в нулевом состоянии (в случае правильной работы).

Во втором режиме, когда осуществляется переход микропроцессора в состояние

50 "захват" и выход иэ него (при отсутствии запроса на "ожидание"), аналогично перво1815638

40

55 в момент времени (см.фиг.3, 4) триггер 4 устанавливается в единичное состояние аналогично тому, как микропроцессор "извещает" о переходе в состояние "захват" сигналом HLDA = 1 устанавливаемым по пе- 5 реднему фронту F> такта Т* (см.фиг.3, 4), Единичное состояние триггера 4 снимает сигнал при длительной установки в ноль на

R-входе триггера 5. Особенностью микропроцессора КР580 ИК80А является зависимость перехода в состояние "захват" от типа выполняемого цикла. Если выполнялся циклчтения или вода, то переход в состояние

"захват" осуществляется в такте, следующем за Т2, а если цикл записи или вывода—

15 то в такте следующем на ТЗ. Эта особенность учтена в работе устройства при помощи триггера 5. В циклах чтения или ввода, когда сигнал DBIN = 1, осуществляется 20 сравнение сигнала микропроцессора HLDA и сигнала, формируемого на выходе триггера 4 (момент времени тз фиг.3, см,выходы 22, 4). Сравнение обеспечивается наличие разрешающего сигнала DBIN на входе.элемента 14И, пропускающего результат сравнения на вход элемента ИЛИ, Результат сравнения фиксируется триггером 1 по каждому заднему фронту импульсов фазы

Ft. В циклах записи или ввода сравнение сигнала HLDA осуществляется с сигналом, формируемым на выходе триггера 5, Установка триггера 5 в единичное состояние осуществляется с задержкой на один такт, т.е. в такте, следующим за Т3 (момент ts фиг.4). В этом случае сигнал DBIN = О, и сравнение осуществляется схемой сравнения 10, так как элемент 14 И заблокирован, В процессе дальнейшего функционирования в тактах захвата Т* осуществляется onрос сигнала HOLD по заднему фронту импульса фазы Fz триггером 4. В случае, если сигнал запроса на "захват" снят (HOLD=

= О), триггер 4 устанавливается в нулевое состояние (момент времени t5 — фиг.3/t6— фиг,4), устанавливая триггер 5 в ноль с некоторой задержкой, равной времени срабатывания триггера. В обоих случаях (в любых циклах) выход из состояния "захват" микропроцессор осуществляет по переднему фронту такта Т1 (см.фиг. 3, 4, фиг.б). Сигнал результата сравнения, поступающий через элементы 13 и 14, фиксируется в триггере 1 по заднему фронту синхроимпульса Ft.

В третьем режиме, когда запросы на состояния "ожидание" и "захват" поступают одновременно (относительно импульса F2 в такте T2). работа элементов устройства аналогично работе в первом и втором режимах.

Особенностью является то, что сначала выполняется режим ("ожидание", а потом "захват"), Это обеспечивается тем, что в режиме "ожидание" триггер 3 находится в единичном состоянии (интервал времени

t2".t3 фиг.5), блокируя состояние "0" на своем инверсном выходе работу триггера 5 и передачу сигналов сравнения через элементы 13 и 14И.

При снятии сигнала "0" с инверсного выхода триггера 3 (по окончании режима

"ожидание") осуществляется установка в единичное состояние триггера 5 через так, а также разрешение на передачу результатов сравнения через элементы 13. 14 И в зависимости от типа цикла, В дальнейшем работа устройства полностью определяется работой во втором режиме.

Следует отметить, что при работе устройства на выходах элементов 7 и 8 ИЛИ в такте, следующим Т2 (см.фиг.2 — 4), возможны кратковременные перепады сигналов, связанные с асинхронностью срабатывания триггеров 2 и 3 (4). Однако, влияние указанных переходных процессоров на работу триггеров 3 и 4 не происходит из-за синхронизации по сигналу Fz, Переходные процессы (см.фиг.5, интервал ta...tü) связаны с асинхронностью сравниваемых сигналов WAIT и на выходе триггера 3, ILDA и на выходах триггера 4 и

5, могут привести к ложному срабатыванию триггера 1. С целью устранения данного эффекта необходимо выбирать быстродействие элемента, исходя из того, что срабатывание самой длинной цепочки сравнения сигналов должно заканчиваться к моменту прихода заднего фронта синхроимпульса F>, т.е. должно выполняться условие:

— время срабатывания соответственно элементов: триггера DCV, сумматора по модулю 2, элементов И и ИЛИ.

Формула изобретения

Устройство для контроля микропроцессорной системы, содержащее первую схему сравнения, с первого по третий элементы

ИЛИ, первый и второй элементы И. первый триггер, причем выход первой схемы сравнения соединен с первым входом первого элемента ИЛИ, выход первого триггера является контрольным выходом устройства, 1815638

10 о т л и ч а ю щ е е с я тем, что, с целью повышения достоверности контроля, в него дополнительно введены с второго по пятый триггеры, третий элемент И, элемент

НЕ, вторая и третья схемы сравнения, причем первый вход устройства соединен с выходом сигнала начала машинного цикла контролируемой микропроцессорной системы, с единичным входом и синхровходом второго триггера, инверсным входом первого элемента И, второй вход устройства соединен с первым выходом синхронизации контролируемой микропроцессорной системы, с входом синхронизации первого триггера и прямым входом первого элемента И, выход которого соединен с установочным входом второго триггера, нулевые входы первого и второго триггеров соединены с шиной нулевого потенциала, контролируемой микропроцессорной системы, третий вход устройства соединен с выходом подтверждения состояния "ожидание" контролируемой микропроцессорной системы и с первым входом первой схемы сравнения, четвертый вход устройства соединен с входом запроса на "ожидание" контролируемой микропроцессорной системы и через элемент НŠ— с информационным входом третьего триггера, прямой выход которого соединен с вторым входом. первой схемы сравнения, и первым входом второго элемента ИЛИ, второй вход которого соединен с прямым выходом второго триггера, выход второго элемента ИЛИ соединен с разрешающим входом третьего триггера, пятый вход устройства соединен с вторым выходом синхронизации контролируемой Микропроцессорной системы и входами синхронизации с третьего по пятый триггеров, шестой вход устройства соединен с входом запроса на

"захват" контролируемой микропроцессорной системы и информационным входом

5 четвертого триггера, прямой выход которого соединен с первым входом третьего элемента ИЛИ, второй вход третьего элемента

ИЛИ соединен с прямым выходом второго триггера, выход третьего элемента ИЛИ со"О единен с разрешающим входом четвертого триггера, прямой выход которого соединен с первым входом третьей схемы сравнения» и информационным входом пятого триггера, разрешающий вход которого соединен с инверсным выходом третьего триггера, инверсный выход четвертого триггера соединен с установочным входом пятого триггера, прямой выход которого соединен с первым входом второй схемы сравнения, вторые входы второй и третьей схем сравнения соединены с седьмым входом устройства, соединенным с выходом подтверждения состояния

"захват" контролируемой микропроцессорной системы, восьмой вход устройства соединен с выходом сигнала чтения контролируемой микропроцессорной системы и первыми входами второго и третьего, элементов И, вторые входы второго и треть30 его элементов И соединены соответственно с выходами второй и.третьей схем сравнения, третьи входы второго и третьего элементов И соединены с инверсным выходом триггера, выходы второго и третьего элеЗ5 ментов И соединены соответственно с вторым и третьим входами первого элемента

ИЛИ, выход которого соединен с единичным входом первого триггера.

1815638

47

Уб

1815638

/7

1815638

Составитель Д.Ванюхин

Техред М,Моргентал Корректор И.Муска

Редактор

Заказ 1636 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101