Устройство для ортогонального преобразования цифровых сигналов по уолшу-адамару

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано в аппаратуре обработки сигналов , сжатия информации при передаче данных , для анализа и обработки звуковых и видеосигналов, для цифровой фильтрации и т.д. Целью изобретения является повышение производительности устройства для ортогонального преобразования цифровых сигналов по Уолшу-Адамару за счет разбиения каждого пакета из 2М/отсчетов на два параллельных потока, что позволяет для базовой операции в каждом такте любой интеграции использовать сразу два отсчета. Устройство ортогонального преобразования цифровых сигналов по Уолшу-Адамару содержит генератор 1 тактовых импульсов, счетчик 2, сумматор-вычитатель 3, первый 4 и второй 5 блоки сдвиговых регистров, блоки 6-11 элементов ИЛИ, блоки 12-25 элементов И. 3 ил. &

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (si)s G 06 F 15/332

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) ОПИСАНИЕ ИЗОБРЕТЕНИ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Ь» (21) 4883681/24 . (22) 19,11;90 (46) 15.05.93. Бюл. N 18 (71) Конструкторское бюро злектроприборостроения (72) Н.К.Байда, Ю.Г.Нестеренко, К,Ю.Воробьев, Г,Н.TMMoHbKMH. В,С,Харченко и

С,Н.Ткаченко (56) Авторское свидетельство СССР

N- 620974, кл. G 06 Е 15/332, 1976.

Авторское свидетельство СССР

М 1234847, кл, G 06 F 15/332, 1984. (54) УСТРОЙСТВО ДЛЯ ОРТОГОНАЛЬНОГО ПРЕОБРАЗОВАНИЯ ЦИФРОВЫХ СИГНАЛОВ ПО УОЛШУ вЂ” АДАМАРУ (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано в аппаратуре обработки сигна„„SU „„1815650 А1 лов, сжатия информации при передаче данных, для анализа и обработки звуковых и видеосигналов, для цифровой фильтрации и т.д. Целью изобретения является повышение производительности устройства для ортогонального преобразования цифровых сигналов по Уолшу — Адамару за счет разбиения каждого пакета из 2й/отсчетов на два параллельных потока, что позволяет для базовой операции в каждом такте любой интеграции использовать сразу два отсчета.

Устройство ортогонального преобразования цифровых сигналов по Уолшу — Адамару содержит генератор 1 тактовых импульсов, счетчик 2, сумматор-вычитатель 3, первый 4 и второй 5 блоки сдвиговых регистров, бло- Я ки 6 — 11 злементов ИЛИ, блоки 12 — 25 злементов И. 3 ил.

1815650 режиме сумматора.

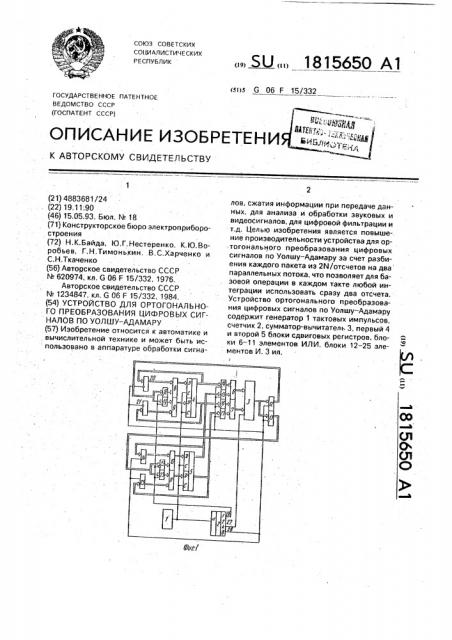

Изобретение относится к автоматике и вычислительной технике и может быть использовано в аппаратуре обработки сигналов, сжатия информации при передаче данных, для анализа и обработки звуковых и видеосигналов, для цифровой фильтрации и т.д, Цель изобретения — повышение производительности, На фиг.1 представлена функциональная схема устройства ортогонального преобразования цифровых сигналов по Уолшу — Адамару для случая 2 = 8; на фиг,2 — временные диаграммы функционирования устройства; на фиг.3 — граф-схема алгоритма ортогонального преобразования цифровых сигналов по Уолшу — Адамару.

Устройство ортогонального преобразования цифровых сигналов по Уолшу — Адамару содержит генератор 1 тактовых импульсов, счетчик 2, сумматор — вычитатель

3, первый 4 и второй 5 блоки сдвиговых регистров, блоки 6 — 11 элементов ИЛИ, блоки 12-25 элементов И обозначены первый

26, N-й 27 и (N+1)-й 28 выходы счетчика 2, На фиг.2 использованы обозначения, принятый на фиг.1, На фиг.3 приняты следующие обозначения: Х1, X2„...Õ8 обозначены входные отсчеты; У1, Y2„...Y8 — выходные отсчеты — коэффициенты Уолша-Адамара.

Рассмотрим назначение основных элементов устройства.

Генератор 1 предназначен для формирования последовательности тактовых импульсов; синхронизирующих работу устройства.

Счетчик 2 предназначен для формирования признаков четности тактов, четности итераций, а также сигнала управления сумматором-вычитателем.

Сумматор — вычитатель служит для выполнения над отсчетами А и В, поступающими соответственно на его первый и второй информациоуные входы, базовой операции.

Единичный сигнал на управляющем входе сумматора-вычитателя переводит его в режим сумматора, нулевой — в режим вычитателя. В целом сумматор — вычитатель функционирует также как и в прототипе.

Базовая операция алгоритма заключается в вычислении по формулам:

Ап+В --Cn

I I I

An — Bn = Dn

1 I I где An u Bn — входные отсчеты рля I-й ите1 рации (для 2 = 8)! =- 1,2,3, n = 2 — номер баэовой операции), при I = 1 А, и В явля1 1 ются входными отсчетами из группы Хп, A1 =-X1,A2 =Хз,Аз -X5,A4 =Х7

1 1 1 1

В1 =Хг,В2 =-Х4,Вз =-X5,В4 =Х8

Сп и Dn — результаты базовой операции в

I I

1-й итерации. принимаемые как исходные данные An и Вп для базовой операции

I+1 1+1 следующей итерации в соответствии с используемым графом алгоритма фиг.3.

Таким обоазом:

В1 = Сг, А1 = С1

В2 = С4, А2 = Сз

I+1 I+1 I

В4 =D4, А4 =0з

После выполнения последней итерации

1 =3 результатами базовых операция будут являться коэффициенты Уолша, упорядоченные по Адамару, поичем;

У1 =С1 У2 =Сг,уз =СЗ,У4=С} ", У5 =01,У6 =02 У7 =03,У8=04" где k = 1, 2, 3„. — номер группы входных отсчетов, Первый 4 и второй 5 блоки сдвиговых регистров предназначены для приема, хранения и последовательной выдачи соответствующих отсчетов. По первому входу первый 4 блок последовательно принимает хранит и последовательно вйдает на пер1 вый выход отсчеты А„, где 1= 1,3,п=1,4, аналогично по второму входу он принимает отсчеты В, где! =1,3,iI=1,4 и выдает их на

1 свой второй выход, Порядок функционирования блоков регистров не отличается от аналогичных блоков в прототипе.

Второй 5 блок аналогично по первому вход-выходу работает с отсчетами Сп, 1=1,3,n=1,4, по вторым Dn, l=1,3,n=1,4.

Рассмотрим порядок функционирования устройства ортогонального преобразования цифровых сигналов по

Уолшу-Адамару в целом, B исходном состоянии счетчик 2 обнулен, в первом 4 блоке сдвиговых регистров записаны на последовательных адресах отсчеты

А1,А2,АЭ,А4 иВ1,В2,Вз,В4 (Цепи установки элементов устройства в исходное состояние не показаны). Состояние второго 5 блока сдвиговых регистров безразлично.

По первым четырем импульсам с выхода генератора 1 тактовых импульсов отсчеты полярно с первого и второго выходов первого 4 блока сдвиговых регистров по нулевому сигналу на выходе 28 счетчика 2 через блоки

14 и 16 последовательно поступят на первый и второй входы сумматора — вычитателя

В СЛЕДУЮЩЕМ ПОО1ЯДКЕ:

А1 и В1,А2 и В2,АЗ и ВЗ,А4 и В4, В течение этих четырех тактов сумматор-вычитатель 3 будет функционировать в

В первом такте будет сформирован отсчет С1, по заднему фронту первого им1

1815650

55 пульса через блок 22 по первому входу занесется в блок 5 сдвиговых регистров, а отсчеты А1 и 81 по этому же импульсу

1 1 вновь по первому и второму входам соответственно занесутся в блок 4 сдвиговых регистров. Во втором такте будет сформирован отсчет Сг, который через коммутатор 23

1 занесется по второму входу в блок 5 сдвиговых регистров. Отсчеты A2 и 82 вновь ока1 жутся записанными в блок 4 сдвиговых регистров. В конце четвертого TBKTB отсчеты А1 ...A4 и B1 ...84 вновь окажутся запи1 1 1 1 санными по прежним адресам в блоке 4 сдвиговых регистров, а в блоке 5 регистров по первому его входу занесутся отсчеты С1

1 и Сз, а по второму Сг и С4 .

1 i 1

В очередные четыре такта сумматорвычитатель функционирует в режиме вычитатепя. Сформированные отсчеты будут занесены в блок 5 сдвиговых регистров: по первому входу — D1 и Оз, по второму — Dz

1 1 1 и 04 . Таким образом, к концу первой итера1 ции на последовательных адресах во втором 5 блоке сдвиговых регистров окажутся записанными отсчеты: С1, Сз, D1 . Оз и

1 1 1 1

Ср, С4, Dz, D4, а в блоке 4 сдвиговых

1 1 1 1 регистров вновь занесутся отсчеты . А1,...,A4 и 81 ....В4 . Во второй итерации

1 1 устройство функционирует аналогично, с той разницей, что теперь на вход сумматора — вычитателя 3 отсчеты поступают с перBoro и второго выходов второго 5 блока сдвиговых регистров, а результаты операций заносятся в первый 4 блок сдвиговых регистров.

В конце второй итерации в первом 4 блоке сдвиговых регистров будут записаны по последовательным адресам отсчеты:

А1 ...„А4 и 81,...,84 . 8 конце третьей ите2 рации во втором 5 блоке сдвиговых регистров окажутся записанными по последовательным адресам отсчеты С1, С3, D1, D3 и С2., С4, D2 . D4, которые з являются коэффициентами Уолша-АДамара.

У1, УЗ, У5, У7 и У2, У4, Уб, УВ.

После этого устройство переходит в исходное состояние. Далее по соответствующим управляющим сигналам порядок работы устройства повторяется.

Формула изобретения

Устройство для ортогонального преобразования цифровых сигналов по УолшуАдамару, содержащее шесть блоков элементов И, три блока элементов ИЛИ, сумматор — вычитатель, два блока сдвиговых регистров, генератор тактовых импульсов и счетчик, причем выход сумматора — вычитателя соединен с первыми входами первого и второго блоков элементов И. выход, пер5

45 вый и второй входы первого блока элементов ИЛИ соединены соответственно с первым информационным входом сумматора — вычитателя. выходом третьего блока элементов И и выходом четвертого блока элементов И. выход второго блока элементов ИЛИ соединен с первым информационным входом первого блока сдвиговых регистров, первый выход которого соединен с первыми входами третьего и пятого блоков элементов И, первый вход второго блока элементов ИЛИ соединен с выходом пятого блока элементов И, первый выход второго блока сдвиговых регистров соединен с первыми входами четвертого и шестого блоков элементов И, выход шестого блока элементов И соединен с первым входом третьего блока элементов ИЛИ, выход которого соединен с первым информационным входом второго блока сдвиговых регистров, синхровход которого соединен с синхровходом первого блока сдвиговых регистров, выходом генератора тактовых импульсов и счетйым входом счетчика. о т л ич а ю щ е е с я тем, что, с целью повышения производительности, оно дополнительно содержит три блока элементов ИЛИ и восемь блоков элементов И, причем выход первого блока элементов И соединен с первыми входами седьмого и восьмого блоков элементов И, выходы которых соединены соответственно с вторым входом второго и первым входом четвертого блоков элементов ИЛИ, второй выход первого блока сдвиговых регистров соединен с первыми входами девятого и десятого блоков элементов И, выход девятого блока элементов И соединен с вторым входом четвертого блока элементов ИЛИ, выход которого соединен с вторым информационным входом первого блока сдвиговых регистров, выход десятого блока элементов И соединен с первым входом пятого блока элементов ИЛИ, выход и второй вход которого соединены соответственно с вторым информационным входом сумматора — вычитателя и выходом одиннадцатого блока элементов И, первый вход которого соединен с вторым выходом второго блока сдвиговых регистров и первым входом двенадцатого блока элементов И, выход которого соединен с первым входом шестого блока элементов ИЛИ, выход и второй вход которого соединены соответственно с вторым информационным входом второго блока сдвиговых регистров и выходом тринадцатого блока элементов И, первый вход которого соединен с выходом второго блока элементов И и первым входом четырнадцатого блока элементов И, выход которого соединен с вторым входом третьего блока

1815650 динен с управляющим входом сумматоравычитателя, выход (N+1)-го разряда счетчика соединен с вторыми входами с первого по шестой и с девятого по двенадцатый бло5 ков элементов И.

Эаа2

А-8

ЦГ.З

Составитель Ю. Ланцов

Техред М.Моргентал - Корректор Н.. Ревская

Редактор

Заказ 1637 . Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035. Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул,Гагарина. 101 элементов ИЛИ, выход первого разряда счетчика соединен с вторыми входами седьмого, восьмого, тринадцатого и четырнадцатого блоков элементов И, выход N-го разряда счетчика (где 2 — число вычисляеN мых коэффициентов преобразования) сое7