Широтно-импульсный n-фазный инвертор

Иллюстрации

Показать всеРеферат

Использование: преобразование постоянного напряжения в IM-фазное переменное напряжение в системах вторичного электропитания и электропривода. Сущность изобретения: преобразователь выполнен по N-фазной мостовой схеме с М-фазным трансформатором 1, выходным фильтром из дросселей 2.1...2.N и конденсаторов 3.1...3.N и 2N управляемых ключей. Преобразователь работает в режиме двухпозиционной следящей широтно-импульсной модуляции с пофазным независимым регулированием напряжения. При перегрузке или коротком замыкании ток ограничивается дросселями 2.1...2.N путем управления в режиме стабилизации тока. 1 з.п. ф-лы, 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„5U„„1815776 А1 (я)5 Н 02 M 7/5395

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР)

А Г

ОПИСАНИЕ ИЗОБРЕТЕНИЯ « :,"::::::-;::-::!, " .

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

М

Ма

Ое

Ъ (21) 4763327/07 (22) 28.11.89 (46) 15.05.93. Бюл. N. 18 (71) Научно-производственное объединение

". Силовая электроника" (72) В.И,Яшкин и В.Ф,Еряшев (56) Моин В.С. Стабилизированные транзисторные преобразователи,— M.: Энергоатомиздат, 1986, с. 82.

Кибакин В,М, Основы ключевых методов усиления. М.: Энергия, 1980, с. 44, (54) ШИРОТНО-ИМПУЛЬСНЫЙ ¹ÔÀÇНЫЙ ИНВЕРТОР (57) Использование: преобразование. постоянного напряжения в N-фазное переменное напряжение в системах вторичного электропитания и электропривода. Сущность изобретения; преобразователь выполнен по

N-фазной мостовой схеме с N-фазным трансформатором 1, выходным фильтром из дросселей 2.1...2.N и конденсаторов

3,1...3,N и 2N управляемых ключей, Преобразователь работает в режиме двухпозиционной следящей широтно-импульсной модуляции с пофазным независимым регулированием напряжения. При перегрузке или коротком замыкании ток ограничивается дросселями 2.1...2.N путем управления в режиме стабилизации тока. 1 з.п. ф-лы, 3 ил, 1815776

Изобретение относится к преобразовательной технике и может использоваться в качестве преобразователя постоянного напряжения в переменное синусоидальное, различной фазности, Целью изобретения является повышение надежности работы N-фазного инвертора путем ограничения пусковых зарядных токов, получение синусоидальной формы выходного напряжения, его широтно-импульсного пофазного регулирования и ограничения токов через управляемые ключи при перегрузке и коротком замыкании.

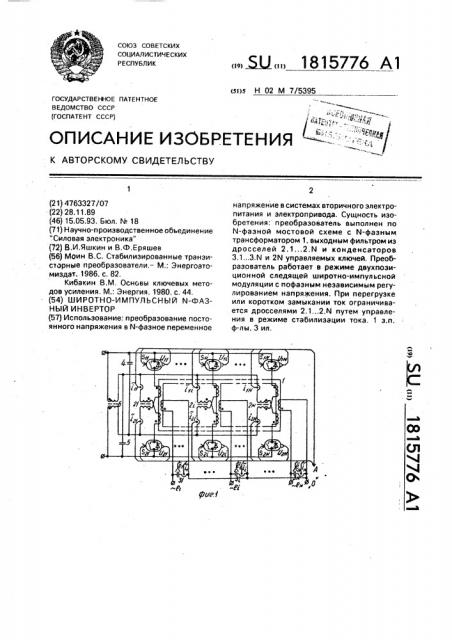

На фиг.1 изображена структурная схема широтно-импульсного N-фазного инвертора; на фиг.2 — структурная схема блока управления инвертором; на фиг.3 диаграммы работы одной фазы инвертора (i-й) в различных режимах.

Широтно-импульсный N-фазный инвертор (фиг,1) содержит N-фазный трансформатор 1 с двумя первичными и одной вторичной обмоткой в каждой i-той фазе, N пар управляемых ключей $11, ..., $гь $гь ..., SzN, каждый из которых шунтирован обратно включенным диодом, N двухобмоточных дросселей 2,1, ..., 2.N выходных фильтров, N конденсаторов 3.1, ..., 3,N выходных фильтров, подключенных параллельно вторичным обмоткам соответствующих фаз, соединенных N-фазной звездой, первые К управляемые ключи S>>, $1з, ..., $щ всех фаз подключены первыми силовыми выводами к первому входному выводу инвертора, а вторые N управляемые ключи $г1, $22, ..., S2N всех фаз подключены вторыми силовыми выводами к второму входному выводу инвертора. а цепочки из последовательно соединенных соответствующих первичных обмоток трансформатора 1 и обмоток дросселей 21, ... 2N выходных фильтров подключены одними концами к вторым силовым выводам соответствующих первых управляемых ключей $11, $и, ..., $щ и к первым силовым выводам соответствующих вторых управляемых ключей Szi, $22, ..., S2N, два входных конденсатора 4, 5, датчики мгновенных значений токов и напряжений 3ц, 721 ". l1N 12М. 11 ".А. ", IN 01k, 021, ..., U1l, 02ь ..., 01N, 02N е1 ...,. еь ..., 8N и блок управления БУ, при этом управляемые ключи $11, Szi, ..., $щ, S2N в каждой из N фаз переключаются противофазно, двухобмоточный входной дроссель 6, обмотки которого первыми выводами подключены соответственно к первому и второму входным выводам инвертора и к соответствующим выводам двух входных конденсаторов

4,5, а своими вторыми- к соответствующим другим выводам этих конденсаторов 4, 5 и

55 концам цепочек из последовательно соединенных соответствующих первичных обмоток трансформатора 1 и обмоток дросселей

21,;... 2N выходных фильтров, а блок управления БУ (фиг.2) выполнен из N идентичных блоков В1, ..., BN, каждый из которых содержит первый, второй суммирующие усилители 1, 2 ° двойной интегратор 3 с устройством обнуления, задатчик управляющего сигнала по напряжению 4 с соответствующим фазовым сдвигом, нуль-орган 5, первый компаратор 6 со стробированием, первые инвертор

7, одновибратор 8 с запуском по переднему фронту и элемент И вЂ” НЕ 9. вторые одновибратор 10 с запуском по переднему фронту и элемент И вЂ” НЕ 11, элемент ИЛИ 12, второй инвертор I3 и третий, четвертый элементы

И-НЕ 14, 15, третий суммирующий усилитель 16, второй компаратор 17 с симметричным гистерезисом и стробированием, прецизионный двухполупериодный выпрямитель 18, третьи компаратор 19 и инвертор

20, пятый, шестой элементы И вЂ” НЕ 21, 22, задатчик постоянного управляющего сигнала по току 23, аналоговый инвертор 24, двухвходовый аналоговый управляемый ключ 25, четвертый инвертор 26. третий. четвертый одновибраторы 27,.28 с запусками по передним фронтам, элемент ИЛИ-НЕ 29, первый, второй формирователи 30, 31 импульсов управления ключами $иь $э соответствующей i-той фазы преобразователя, причем, соответственно в каждом из N блоков В1, ..., BN, неинвертирующий вход первого усилителя 1 соединен с выходом датчика напряжения 0а первого управляемого ключа $ц соответствующей i-той фазы, а инвертирующий вход — с выходом датчика напряжения Uzi второго управляемого ключа Szi этой фазы, выход первого усилителя 1 соединен с первым инвертирующим входом второго усилителя 2 и с входом двойного интегратора 3, второй неинвертирующий вход второго усилителя 2 соединен с выходом датчика мгновенных значений напряжения ei конденсатора 31 выходного фильтра соответствующей i-той фазы, третий неинвертирующий вход второго усилителя 2 соединен с выходом датчика мгновенного значения тока li этого конденсатора 3i, четвертый инвертирующий вход второго усилителя 2 соединен с выходом задатчика 4 управляющего синусоидального сигнала по напряжению с соответствующим фазовым сдвигом и с входом нуль-органа 5, выход второго усилителя 2 соединен с первым входом первого компаратора 6, а его второй вход — с выходом двойного интегратора 3, выход первого компаратора 6 соединен с входами первых ин1815776 тегратора 7, одновибратора 3 и с первым входом первого элемента И вЂ” НЕ 9, выход первого инвертора 7 соединен с входом второго одновибратора 10 и с первым входом второго элемента И вЂ” НЕ 11, выходы первого, второго одновибраторов 8, 10 соединены соответственно с первым, вторым входами элемента ИЛИ 12, à его выход — с входом второго инвертора 13 и с управляющим входом устройства обнуления двойного интегратора 3, выход второго инвертора 13 соединен с третьими входами первого, второго элементов И вЂ” НЕ 9, 11, а выходы этих элементов соединены соответственно с вторыми входами третьего, четвертого элементов И вЂ” НЕ 14, 15, первый вход третьего усилителя 16 соединен с выходом датчика мгновенного значения тока ц одной обмотки дросселя 2i выходного фильтра соответствующей i-той фазы, а второй вход этого усилителя 16 — с выходом датчика мгновенГ; ного значения тока щ другой обмотки этого дросселя 2i, выход третьего усилителя 16 соединен с неинвертирующим входом второго компаратора 17 и с входом двухполупериодного выпрямителя 18, а его выход — с

° неинвертирующим входом третьего компаратора 19, выход этого компаратора 19 соединен с входом третьего инвертора 20, со стробирующим входом STR второго компаратора 17, с третьими входами пятого, шестого элементов И вЂ” НЕ 21, 22 и с третьим входом элемента ИЛИ 12, выход третьего инвертора 20 соединен со стробирующим входом STR первого компаратора 6 и с вторыми входами первого. второго элементов

И вЂ” НЕ 9, 11, выход задатчика постоянного управляющего сигнала по току 23 соединен с инвертирующим входом третьего компаратора 19, с входом аналогового инвертора

24 и с первым входом двухвходового аналогового управляемого ключа 25, выход аналогового инвертора 24 соединен с вторым входом двухвходового аналогового управляемого ключа 25, а его выход — с инвертирующим входом второго компаратора 17, выход нуль-органа 5 соединен с управляющим входом двухвходовового аналогового ключа 25, выход второго компаратора 17 соединен с входом четвертого инвертора 26, с первым входом пятого элемента И вЂ” НЕ 21 и с входом третьего одновибратора 27, выход четвертого инвертора 26 соединен с входом четвертого одновибратора 28 и с первым входом шестого элемента И-НЕ 22, выходы третьего, четвертого одновибраторов 27, 28 соединены с первым, вторым входами элемента ИЛИ-HE 29, а его выход — с вторыми входами пятого, шестого эленость) импульсов в функции некоторой низкочастотной модулирующей (модулиру55 ющая частота Q), при этом должно выполняться условие, чтобы пауза г была значительно меньше по времени как периода несущей, так и периоде модулирующей, т.е.

50 ментов И вЂ” НЕ 21, 22, выход пятого элемента

И-НЕ 21 соединен с первым входом третьего элемента И-НЕ 14, а выход шестого эелмента И вЂ” НЕ 22 — с первым входом четвертого элемента И вЂ” НЕ 15, выход третьего элемента И вЂ” НЕ 14 соединен с входом первого формирователя 30 импульсов управления, выход четвертого элемента И вЂ” НЕ

15 соединен с входом второго формирователя 31 импульсов управления, выход первого формирователя 30 подключен ко входу управления первого управляемого ключа Зц соответствующей i-той фазы, а выход второго формирователя 31 — ко входу управления второго управляемого ключа Szi этой фазы, при этом, в каждом из N блоков В>, ..., Ви, задатчик 4 управляющего синусоидального сигнала по напряжению обеспечивает величину фазового сдвига рч + 2 л = 2 (i — 1)/1, по соответствующей фазности выходного напряжения, а i = 1, 2, 3, ..., N — порядок соответствующей фазности преобразователя.

Широтно-импульсный N-фазный инвертор работает следующим образом.

В каждой фазе N-фазного инвертора пары управляемых ключей, выполненных, например, на транзисторах, переключаются поочередно, т.е. противофазно, через малую паузу т, необходимую для исключения сквозного тока через них вследствие конечного времени выключения. При пофазном регулировании работа всех фаз протекает независимо друг от друга и в общем случае идентично, с той лишь разницей; что в каждой фазе формируется сдвинутое на фиксированную величину, определяемую фазностью преобразования, выходное синусоидальное напряжение, в совокупности образующее связанную N-фазную систему, Поэтому для определенности, в дальнейшем будем рассматривать некоторую 1-ю фазу, причем переменная i может принимать только целые значения, т.е. i = 1, 2, 3, ..., N.

Формирование или синтез выходного напряжения в каждой фазе осуществляется в режиме двухпозиционной следящей широтно-импульсной модуляции, частота повторения импульсов которой (несущая частота ю) почти неизменна, а изменяется лишь относительная длительность (скваж1815776

2 л/й > 2 жЪ» т = const

Каждая фаза инвертора снабжена сравнительно низкочастотным выходным фильтром, образованным, например в i-й фазе, линейным дросселем 2! и конденсатором 3i.

Собственная частота резонанса этого фильтра близка к частоте несущей и, благодаря чему обеспечивается выделение основной гармоники напряжения с модулирующей частотой И и питание нагрузки этой фазы синусоидальным выходным напряжением с заданным качеством.

При противофаэном включении первого, второго управляемых ключей $1ь Szi напряжение с первого 4, второго 5 конденсаторов (емкостных накопителей), предварительно заряженных от постоянного источника питания через обмотки магнитносвязанного входного дросселя 6, прикладывается попеременно то к одним, то к другим обмоткам дросселя 2! и первичным обмоткам i-й фазы трансформатора 1, возбуждая в их магнитных системах мрдулированные по синусоидальному закону знакопеременные фазные магнитные потоки, осуществляющие формирование в дросселе

2l низкочастотную гладкую составляющую тока фильтра, а в трансформаторе 1 — индуцирование во вторичную обмотку перемен ного напряжения, иэ которого с помощью конденсатора 3i выделяется низкочастотная гладкая составляющая напряжения, поступающая затем в фаэную нагрузку.

Благодаря разделению обмоток входного дросселя 6 и подключению каждой из них к своему конденсатору 4 и 5, возможно обеспечить питание каждого управляемого ключа $11, $2i оТ независимого емкостного накопителя. Зто позволяет плавно ограничивать амплитуды зарядных токов этих конденсаторов 4, 5 в моменты пуска и перегрузок с одновременным симметрированием напряжения на них. Разделение первичных обмоток трансформатора 1, обмоток дросселей 21, ..., 2N и подключение каждых из них со своим управляемым ключом к отдельному емкостному накопителю, позволяет в каждый полупериод несущей через свой открытый ключ ($ц либо Szi) запитывать их от отдельного источника напряжения и тем самым уменьшить в два раза частоту пульсирующей составляющей каждого из конденсаторов 4, 5, а также осуществить самобалансирующую рекуперацию энергии, накопленной в моменты коммутации управляемых ключей в индуктивностях рассеяния дросселей 21, ... 2N и N-фазного

10

N-фазного трансформатора 1 зарядных то15 ков конденсаторов 4 и 5, а следовательно и возможность замагничивания и насыщения

50 трансформатора 1, в отдельные конденсаторы 4, 5 через соответствующие обратные диоды, тем самым исключая коммутационные перенапряжения, При активно-реактивных или нелинейных фазных нагрузках через соответствующие обратные диоды обеспечивается также возврат части фазных токов нагрузок в емкостные накопители 4и5, Независимое подключение управляемых ключей фазы инвертора исключает протекание через соответствующие обмотки дросселей 21, ..., 2N и первичные обмотки его магнитной системы в моменты пуска и перегрузок. Кроме того, первые же такты работы любой иэ фаз происходят с номинальным напряжения питания. обеспечивая тем самым начало синтеза кривой соответствующего выходного синусоидального напряжения с минимальным отклонением от уставки задания, что уменьшает время переходного процесса установления системы Nфаэного напряжения в нагрузке. В результате повышается надежность работы

N-фазного трансформатора и всего широтно-импульсного Й-фазного инвертора.

Фазная нагрузка к выходу инвертора может подключаться как система N-фаэной звезды с нулем, так и N-фазного треугольника или их комбинация. Для уменьшения индуктивностей рассеяния N-фазного трансформатора 1 первичные обмотки в каждой его фазе должны быть намотаны на соответствующем стержне синфазно и с

"тесной" электромагнитной связью.

Как уже отмечалось, структура силовой цепи инвертора позволяет при асимметрии фаз нагрузки осуществить пофазное независимое регулирование и стабилизацию выходных напряжений, а при перегрузке или коротком замыкании — активную стабилизацию фаэных токов на заданном уровне, т.е. ограничение токов через соответствующие фазные управляемые ключи путем изменения интервалов проводящего состояния в функции соответствующего мгновенного тока.

Для регулирования и стабилизации с эаданной точностью и качеством синусоидального выходного напряжения в инверторе используется блок управления БУ, состоящий из N идентичных блоков В1, ..., Bg (фиг.2), каждый из которых в зависимости от состояния и действия возмущающих факторов осуществляет слежение эа текущими в соответствующей фазе мгновенными значениями токов и напряжений и осуществляет

1815776

10 необходимое управление соответствующими ключами этой фазы. Поэтому, для определенности, в дальнейшем будем рассматривать работу некоторого i-того блока Bi, причем i = 1, 2, 3,, „N, осуществляющего в номинальном режиме управления i-той фазы преобразователя по способу вычисляемого условного прогноза.

Эвристический принцип условного прогноза основан нэ том, что непрерывно на каждом межкоммутационном интервале соответствующей фазы вычисляется некоторое прогнозируемое значение рассогласования выходного параметра, в данном случае фазного напряжения, и формируются импульсы управления ключами фазы в моменты времени, соответствующие необходимым моментам переключения по прогноэируемому минимальному значению рассогласования, т,е, вычисленная длительность межкоммутационного интервала определяет необходимую вариацию скважности на- периоде несущей. Произвольное возмущение по входу либо по выходу инвертора изменяет моменты переключения управляемых ключей соответствующей фазы или скважность несущей таким образом, что переходной и новый установившийся режимы отличаются от задающего воздействия на величину, не превышающую заданную точность. В результате осуществляется практически мгновенное слежение за синусоидальным сигналом задания. Время задержки отработки по возмущению равно апертурному времени вычисления условного прогноза, т.е. такту несущей.

При перегрузке инвертора или фазном коротком замыкании, блок Bi перестраивает свою структуру. осуществляя практически мгновенное слежение не за выходным параметром (фазным напряжением), à зэ токами обмоток дросселя 2i и тем самым, за токами управляемых ключей Яц, Я2, поддерживая их на некотором заданном уровне, не превышающем предельно допустимый, т.е, осуществляет их активную стабилизацию.

Элементы блока В1, вычисляющие условный прогноз рассогласования, в это время выключаются и устанавливаются в исходное состояние. После окончания действия токового возмущения, элементы блока В, осуществляющие стабилизацию тока, мгновенно выключаются и устанавливаются в исходное состояние, затем разрешается работа элементов контура вычисления условного прогноза, Таким образом, происходит обратная перестройка структуры блока

Bi и продолжается отслеживание выходного параметра.

Рассмотрим более подробно работу блока Bi в режиме стабилизации выходного фазного напряжения.

Информационные сигналы с датчиков напряжения 01ь U2i или состояния управляемых ключей S11, S2I (фиг.1, 2) I-той фазы с соответствующими коэффициентами усиления поступают на входы первого суммирующего усилителя 1, на выходе которого формируется знакопеременная коммутационная функция Оь соответствующая величине напряжения источника питания и текущему состоянию управляемых ключей

Я1ь S2t, С датчиков мгновенных значений напряжения е и тока ii фазного конденсатора 3i i-й фазы, с соответствующими коэффициентами усиления информационные сигналы обратной связи по напряжению и по скорости его изменения (производная сигнала обратной связи или ток конденсатора 3i). поступают соответственно на второй, третий неинвертирующие входы второго суммирующего усилителя 2. На первый инвертирующий вход этого усилителя 2 с соответствующим коэффициентом усиления, поступает коммутационная функция Ul c выхода первого усилителя 1, а на четвертый инвертирующий вход усилителя 2 — сигнал задания с задатчика 4. В результате на выходе усилителя 2 формируется энакопеременный разностный сигнал управления, поступающий затем на первый вход первого компаратора со стробированием 6, при этом в номинальном режиме нэ его стробирующий вход STR подается разрешающий сигнал логической единицы с выхода третьего инвертора 20.

С выхода первого усилителя 1 сигнал, т.е, коммутационная функция -Ui поступает на вход двойного интегратора 3 с устройством обнуления, отсчитывающего некоторое локальное время вычисления прогноза и формирующего в течение него аппроксимацию второго порядка этой функции в виде изменяющейся параболической развертки, поступающую затем на второй вход первого компаратора 6. В результате сравнения сигналов компаратором 6, при достижении их разности нулю, происходит

его переключение в новое состояние, либо логической единицы, либо логического нуля, т.е. вырабатываются команды на переключение соответствующих управляемых ключей Яи, $21 и формирование по возбуждающим передним фронтам одновибраторами 8 или 10 кратковременной паузы т, эа время которой происходит обнуление двойного интегратора 3 и установка его в исходное состояние сигналом

1815776

12 сброса, поступающим с выхода объединяющего сигналы одновибраторов 8, 10 логического элемента ИЛИ 12 на логический S вход интегратора 3. Импульс r затем инвертируется логическим инвертором 13 и одновременно поступает на первые входы первого, второго элементов И вЂ” НЕ 9, 11. На вторые входы этих элементов И-HE 9, 11 поступают соответственно прямая и инверсная (образованная с помощью первого ин- 10 вертора 7) команды переключения, генерируемые компаратором 6. На третьи входы элементов 9, 11 одновременно поступает сигнал с выхода третьего инвертора 20, осуществляющего запрет на работу контура 15 вычисления прогноза при переходе в режим стабилизации тока.

С выходов элементов И-НЕ 9, 11 команды переключения поступают на соответствующие первые входы третьего, четвертого 20 элементов И-НЕ 14, 15, а с их выходов — на входы формирователей 30, 31 импульсов уп-равления. Затем формирователь 30 управляет первым ключом Яц i-й фазы, а формирователь 31 — ключом Sz этой фазы. 25

Рассмотрим работу блока В в режиме . стабилизации тока.

Информационные сигналы с датчиков мгновенных значений токов Ь, @ обмоток дросселя 2i (фиг.1, 2) i-той фазы, с соответ- 30 ствующим коэффициентом усиления посту.пают на входы третьего суммирующего усилителя 16, на выходе которого формируется сигнал ii, пропорциональный току управляемых ключей этой фазы и 35 изменяющийся по квазисинусоидальному закону с некоторым фазовым сдвигом, обусловленным характером комплекса фазной нагрузки. С выхода усилителя 16 сигнал поступает на вход прецизионного двухполупе- 40 риодного выпрямителя 18 и на неинвертирующий вход второго компаратора II7 с симметричным гистерезисом и стробированием. Для синфазного с управляющим воздействием по напряже- 45 нию переключения уставок ограничения по току управляемых ключей используется сигнал, поступающий с выхода задатчика 4 на вход нуль-органа 5, а затем, с его выхода— на управляющий вход двухвходового анало- 50 гового управляемого ключа 25. Уставка по току +li поступает на первый вход ключа 25, а ее инверсия -ii через аналоговый инвертор

24 — на второй вход ключа 25. Таким образом, синфаэно с управляющим воздействи- 55 ем, на инвертирующий вход компаратора 17 поступает энакопеременная уставка задания по току с задатчика 23, что обеспечивает постоянство частот пульсирующих магнитных потоков в стержнях магнитной системы

N-фазного трансформатора 1 и соответственно, симметрию системы выходного Nфаэного напряжения. Кроме того, постоянное напряжение смещения с выхода задатчика 23 поступает также на инвертирующий вход третьего компаратора 19, а на

его неинвертирующий вход — пульсирующий сигнал модуля тока с выхода выпрямителя 18. Если сигнал модуля тока превысит напряжение смещения, т.е. уставку по току задатчика 23, то на выходе третьего компаратора 19 появляется сигнал (логическая единица), запрещающий работу контура вычисления условного прогноза и разрешающий работу контура стабилизации тока, Сигнал с выхода компаратора 19 одновременно поступает на вход третьего инвертора 20, на стробирующий вход STR второго компаратора 17, разрешающий его работу, на первые входы пятого, шестого элементов

И-НЕ 21, 22 и на третий вход элемента ИЛИ

12, формируя на его выходе сигнал запрета работы двойного интегратора 3 (зануляя его).

В результате второй компаратор 17 совместно с четвертым инвертором 26 генерирует противотактные команды переключения. Их частота и соответствующая ей амплитуда пульсирующей составляющей стабилизируемого тока ii зависит от энергоемкости дросселя 3i и однозначно определяется шириной зоны симметричного гистерезиса второго компаратора 17. Команды переключения с выхода компаратора

17 поступают на третий вход элемента ИНЕ 21 и на вход возбуждаемого передним фронтом третьего одновибратора 27, а команды с выхода инвертора 26 поступают на третий вход элемента И вЂ” НЕ 22 и на вход возбуждаемого передним фронтом четвертого одновибратора 28. Одновибраторы 27, 28 генерируют, соответственно каждый, кратковременный импульс r, равный времени необходимой паузы для надежного выключения управляемых ключей S>i, Szi во время работы. Затем сигналы с выходов одновибраторов 27, 28 объединяются логическим элементом ИЛИ-HE 29 и с его выхода поступают на вторые выходы элементов ИНЕ 21, 22. В результате сигналы, сформированные на выходах этих элементов И вЂ” НЕ 21, 22 поступают на вторые входы элементов

И-НЕ 14, 15, а с них — на соответствующие формирователи 30, 31 импульсов управления.

При выходе инвертора из режима перегрузки или фазного короткого замыкания, сигнал по току с выхода выпрямителя 18 становится меньше напряжения уставки с задатчика 23 и третий компаратор 19 пере13

1815776

14 ключается в другое состояние. вырабатывая сигнал (логический нуль), запрещающий работу второго компаратора 17 с гистерезисом и разрешающий работу контура вычисления условного прогноза. т.е. практически мгновенно начинается режим отслеживания выходного параметра соответствующей i-той фазы. а в общем случае и номинальный режим работы всего инвертора.

Формула изобретения

1, Широтно-импульсный N-фазный инвертор, содержащий N-фазный трансформатор с двумя первичными и одной вторичной обмотками в каждой фазе, N nap управляемых ключей, каждый из которых шунтирован обратно включенным диодом, N двухобмоточных дросселей выходных фильтров, N конденсаторов выходных фильтров, подключенных параллельно вторичным обмоткам соответствующих фаз, соединенных N-фазной звездой, первые N управляемых ключей всех фаз подключены первыми силовыми выводами к первому входному выводу инвертора, а вторые N управляемых ключей всех фаз подключены вторыми силовыми выводами к второму входному выводу инвертора, цепочки из последовательно соединенных соответствующих первичных обмоток трансформатора и обмоток дросселей выходных фильтров подключены одними концами к вторым силовым выводам соответствующих первых управляемых ключей и к первым силовым выводам соответствующих вторых управляемых ключей, два входных конденсатора, датчики мгновенных значений токов и напряжений и блок управления, при этом управляемые ключи в каждой из N фаз переключаются противофазно, о т л и ч а юшийся тем, что, с целью повышения надежности путем ограничения пусковых зарядных токов, введен двухобмоточный входной дроссель, обмотки которого первыми выводами подключены соответственно к первому и второму входным выводам инвертора и к соответствующим выводам двух входных конденсаторов, а своими вторыми выводами — к сОответствующим другим выводам этих конденсаторов и к концам цепо-. чек из последовательно соединенных соответствующих первичных обмоток трансформатора и обмоток дросселей выходных фильтров, 2. Инвертор по п.1. отличающийся тем, что, с целью получения синусоидальной формы выходного напряжения, его широтно-импульсного пофазного регулирования и ограничения токов через управляемые ключи при перегрузке и коротком замыкании.

55 блок управления выполнен из N идентичных блоков, каждый из которых содержит первый и второй суммирующие усилители, двойной интегратор с устройством обнуления, задатчик управляющего синусоидального сигнала по напряжению с соответствующим фазовым сигналом, нульорган, первый компаратор со стробированием, первые инвертор, одновибратор с запуском по переднему фронту и элемент

И вЂ” НЕ, вторые одновибратор с запуском по переднему фронту и элемент И вЂ” НЕ, элемент

ИЛИ, второй инвертор и третий, четвертый элемент И вЂ” НЕ, третий суммирующий усилитель, второй компаратор с симметричным гистерезисом и стробированием, прецизионный двухполупериодный выпрямитель, третий компаратор и инвертор, пятый, шестой элементы И-НЕ, задатчик постоянного управляющего сигнала по току, аналоговый инвертор, двухвходовый аналоговый управляемый ключ, четвертый инвертор, третий одновибратор с запусками по передним фронтам. элемент ИЛИ вЂ” НЕ, первый, второй формирователи импульсов управления ключами соответствующей фазы, причем в каждом из N блоков, неинвертирующий вход первого усилителя соединен с выходом датчика напряжения первого управляемого ключа соответствующей фазы, а инвертирующий вход- с выходом датчика напряжения второго управляемого ключа этой фазы, выход первого усилителя соединен с первым инвертирующим входом второго усилителя и с входом двойного интегратора с обнулением, второй неинвертирующий вход второго усилителя соединен с выходом датчика мгновенного значения напряжения конденсатора выходного фильтра соответствующей фазы, третий неинвертирующий вход второго усилителя соединен с выходом датчика мгновенного значения тока этого конденсатора, четвертый инвертирующий вход второго усилителя соединен с выходом задатчика управляющего синусоидального сигнала по напряжению с соответствующим фазовым сдвигом и с входом нуль-органа, выход второго усилителя соединен с первыу входом первого компаратора, а его второй вход — с выходом двойного интегратора, выход первого компаратора соединен с входами первых инвертора, одновибратора и первым входом первого элемента И вЂ” НЕ, выход первого. инвертора соединен с входом второго одновибратора и с первым входом второго элемента И вЂ” НЕ, выходы первого, второго одновибраторов соединены соответственно с первым. вторым входами элемента ИЛИ, а его выход — с входом второго инвертора и с управляющим входом устрой1815776

16 ства обнуления двойного интегратора, выход второго инвертора соединен с третьими входами первого, второго элементов И-НŠ— а выходы этих элементов соединены соответственно с вторыми входами третьего, 5 четвертого элементов И-НЕ, первый вход третьего усилителя соединен с выходом датчика мгновенного значения тока одной обмотки дросселя выходного фильтра соответствующей фазы, а второй вход этого 10 усилителя — с выходом датчика мгновенного значения тока другой обмотки этого дросселя, выход третьего усилителя соединен с неинвертирующим входом второго компаратора и с входом прецизионного двухполу- 15 периодного выпрямителя, а его выход — с неинвертирующим входом третьего компаратора, выход этого компаратора соединен с входом третьего инвертора, со стробирующим входом второго компаратора, с третьи- 20 ми входами пятого, шестого элементов

И-НЕ и с третьим входом элемента ИЛИ, выход третьего инвертора соединен со стробирующим входом первого компаратора и с вторыми входами первого, второго элемен- 25 тов И-HE. выход задатчика постоянного уггравляющего сигнала по току соединен с инвертирующими входом третьего компаратора, с входом аналогичного инвертора и с первым входом двухвходового аналогового 30 управляемого ключа, выход аналогового инвертора соединен с вторым входом двухвходового аналогового управляемого ключа, а его выход — с инвертирующим входом второго компаратора, выход нуль-органа соединен с управляющим входом двухвходового аналогового управляемого ключа, выход второго компаратора соединен с входом четвертого инвертора, с первым входом пятого элемента И-НЕ и с входом третьего одновибратора, выход четвертого инвертора соединен с входом четвертого одновибратора и с первым входом шестого элемента И вЂ” НЕ, выходы третьего, четвертого одновибраторов соединены соответственно с первым, вторым входами элемента ИЛИ вЂ” НЕ, а его выход — с вторыми входами пятого, шестого элементов И-НЕ, выход пятого элемента И-НЕ соединен с первым входом третьего элемента И вЂ” НЕ, а выход шестого элемента И-НŠ— с первым входом четвертого элемента И вЂ” НЕ, выход третьего элемента И-НЕ соединен с входом первого формирователя импульсов управления; выход четвертого элемента И-НЕ соединен с входом второго формирователя импульсов управления, выход первого формирователя подключен к входу управления первого управляемого ключа соответствующей фазы, а выход второго формирователя— к входу управления второго управляемого ключа этой фазы, при этом в каждом из блоков задатчик управляющего синусоидального сигнала по напряжению обеспечивает величину фазового сдвига по соответствующей фазнос ти выходного напряжения.

1815776

1815776

Составитель В.Яшкин

Техред М.Моргентал

Редактор

Корректор Л,Пилипенко роизводственно-издательский комбинат "Патент". г. Ужгород, ул.Гагарина.

Заказ .16ФЗ Тираж Подписное

ВНИИПИ Г

И И Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж 35, Раушская наб., 4/5