Двухполярный стабилизатор постоянного напряжения

Иллюстрации

Показать всеРеферат

Область использования: в источниках вторичного электропитания радиоэлектронной аппаратуры. Сущность изобретения: устр-во содержит восемь транзисторов, два регулирующих транзистора, делитель напряжения с двумя выходами и повторитель тока. Схема выполнена таким образом, что температурный дрейф опорного напряжения значительно снижен. 1 ил.

союз соВетских

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГоспАгент сссР) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Ф

° »

I»

° »

Ъ Ф (21) 4935953/07 (22) 14,05,91 (46) 23,05.93. Бюл. hb 19 (71) Шахтинский технологический институт бытового обслуживания (72) А.Э.Попов, Ю,М.Соколов, Н.И.Ясюкевич, В,Г,Манжула, А.Б,Исаков и Е.И,Старченко (56) 1. ДАТА ВООК voi. 19, 1978, р.276, Fig, F139, 2. ДАТА ВООК ЕД-18, 1984, р.242, Fig.

F139.

Изобретение относится к области электротехники и может быть использовано в источниках вторичного электропитания радиоэлектронной аппаратуры.

Цель изобретения — повышение темпе. ратурной стабильности и расширение диапазона выходных напряжений стабилизатора.

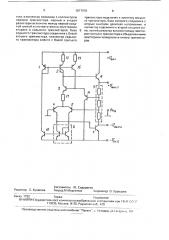

На чертеже приведена принципиальная электрическая схема устройства.

Устройство содержит транзисторы 1-5, регулирующие элементы 6 и 7, повторитель тока 8, причем эмиттер транзистора 1 объединен с коллектором регулирующего элемента 6 и подключен к первой входной шине, база транзистора 1 объединена с его коллектором и соединена с базой транзистора 2, коллектор которого объединен с коллектором транзистора 3 и подключен к базе регулирующего элемента 6, змиттер которого соединен с первым выходом, эмиттеры транзисторов 4 и 5 объединены, база транзистора 4 соединена с. общей шиной, его коллектор объединен с базой регулиру„„Ы2 ÄÄ 1817079 А1 (54) ДВУХПОЛЯРНЫЙ СТАБИЛИЗАТОР

ПОСТОЯННОГО НАПРЯЖЕНИЯ (57) Область использования; в источниках вторичного электропитания радиоэлектронной аппаратуры. Сущность изобретения: устр-во содержит восемь транзисторов, два регулирующих транзистора, делитель напряжения с двумя выходами и повторитель тока, Схема выполнена таким образом, что температурный дрейф опорного напряжения значительно снижен. 1 ил. ющего элемента 7 и подключен к выходу повторителя тока 8, вход которого соединен с коллектором транзистора 5, а вывод питания объединен с эмиттером регулирующего элемента 7 и подключен ко второй входной шине, база транзистора 5 связана с первым выходом делителя напряжения 9, вклоченного между первым и вторым выходами, коллектор регулирующего элемента 7 подключен ко второму выходу, транзистор 10, резисторы 11 — 13, транзисторы 14 и 15, причем эмиттер транзистора 10 подключен ко второй входной шине, база связана со входом повторителя тока, а коллектор соединен с коллектором транзистора 1, резисторы 12 и 13 включены между первой входной шиной и, соответственно, эмиттерами транзисторов 2 и 15; база транзистора 15 соединена с базой транзистора 2, коллектор транзистора 15 объединен с базой транзистора 3 и подключен к змиттеру транзистора

14, база которого связана со вторым выходом делителя напряжения 9, à его коллектор подключен ко второй входной шине, рези1817079 стор 11 включен между эмиттером транзистора 3 и объединенными эмиттерами транзисторов 4 и 5, Стабилизатор напряжений работает следующим образом, Предположим, что напряжение на первом выходе увеличилось. Это приращение передается на базы транзисторов 5 и 14, при этом ток коллектора транзистора 14 уменьшается,,большая часть коллекторного тока транзйстора 15 поступает в базу транзистора 3, который, открываясь, подзапирает регулирующий элемент 6, тем самым компенсируя первоначальное изменение напряжения на выходе.

В то же время нарушение баланса выходных напряжений приводит к уменьшению тока коллектора транзистора 5 и, соответственно, к увеличению тока коллектора транзистора 4. Приращение тока коллектора 4 поступает в базу регулирующего элемента 7, за счет чего увеличивается ток его коллектора, чем обеспечивается симметрия выходных напряжений, Опорное напряжение формируется между первым и вторым выходами делителя напряжения 9. Стабильность этого напряжения обеспечивается за счет компенсации отрицательного температурного дрейфа напряжения база — эмиттер транзистора 5 положительным температурным дрейфом напряжения на резисторе 11, Опорное напряжение можно представить как

Uon = 0бэ5+ UR11+ 0бэз 0бэ11 где 0ы — напряжение база-эмиттер соответствующего транзистора;

UR11 — падение напряжения на резисторе 11, При выполнении устройства методом интегральной технологии площади переходов транзисторов 2 и 15 можно сделать одинаковыми, Если пренебречь базовыми токами транзистора 3 и регулирующего элемента 6, то можно считать, что токи коллекторов транзисторов 3 и 14 будут равны.

Следовательно, напряжения база — эмиттер транзисторов 3 и 14 также равны. В этом случае выражение для опорного напряжения приобретает вид

Uon = 0бэ5+ 1к2Н11 (1)

ГдЕ Iк,2 = Л 0бэ/R12 — тОК КОЛЛЕКтара траНЭИстара 2;

Ri — сопротивление соответствующего резистора;

Л 0бэ = Рг In S1/S2 — Разность напРЯжений база-эмиттер транзисторов 1 и 2;

S — плогцадь эмиттера соответствующего транзистора;

55 рт — температурный потенциал.

Тогда выражение 1 можно представить следующим образом:

Uon = 0бэ5+ (PT In S1/S2)R11/R12 . (2)

Вполне очевидно, что второе слагаемое в выражении (2) имеет положительный темпеРатУРный ДРейф, а 0бэ5 отРиЦательный.

При соответствующем выборе сопротивлений резисторов 11 и 12 можно сделать температурный дрейф опорного напряжения нулевым. Это возможно, если Uon 1,205

В, что равно ширине запрещенной зоны для кремния.

Таким образом, поскольку температурная стабильность опорного напряжения в предлагаемом устройстве существенно выше, чем у прототипа, а минимальное выходное напряжение составляет 0,6...0,7 В, что существенно меньше, чем в схеме прототипа, поставленную цель можно. считать достигнутойй.

Формула изобретения

Двухполярный стабилизатор постоянного напряжения, содержащий пять транзисторов, два регулирующих транзистора, делитель напряжения с двумя выходами и повторитель тока, причем эмиттер первого транзистора вместе с коллектором первого регулирующего транзистора подключен к первой входной шине, база первого транзистора вместе с его коллектором соединена с базой второго транзистора, коллектор которого вместе с коллектором третьего транзистора подключен к базе первого регулирующего транзистора, эмиттер которого соединен с первой выходной шиной, однополярной с первой входной шиной, эмиттеры четвертого и пятого транзисторов объединены, база четвертого транзистора соединена с общей шиной, коллектор вместе с базой второго регулирующего транзистора подключен к выходу повторителя тока, вход которого соединен с коллектором пятого транзистора, а вывод питания вместе с эмиттером второго регулирующего транзистора подключен к второй входной шине, база пятого транзистора соединена с первым выходом делителя напряжения, включенного между первой и второй выходными разнополярными шинами, коллектор второго регулирующего транзистора соединен с второй выходной шиной, о т л и ч а ю щ и йс я тем, что, с целью уменьшения температурной нестабильности выходных напряжений и расширения их диапазона, введены шестой, седьмой и восьмой транзисторы и три резистора, причем эмиттер шестого транзистора подключен к второй входной шине, база соединена с входом повторителя

1017079

Составитель Ю. Сидоренко

Редактор С. Кулакова Техред M.Mîðãåíòàë . Корректор О. Кравцова

Заказ 1722 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гэгари-ia, 101 тока, э коллектор соединен с коллектором первого транзистора, первый и второй резисторы включены между первой входНоА свиной и соответственно змиттерами второго и седьмого транзисторов, база седьмого транзистора соединена с базой второго транзистора, коллектор седьмого транзистора вместе с базой третьего транзистора подключен к змиттеру восьмого транзистора, база которого соединена с вторым выходом делителя напряжения, а коллектор подключен к второй входной ши5 не, третий резистор включен между эмиттером третьего транзистора и объединен ными эмиттерами четвертого и пятого транзисторов.