Устройство обработки информации с переменной длиной команд

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и предназначено для выполнения инженерных, экономических и статистических расчетов. Целью изобретения является повышение быстродействия при выполнении Многооперандных операций с многоразрядными числами переменного формата. Для этого в устройство, содержащее блок 1 памяти команд, счетчик 2 адреса команд, регистр 3 инструкций, первый блок 4 микропрограммного управления, первый арифметико-логический блок 5, первый блок 6 оперативной памяти, счетчик 7 команд и таймер 8, введены буферный регистр 9, счетчик 10 операндов, счетчик 11 разрядов, второй блок 12 оперативной памяти , регистр 13 формата, К регистров 14 операндов, второй блок 15 микропрограммного управления, второй арифметико-логический блок 16, регистр 17 результата и регистр 18 адреса. Введенные блоки позволяют выполнять сложную обработку адресов разрядов разноформатных операндов первого блока 6 оперативной памяти в ходе выполнения инструкции устройством, Форматы данных хранятся во втором блоке 12 оперативной памяти, адресные входы которого соединены с группой выходов регистра 3 инструкций, а информационные входывыходы блока 12 соединены с соответствующими входами-выходами буферного регистра 9. Счетчик 10 операндов и счетчик 11 разрядов обеспечивают синхронизацию всех блоков устройства. 5 ил. (Л С оо vj о JO О

СОЮЗ СОВЕ ГСКИХ

col (иАлистиче ских

РЕСПУБЛИК

Гзоз G 06 F 15/00

ГОСУДАРСТВЕННОГ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПА ГЕНТ СССР) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

i Ч

iO

i К ) 1 (21) 4794287/24 (22) 19,02,90 (46) 23.05.93. Бюл. № 19 (71) Киевский научно-исследовательский институтмикроприборов (72) Н.Т.Голец, В.П.Захаров, Ю.М.Польский и П.В,Сивобород (56) Патент США ¹ 4491910, кл. G 06 F 9/22, 13/00, 1985, IC MASTER 1989 Hearst Buisness

Communications пс„р. 2488 — 91, (54) УСТРОЙСТВО ОБРАБОТКИ ИНФОРМАЦИИ C ПЕРЕМЕННОЙ ДЛИНОЙ КОМАНД (57) Изобретение относится к вычислительной технике и предназначено для выполнения инженерных, зкономических и статистических расчетов. Целью изобретения является повышение быстродействия при выполнбйии многооперандных операций с многоразрядными числами переменного формата. Для этого в устройство, содержащее блок 1 памяти команд, счетчик

2 адреса команд, регистр 3 инструкций, перSU 1817099 А1 вый блок 4 микропрограммного управления, первый арифметика-логический блок 5, первый блок 6 оперативной памяти, счетчик 7 команд и таймер 8, введены буферный регистр 9, счетчик 10 операндов, счетчик 11 разрядов, второй блок 12 оперативной памяти, регистр 13 формата, К регистров 14 операндов, второй блок 15 микропрограммного управления, второй арифметико-логический блок 16, -регистр 17 результата и регистр 18 адреса. Введенные блоки позволяют выполнять сложную обработку адресов разрядов разноформатных операндов первого блока 6 оперативной памяти в ходе выполнения инструкции устройством, Форматы данных хранятся во втором блоке 12 оперативной памяти, адресные входы которого соединены с группой выходов регистра

3 инструкций, а информационные входы— выходы блока 12 соединены с соответствующими входами-выходами буферного регистра 9. Счетчик 10 операндов и счетчик

11 разрядов обеспечивают синхронизацию всех блоков устройства. 5 ил.

1817099

Изобретение относится к вычислительной технике.

Цель изобретения — повышение быстродействия при выполнении многооперандных операций с многоразрядными числами переменного формата.

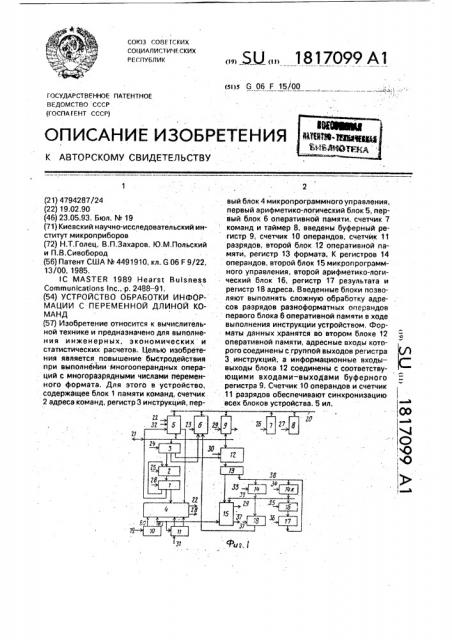

На фиг.1 приведена структурная схема устройства обработки информации с.переменной длиной команд; на фиг.2 — пример формата инструкции устройства; на фиг,3— пример формата данных устройства; на фиг.4 — временная диаграмма работы синхронизатора; на фиг.5 — пример протокола работы устройства с указанием микроприказов и содержимого регистров при выполнении двухоперандной инструкции,Устройство обработки информации с переменной длиной команд содержит блок

1 памяти команд, счетчик 2 адреса команд, регистр 3 инструкций, первый блок 4 микропрограммного управления, первый арифметико-логический блок 5, первый блок 6 оперативной памяти, счетчик 7 команд, таймер 8, буферный регистр 9, счетчик 10 операндов, счетчик 11 разрядов, второй блок 12 оперативной памяти, регистр 13 формата, регистры 14> — 14к операндов, второй блок

15 микропрограммного управления, второй арифметико-логический блок 16, регистр 17 результата и регистр 18 адреса.

Приняты следующие обозначения: 19— вход синхронизации устройства; 20 — информационная магистраль; 21 — управляющая магистраль; 22 — 28 — выходы первого блока микропрограммного управления; 29—

37 — выходы второго блока микропрограммного управления; 38; 39 — схемы

МОНТАЖНОЕ ИЛИ; Bo — В1 — внутренние и выходные сигналы счетчика операндов;

Со-Ci — внутренние и выходные сигналы счетчика разрядов; ЗЗ(14- 39) означает (в таблице на фиг,5), что микроприказ из группы 33 выходов второго блока микропрограммного управления осуществляет чтение информации из регистра 14 операндов в схему 39 МОНТАЖНОЕ ИЛИ.

Введенное устройство способно осуществлять сложную обработку последовательностей адресов синхронно с потоком поступающей информации. При последовательно-параллельном. способе представления информации это могут быть адреса отдельных 8-, 2 — 10-, 16-ричных разрядов чисел, адреса отдельных байтов или адреса слов другой разрядности. B общем случае количество разрядов (байтов, слов другой разрядности). обрабатываемых в каждой инструкции устройства, может быть равно

1 . от 1 до 2 = m и ограничивается только числом разрядов а регистров операндов, Сийхронизация узлов устройства осу ществляется сигналами, вырабатываемыми на выходах счетчика 10 операндов и счетчика 11 разрядов, Число внутренних состояний счетчика 10 операндов (коэффициент деления К1) должно обеспечивать прохождение одного разряда данных на АЛУ, обработку этих данных и запись результатов обработки, Так, например, для обработки двухоперандных команд коэффициент деления может быть равен 3 и определяться как . вызов на АЛУ первого операнда, второго операнда и собственно обработка информации с записью результата по адресу одного из операндов, Число внутренних состояний счетчика 11 разрядов (коэффициент деления

К2) является числом переменным и макси20 мально равно числу возможных разрядов операндов, обрабатываемых в одной инструкции ЭВМ, Минимально возможный временной интервал ЭВМ равен продол>кительности нахождения счетчика

10 операндов в одном состоянии. Общее время обработки К2 разрядов определяется как К1К2, Коэффициент деления К2 обеспечивается подачей сигнала 31 с второго блока микропрограммного управления на установочные входы счетчика 11 разрядов..Так как выходные сигналы делителей определяют моменты выработки сигналов устройствами управления, то моменты времени могут быть соотнесены с совокупностью состоя35 ний делителей, Блок 6 оперативной памяти представляет собой устройство с произвольной выборкой, в котором каждому со. стоянию адреСных входов соответствует выбор одного конкретного разряда из одно40 ro конкретного регистра данных. Выбор номера регистра определяется группой выходов из регистра 3 инструкций, выбор номера разряда — группой информационных выходов регистра 18 адреса. Последо45 вательность адресов разрядов и способ модификации операндов в ходе выполнения инструкции ойределяется введенным устройством и указывается в формате данных.

Синхронизация узлов устройства осуществляется сигналами с выходов одних и тех же делителей, что при общем равенстве периода циркуляции счетчика 11 разрядов (цикл) и последовательности адресов разрядов операндов дает возможность, с одной

55 стороны, однозначно определять в любой момент времени адреса разрядов операндов, а с другой стороны — привести в соответствие выходные сигналы синхронизатора и адреса разрядов операндов для выбранного формата данных. На1817099 пример, можно заранее установить, что при ройств в регистр 3 инструкций по управлявыполнении двухоперандной инструкции ющей магистрали 21, состоянию счетчика 10 операндов ВО соот- Результаты работы АЛУ 5 могут быть ветствует вызов на АЛУ первого операнда, выданы также на внешние устройства через

81 — второго, 82 — обработка операнд на 5 управляющую магистраль 21.

АЛУ и т.д„состоянию счетчика 11 разрядов Формирование адресов разрядов опеС0 соответствует К(0) разряд первого one- рандов осуществляется в течение каждого ранда и I (о) разряд второго операнда, С1 — цикла. Форматданных, аналогично формату значения адресов разрядов равны значени- инструкции, можно условно разбить на поям функции К(1) и l(1) соответственно и т.д„10 ля, в которых будут указаны начальные ада при достижении значения К(С), заранее реса разрядов ОЗУ, конечные адреса установленного в формате значения L адре- (адрес), код операции. Перед началом вы. са разрядов первого и второго операндов полнения каждой инструкции формат, адрес устанавливаются равными значениям функ- которого указан в инструкции устройства, ции K1(C) и 11(С) соответственно. При дости- 15 считывается из второго блока 12 оперативжении 11(C) = l либо при выработке - ной памяти в регистр 13 формата. Из регимикроприказапервымблоком4микропрог- стра 13 формата начальные адреса раммного управления по результатам рабо- разрядов ОЗУ через схему 38 МОНТАЖНОЕ ты первого блока АЛУ 5 может быть ИЛИ последовательно переписываются в завершен цикл выполнения инструкции и 20 регистры 14 — 14к операндов, Код операции переход счетчика 11 разрядов в исходное и конечный адрес поступают при этом во состояние СО. Совокупность состояний CiBJ второй блок 15 микропрограммного управсоответствует i-разряду j-операнда. ления. Начальные адреса разрядов послеПравило формирования адресов разря- довательно поступают иэ регистров 14 — 14к дов операндов указывается в поле формата 25 операндов через схему 39 МОНТАЖНОЕ данных и зависит от конкретного исполне- ИЛИ в блок 15 микропрограммного управния устройства. Формат, номер которого ления для сравнения с конечным адресом указывается в инструкции, перед началом или другими константами, на АЛУ 16 — для выполнения инструкции считывается с бло- вычисления следующего адреса разряда и в ка ОЗУ 12 в регистр 13 формата. В инструк- 30 регистр 18 адреса для управления ОЗУ 6, ции указываются также команды записи- При этом новое значение адреса разряда иэ нового формата или вызова старого форма- АЛУ 16 через регистр 17 результата и схему та для обработки, Обмен форматом в уст- 38 МОНТАЖНОЕ ИЛИ возвращается назад ройстве осуществляется через второй блок в регистр 14 соответствующего операнда.

12 оперативной памяти и буферный регистр 35 Сигналы с выходов блока 15 (группы 29 — 37

9. Информация в буферный регистр 9 может микроприказов) при этом осуществляют упбыть записана после обработки на АЛУ 5 равление всеми введеннымиузламиустройчерез информационную магистраль 20 или . ства и вырабатывают сигнал конца цикла, через управляющую магистраль 21 как часть Второй блок 15 микропрограммного управинструкции либо как второе слово инструк- 40. нения, помимо обработки адресов разрядов ции, операндов, может вырабатывать микроприказы 32, модифицирующие информацию неВ инструкции также указывается опера- посредственно — в первом ция, которая выполняется над операндами. арифметико-логйческом блоке 5.

Код операции из регистра 3 инструкций по- 45 . Рассмотрим работу устройства для слуступает в счетчик 2 адреса команд перед чаядвухоперанднойсистемыкомандспереначалом выполнения инструкции, По адре- менным форматом данных. Пусть . су, полученному на основе кода операции,. устройство находится в состоянии, когда завыбирается одна строка в блоке 1 памяти кончена обработка предыдущей инструкции команд. Часть выходов блока памяти ко- 50 и новая конструкция через управляющую манд используется для указания кода one- магистраль 21 записана в регистр 3 инструк.рации АЛУ 5, другая часть используется для ции, По сигналу об окончании цикла формат указания следующего адреса счетчик адре- данных из ОЗУ 12 за номером, указанным в са команд2(СЧАК), если операция занимает инструкции и установленным на его адреснесколько циклов, а третья часть, смешива- 55 ных входах, считывается в регистр 13 форясь в блоке 4 микропрограммного управле- мата. В следующем состоянии счетчика 10 ния с сигналами синхронизатора, операндов начальный адрес разряда первообеспечивает сигналы (микроприказы 22- ro операнда из регистра 13 через схему 38

28), управляющие работой всех узлов, Сама МОНТАЖНОЕ ИЛИ переписывается в реинструкция считывается из внешних уст- тистр 14 первого операнда. код операции

1817099

25

35

40 дет содержать полученное на АЛУ 16 45

50 из регистра 3 инструкции и переписывается в СЧАК 2, а код операции формата данных-из регистра 13 формата в блок 15 микропрограммного управления. Допустим; что формат, указанный в инструкции, обеспечивает обработку от второго до девятого разрядов второго операнда и циклически сдвинутого на три разряда вправо первого операнда. Запись результата обработки осуществляется по адресам второго операнда.

Момент времени СОВО соответствует началу цикла. По коду операции, содержащемуся в СЧАК 2, в блоке 1 памяти команд выбирается соответствующая строка, и первая группа выходов устанавливает код операции на входах АЛУ 5 для обеспечения соответствующей операции над данными, вторая группа выходов устанавливает адрес следующей команды на входах СЧАК 2, если инструкция занимает несколько циклов, или дополнение к коду адреса, если в следующем цикле будет приниматься новая инструкция. Третья группа выходов блока 1 памяти команд поступает в первый блок 4 микропрограммного управления. Блок 4 обеспечивает выборку на адресных входах

ОЗУ 6 адреса регистра первого операнда, При этом адрес пятого разряда первого oneранда обеспечивается на второй группе адресных входов ОЗУ 6 перезаписью содержимого регистра 14> первого îneðàíда в регистр 18 адреса. Одновременно содержимое регистра 141 через схему 39

МОНТАЖНОЕ ИЛИ поступает на вход АЛУ

16, а адрес второго разряда (второй операнд сдвинут на три разряда относительно первого) второго операнда из регистра 13 формата через схему 38 МОНТАЖНОЕ ИЛИ записывается в регистр 14 второго операнда. Таким образом, в конце момента времени СОВО на входах АЛУ 16 будет присутствовать номер пятого разряда первого операнда, а регистр 17 результата бузначение следующего номера разряда первого операнда (код 6), В следующий момент времени СОВ1 блок 15 вырабатывает микроприказ 23 выбора режима,- осуществляющие установки на первых адресных входах ОЗУ 6 адреса регистра второгО операнда, поступающего иэ регистра 3 инструкции, При этом содержимое регистра 142 второго операнда поступает через схему 39 МОНТАЖНОЕ ИЛИ на АЛУ 16 и в регистр 18 адреса, обеспечивая на вторых адресных входах ОЗУ 6 значение второго разряда, а содержимое регистра 17 результата (код 6) через схему

38 МОНТАЖНОЕ ИЛИ переписывается в ðe5

15 гистр 14 первого операнда, Аналогично в конце момента времени на АЛУ 16 будет получено значение следующего разряда второго операнда (код 3) и перезаписано в регистр 17 результата, В момент времени

СОВ2 значение адреса на входах ОЗУ 6 не меняется, блок 4 вырабатывает микроприказ группы 23 для записи результата работы

АЛУ 5 через информационную магистраль в первый блок 6 оперативной памяти, Одновременно содержимое регистра 17 результата (код 3) через схему 38 МОНТАЖНОЕ

ИЛИ заносится в регистр 14 второго операнда. Аналогично происходит обработка следующих 5,6...9-го и 2,3...6-го разрядов соответствующих операндов.

При обработке каждой пары разрядов, в моменты времени ВО, В1, осуществляется сравнейие содержимого схемы 39 МОНТАЖНОЕ ИЛИ со значением адреса конечного обрабатываемого разряда (код 9), поступающего иэ регистра .13 формата в блок 15. В момент времени С4ВО, в результате первого такого сравнения, вырабатывается микроприказ перегрузки содержимого регистра 27 формата, соответствующего начальйому адресу второго операнда (код 2)= в схему 38 МОНТАЖНОЕ ИЛИ и микроприказ группы 33 — записи содержимого схемы

3S МОНТАЖНОЕ ИЛИ в регистр 14> первого операнда. После обработки 2,3,4-го и 7,8,9го разрядов соответствующих операндов, в момент времени С7В1, наступает второе сравнение указанных величин. При этом блок 15 вырабатывает микроприказ 31 конца цикла (если он не был выработан ранее в блоке 4}, Если выполняемая инструкция была инструкцией ветвления, то по положительному результату анализа йризнаков, установленных в АЛУ 5 в ходе выполнения инСтрукции и поступающих в блок 4; будет выработан микроприказ 25 записи содержимого блока 1 памяти команд в СЧАК 2. В этом случае, прежде следующей инструкции, будет выполнена внутренняя команда устройства над содержимым счетчика команд 7. В противном случае будет выполняться следующая инструкция, считанная в регистр 3 инструкции по управляющей ма- гистрали. Очевидно, что содержимое счетчика команд 7 будет обрабатываться по сигналам блока 4 и независимо от содержимого формата данных. В конце момента времени С7В2 происходит установка счетчика

11 разрядов в исходное состояние СОВО, и вышеописанный процесс повторяется, Таким образом, устройство обработки информации с переменной длиной команд позволяет производить многооперандные операции над числами разной разрядности, 1817099 сдвинутыми одно относительно другого на любое число разрядов прямо или циклически, вправо или влево, с расширением старших разрядов, старших битов либо занулением, без промежуточных операций многократных пересылок. Переменные форматы обрабатываемых данных, многократное их использование позволяют быстро решать сложные задачи в малых объемах программной памяти, Формула изобретения

Устройство обработки информации с переменной длиной команд, содержащее блок памяти команд, счетчик адреса команд, регистр инструкций, первый блок многопрограммного управления, первый арифметико-логический блок, первый блок оперативной памяти, счетчик команд, таймер, буферный регистр, причем информационные входы — выходы первого арифметико-логического блока, первого блока оперативной памяти, буферного регистра, счетчика команд и таймера объединены через информационную магистраль и образуют первый вход — выход данных устройств, управляющий вход — выход первого 2 арифметико-логического блока и информационный вход регистра инструкций объединены через управляющую магистраль и образуют вход--выход инструкций устройст-. ва, первый выход регистра инструкций сое- 3 динен с первым информационным входом счетчика адреса команд, второй информационный вход счетчика адреса команд соединен с первым выходом блока памяти команд, второй и третий выходы которого 3 соединены соответственно с входом кода операции первого арифметико-логического блока и с информационным входом первого блока управления, информационный выход счетчика адреса команд соединен с адрес- 4 ным входом блока памяти команд, выходы с первого по седьмой первого блока управления соединены с первым входом микроприказов первого арифметико-логического блока, первым входом выбора режима блока 4 . оперативной памяти, с входом чтения-записи регистра инструкций, с управляющими входами счетчика адреса команд, счетчика команд, таймера, входом режима блока памяти команд, второй выход регистра инст- 5 рукций соединен с первым адресным входом первого блока оперативной памяти, выход результата первого арифметико-логического блока соединен с входом условий первого блока микропрограммного управ-. 5 ления, отлича ющееся тем,что,с целью повышения быстродействия при выполнении многооперандных операций с многоразрядными числами переменного формата, в устройство введены регистр временного хранения, второй блок оперативной памяти, регистр формата, К-per crpoe операндов, регистр результата, регистр адреса, второй блок микропрограммного уп5 равления, счетчик операндов, счетчик разрядов, второй арифметико-логический блок, причем информационный выход счетчика операндов соединен с входом контроля конца операнда первого блока

10 управления, старший разряд информационного выхода счетчика операнд соединен с тактовыми входами счетчика разрядов и второго блока микропрограммного управления, а счетный вход счетчика операндов

15 соединен с входом синхронизации устройства,.выходы второго блока микропрограммного управления с первого по третий, соединены соответственно с управляющими входами буферного регистра, входами

20 режима второго блока памяти и входом установки в нулевое состояние второго счетчика разрядов, информационный вход буферного регистра соединен с первым выходом второго блока оперативной памяти, 5 информационный выход буферного регистра соединен с вторым входом-выходом данных устройства, информационный выход регистра результата соединен с информационным входом регистров операнд с первого

0 по К-й и через схему "МОНТАЖНОЕ ИЛИ"— с первым информационным выходам регистра формата, информационные выходы регистров операнд с первого по К-й объединены через схемы "МОНТАЖНОЕ

5 ИЛИ" и соединены с информационным входом второго блока микропрограммного управления и с информационным входом регистра адреса, второй информационный вход второго блока микропрограммного упО равления соединен с вторым информационным выходом регистра формата, информационный выход регистра адреса соединен соответственно с адресным входом первого блока оперативной памяти, третий

5 выход регистра инструкций соединен с информационным входом второго блока оперативной памяти, выходы с четвертого по восьмой второго блока микропрограммного управления соединены соответственно с вто0 рым управляющим входом микроприказов первого арифметико-логического блока, вхо- . .дов чтения-записи первого регистра операнд, входом чтения — записи К-го регистра операндов, входом кода операции второго

5 арифметико-логического блока, входом чте. ния — записи регистра результатов, входом чтения — записи регистра адреса, информационный выход второго арифметика-логического блока соединен с информационным входом регистра результата, 1817099 р рер5оиу лОЯЦ f 1поР сии &ох.

gnppamulHou с с ссуа сл Р

Ком тр Номер Нси ер

$89Uc o 2 рег слрс (5G b, j-Za anepaH8u Я го опгРаи Р раЕол

onPJo Q 9ucl

К реРисл",,оа, onepîèЯо о.омер

nocneiweeo

onepaquu разряда фон, a.

Ф9

ИГЛ.с ЛГ ЛШП1лл во

3 L 1

В2 и с1 са

Ct6

tr /mopey Ело,гу иикролрог,о аминадо улра5денмд

Р/пггер начальноео

pcoY8p J_#_7

/-ео олерамдц,h о еР, начальног о раьр4 УФ

g-eî олеоанда

1817099

9СгпРоисл бо оБр а8огт кО цНф ии с леремен ной Вл «и аа комаи д

Составитель.Н,Голец

Техред M.Ìîðãåíòàë

Корректор Н,Кешеля

Редактор T.Èâàíîâà

Производственно-издательский комбинат."Патент", r. Ужгород, ул,Гагарина, 101

Заказ 1723 Тираж Подписное

8НИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5