Логический элемент

Иллюстрации

Показать всеРеферат

Использование: изобретение относится к микроэлектронике, более конкретно - к цифровым интегральным схемам (ИС) и может быть использовано во внутренних и выходных каскадах логических ИС и ИС запоминающих устройств. Сущность изобретения: логический элемент цифровых ИС на полевых транзисторах с барьерным переходом содержит логический вентиль НЁ- ИЛИ (1), выходной транзистор (5) и цепочку из п диодов смещения (6), резистивный делитель напряжения (7). 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 К 03 К 19/094

77

//2

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4919385/21 (22) 13.03.91 (46) 23.05.93. Бюл. М 1.9 (71) Московский институт электронной техники (72) В,И.Старосельский, В.И.Суэтинов;

Л.Н. Кравченко и А.Н.Сапельников (56) EDIU, 1984, June 28, р.225-232.

Семейство стандартных БИС фирмы

Viftesse//Ýëåêòð0Hèêà, 1986, т.59, М 19, с.21-,26. (54) ЛОГИЧЕСКИЙ ЭЛЕМЕНТ Ы, 1817239 А1 (57) Использование: изобретение относится к микроэлектронике, более конкретно — к цифровым интегральным схемам (ИС) и может быть использовано во внутренних и выходных каскадах логических ИС и ИС запоминающих устройств. Сущность изобретения: логический элемент цифровых ИС на полевых транзисторах с барьерным переходом содержит логический вентиль НЕИЛИ (1), выходной транзистор (5) и цепочку из п диодов смещения (6), резистивный делитель напряжения (7). 2 ил.

1817239

Изобретение относится к микроэлектронике, в частности к цифровым интегральным схемам (ИС) и может быть использовано во внутренних и выходных каскадах логических ИС и ИС запоминающих устройств, Цель изобретении — повышение стабильности высокого уровня выходного напряжения.

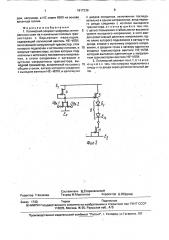

На фиг.1 представлена электрическая схема заявляемого логического элемента.

На фиг.2 — электрическая схема логического элемента-прототипа, выполненного на полевых транзисторах с затвором Шотки.

Логический элемент (фиг.1) содер>кит логический вентиль НŠ— ИЛИ 1 с входными транзисторами 2, 3 и нагрузочным транзистором 4, выходной транзистор 5, цепочку из п диодов смещения 6 и резистивный делитель напряжения 7, включающий резисторы 8 и 9, а также дополнительный диод 10 и нагрузку 1 1.

Сток нагруэочного транзистора 4 подключен к источнику питания Е1. Истоки входных транзисторов подключены к источнику постоянного напряжения Ео, а стоки соединены с затвором и истоком нагрузоч.ного транзистора. Логический вентиль

НŠ— ИЛИ 1 может иметь несколько управляющих входов, если используется несколько транзисторов 2„ включенных параллельно.

Выход вентиля HE — ИЛИ 1 соединен с затвором выходного транзистора 5, включенного по схеме с общим стокам. В цепь истока выходного транзистора 5 включена цепочка иэ и диодов 6, которые соединены последовательно в одном направлении. Анод первого диода 61 соединен с истоком транзистора

5. Резистор 8 делителя 7 подключен к катоду п-ro диода 6п, резистор 9 — к источнику опорного напряжения Еоп. Средняя точка делителя 7 подключена к затвору входного транзистора 3 вентиля 1.

В качестве транзисторов 2-Й могут использоваться полевые транзисторы с затвором Шотки или с управляющим р-и переходом, выполненные, например, на основе арсенида галлия или кремния. Нагруэочный транзистор 4 с объединенными электродами затвора и истока должен иметь встроенный канал. Входной транзистор 3 и нагрузочный транзистор 4 вентиля 1 выполняются в ИС идентичными.

Логический элемент работает следующим образом. Если хотя бы на один из управляющих входов (затворы транзисторов

2) вентиля 1 подается сигнал с высоким логическим уровнем напряжения, нв выходе вентиля 1 сигнал имеет низкий логический уровень. При этом выходной транзистор 5 закрыт, и на катоде и-го диода 6о, к которому подключена нагрузка Н1. формируется низкий уровень выходного напряжения. Через реэистивный делитель 7 выходное напряжение передается на затвор транзистора 3 логического вентиля 1, однако это не влияет на выходное напряжение вентиля 1. Таким образом, цепь обратной связи оказывается ра10 зорванной, Если на всех управляющих входах вентиля 1 сигнал имеет низкий уровень напряжения, переключаемые транзисторы 2 закрываются, и напряжения на затворе вы"5 ходного транзистора 5, истоке транзистора возрастают. Через делитель 7 повышение напряжения передается*на затвор транзистора 3, что ведет к увеличению его тока

20 стока Ice. Возрастание выходного напряжения продол>кается до тех пор, пока ток lca не

УРавновесит ток стока Ic4 нагРУзочного транзистора 4. Транзисторы 3 и 4 должны при этом работать в пологой области ВАХ, где их токи стока практически не зависят от напряжения сток-исток 0«и определяются только напряжением затвор-исток 0з . floскольку транзисторы 3 и 4 идентичны, а напряжение 0зи4 = 0 (затвор транзистора 4

30 СОЕДИНЕН С ИСТОКОМ), УСЛОВИЕ Icg = Ic4 ВЫПОЛняется при таком значении выходного напряжения 0вых, при котором 0зиэ = О. 1 1

Напряжение 0зиз определяется соотноше 1 нием

35 (2) 45

5 и, следовательно, на катоде и-го диода бл

0зиэ = К0вых + (1-К)Еоп — Ео, (1)

1 1 где К = Rg/(Rà+ Rg) — коэффициент передачи делителя 7, Из соотношения (1) при 0зиэ = 0

1 следует, что при условии

K = (Eo — Еоп)/(0вых — Еоп)

1 значение 0вых не изменяется при измене1 нии тока нагрузки, а также параметров транзистора и диодов смещения в широких пределах. В интегральных схемах температурные коэффициенты сопротивлений резисторов, выпОлненных в идентичных технологических условиях, одинаковы, поэтому коэффициент деления К и, следовательно, величина 0вых не зависят от

1 температуры.

Число и диодов смещения 6 выбирается таким образом, чтобы при низком уровне выходного напряжения Ue x транзистор 5 был закрыт: и> Ео+ (01 0пор 0вых )/0д, (3) 1817239 меньшем сопротивления нагрузки RH, что требует увеличения ширины канала выходного транзистора 5. Особенно существенно это при использовании логического элемента в качестве выходного каскада ИС, где коэффициент обьединения М может быть большим.

Отмеченный недостаток может быть устранен путем подключения нагрузки 11 к аноду п-го диода смещения 6п через дополнительный диод 10(нагрузка Нг на фиг.1). В этом случае при формировании высокого уровня выходного напряжения одним из М логических элементов, объединенных по выходу, и-ные диоды в остальных M-1 элементах оказываются закрытыми и не потребляют выходного тока от логического элемента, формирующего уровень Овых ., 1

Это расширяет функциональные возможности логического элемента, так как позволяет объединять по выходу большое число выходных логических элементов, используя их для реализации логической функции "ПРОВОДНОЕ ИЛИ".

Падения напряжений на диоде 10 и ином диоде смещения полностью компенсируются, если при Овых= Овца плотности тока

1 в диодах одинаковы. Это достигается надлежащим выбором ширины диода 10, Если условия работы исключают необ ходимость объединения логических элементов по выходу, первый способ подключения нагрузки (к катоду и-го диода без дополнительного диода) целесообразнее, так как обеспечивает большую стабильность значения Овых при изменениях тока нагрузки.

Таким образом, заявляемый логический элемент (фиг.1) обеспечивает стабильность высокого уровня выходного напряжения при вариациях параметров транзисторов, температуры и сопротивлений нагрузки.

В технических характеристиках ИС предусмотрена максимально допустимая величина высокого уровня выходного напряжения; поэтому применение предлагаемого логического элемента в качестве выходного каскада обеспечивает повышеwe выхода годных ИС, так как уровень Овых

1 ограничивается автоматически. Особенно существенно это при больших значениях коэффициента объединения по выходу М, тэк, как в заявляемом выходном каскаде исклю- чается повышение уровня Овых при работе

1 нескольких выходных каскадов на общую нагрузку.

Предлагаемый логический элемент может быть использован в цифровых ИС на полевых транзисторах с барьерным перехо10

Здесь 01 =- Uâûõ + пОд+ Озим — высо1 1 1 кий уровень выходного напряжения венти- 15 ля 1, Оэио — напряжение затвор-исток

1 выходного транзистора 5 при Овых- Овых .

Поскольку величина К лежит в диапазоне0< К 1, из соотношения(2)следует, что напряжения Овых . Ео и Еоп Ео должны 20

1 иметь разный знак.

При Опор = 0 6 В Овых =+1 В и Овых = 0

В условия (2), (3) и (4) выполнены при Ep= Е2= О, Е1=+ 4 В, Еоп=-2;4 В, К = 0,7 И П= 2, Указанные значения Ео, Е1, Е2, Еоп и 25

Опор соответствуют параметрам арсенид- галлиевых ИС серии 6500 на полевых транзисторах с затвором Шотки.

Отношение сопротивлений резисторов

8 и 9 задается значением коэффициента де- 30 ления К. Их абсолютные значения следует выбирать таким образом, чтобы ток, потреб- . ляемый резистивным делителем, был значительно меньше, чем входной ток в сопротивлении нагрузки. 35

Ширина канала выходного транзистора

5 выбирается таким образом, чтобы при напряжении затвор-исток, не превышающем напряжения отбирания барьерного перехода (около 0,8 В), его ток истока был достато- 40 чен для формирования высокого уровня выходного напряжения на нагрузке 11.

При подключении нагрузки 11 к катоду и-го диода смещениЯ 6п (Н1 на фиг.1) Резистивный делитель 7 снижает выходное со- 45 противление логического элемента, которОе при низком уровне выходного напряжения . (транзистор 5 закрыт) определяется суммарным сопротивлением плеч делителя:

Йвых = RQ + Rg где U1 — низкий уровень выходного напряо жения логического вентиля 1, Опор пороговое напряжение транзисторов, 0>-- 0,8 В— эффективное напряжение отпирания диодов 6.

Для работы транзисторов 3 и 4 в пологой области BAX при Овых = Овых их напря1 жения затвор-сток должны быть больше порогового напряжения, что обеспечивается при выполнении условий

E1+ Опор U1 > Ео+ 03иЗ вЂ” Опор. (4) 1 1

Снижение выходного сопротивления йвыхо огРаничивает коэффициент объединения по выходу M при работе логических элементов на общую нагрузку, так как выходные проводимости объединенных каскадов суммируются, и высокий уровень выходного напряжения формируется на сопротивлении

Йн эф (Ry + М (йз + Rg) ) 1817239 дом, например, в ИС серии 6500 на основе арсенида галлия, Составитель В,Старосельский

Техред M.Ìîðãåíòàë Корректор А.Обручар

Редактор Т.Козлова

Заказ 1730 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35. Раушская наб., 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, yn,Гагарина, 101

Формула изобретения

1. Логический элемент цифровых интегральных схем на и-канальных полевых транзисторах с барьерным переходом, содержащий логический вентиль НЕ-ИЛИ, включающий нагрузочный транзистор, сток которого подключен к источнику питания, и входные транзисторы, истоки которых под ключены к источнику постоянного напрях<ения, а стоки соединены с затвором и истоком нагрузочного транзистора, выходной транзистор, включенный по схеме с общим стоком, затвор которого соединен с выходом вентиля HE-ИЛИ, и цепочку из и диодов смещения, включенных последовательно в одном направлении, анод первого диода соединен с истоком выходного транзистора,отл ича ю щи йс я тем,что, 5 с целью повышения стабильности высокого уровня выходного напряжения, в него введен резистивный делитель напряжения, одно плечо которого подключено к катоду 0-го диода. второе к источнику опорного напря10 жения, а средняя точка к затвору одного из входных транзисторов вентиля HE — ИЛИ, который выполнен идентичным с нагрузочным транзистором вентиля HE-ИЛИ, 2. Логический элемент по п.1, о т л и ч а15 ю шийся тем, что нагрузка подключена к аноду n-ro диода через дополнительный диод.