Перемножитель электрических сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах. Сущность изобретения. Устройство содержит ключи 1-21, запоминающие конденсаторы 22-26. два интегрирующих конденсатора 27, 28, два операционных усилителя 29-30, р-канальный.МДП-транзистор 31, токовое зеркало 32, содержащее n-канэльные МДП-транэисторы 33-35, источник напряжения смещения 42, 2 ил. 1 табл.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (st)s G 06 G 7/161

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Ю

Ов

° °

Ъ

К АВТОРСК0МУ СВИДЕТЕЛЬСТВУ

Ф (21) 4897498/24 (22) 22.10.96 (46) 07.06.93, Бюл. 3Ф 21 (71) Новосибирский электротехнический институт связи им. Н.Д.Псурцева (72) Д.Л.Шлемин (56) Hong Z; IVlelchtor Н. Fovr-guadrant СМ0$

analogue multlpller//Electronics letters—

1984 по 24 — чо! 20 — рр. 1015-1016, (54) ПЕРЕМНОЖИТЕЛЬ ЭЛЕКТРИЧЕСКИХ

СИГНАЛОВ

„„5U „„1826396 А1 (57) Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах. Сущность изобретения, Устройство содержит ключи 1-21. запоминающие конденсаторы 22-26, два интегрирующих конденсатора 27, 28, два операционных усилителя 29-30, р-канальный.МДП-транзистор 31, токовое зеркало

32, содержащее и-канальные МДП-транзисторы 33-35, источник напряжения смещения 42. 2 ил. 1 табл.

1820396

Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах.

Цель изобретения — повышение точности перемножения.

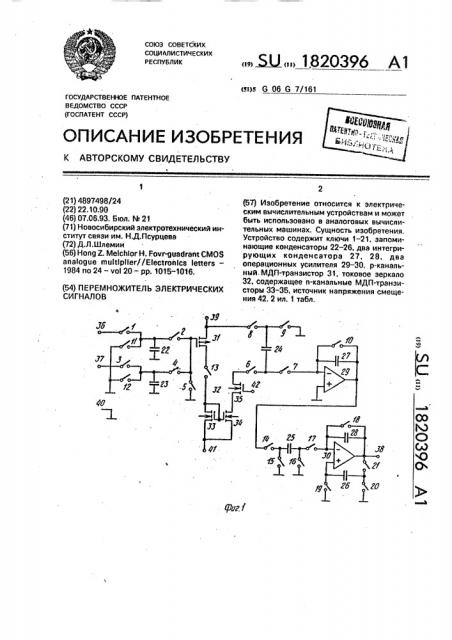

На фиг. 1 представлена принципиальная схема предлагаемого перемножителя электрических сигналов; на фиг. 2 — изображены временные диаграммы управляющих импульсов, Перемножитель электрических сигналов содержит ключи 1-21, запоминающие конденсаторы 22-26, интегрирующие конденсаторы 27, 28. операционные усилители

29, 30, р-канальный МДП-транзистор 31, токовое зеркало 32, содержащее и-канальные

МДП-транзисторы 33 — 35, входы устройства

Зб и 37, выход 38, положительную 39, общую .40 и отрицательную 41 шины источника напряжения питания, источник напряжения смещения 42.

Перемножитель электрических сигналов работает следующим образом.

Ключи перемножителя управляются импульсами, временные диаграммы приведены на фиг, 2. Соответствие между фазами управления и ключами устанавливается таблицей, На входы устройства 36 и 37 подаются перемножаемые напряжения Ux u Uy соответственно.

В течение первого импульса А запоминающий конденсатор 22 через ключ 1 заряжается до напряжения Ux, а запоминающий конденсатор 23 через ключ 3 — до напряжения Uy. Затвор транзистора 31 разряжается до нуля. Запоминающий конденсатор 24 также разряжается через инвертирующий вход ОУ 29.

В течение первого импульса В замыкаются ключи 2 и 4, при этом на затворе транзистора 31 устанавливается напряжение (Ux+ Uy)/2 {при одинаковых емкостях первого и второго запоминающих конденсаторЬв

22 и 23). Таким образом, через транзистор

31 начинает протекать ток - к (+- — и+ — u,ß, поскольку замыкается ключ 13. При этом заряжается запоминающий конденсатор24 через ключ 6 и токовое зеркало 32 на транзисторах 33-35. Заряд, полученный этим конденсатором к окончанию первого импульса В, при единичном коэффициенте передачи токового зеркала будет равен:

Q1- КТ (— "2 — — U — Ur), где Т вЂ” продолжительность импульса В,.

Интегрирующий конденсатор 27 будет разряжен через ключ 10, интегрирующий конденсатор 28 — через ключ 18, а запоминающий конденсатор 25 — через ключи 15 и

16. Кроме того, поскольку неинвертирующий вход ОУ ЗО подключен к общей шине в данный момент, на его входе устанавливается напряжение смещения этого ОУ, до величины которого зарядится запоминающий

10 конденсатор 26.

В течение второго импульса А запоминающие конденсаторы 22 и 23, а также затвор транзистора 31 разряжаются до нуля, а заряд 01, накопленный запоминающим

15 конденсатором 24, передается в интегрирующий конденсатор 27, конденсатор 24 при этом разряжается. На выходе ОУ29 появится напряжение (при равенстве емкостей конденсаторов 24 и 27) U = 01/С, где С—

20 емкость конденсатора 24. До этого же напряжения зарядится запоминающий конденсатор 25 через ключ 14, В течение второго импульса В запоминающий конденсатор 24 посредством про25 цессов, аналогичных протекавшим в течение предыдущего импульса В, получит заряд .

02 = КТ(Π— U От)

Кроме того, интегрирующий конденса30 тор 28 получит заряд, накопленный, ранее конденсатором 25, поскольку замкнулись ключи 15 и 17. На неинвертирующий вход

ОУ 30 с запоминающего конденсатора 26 подается напряжение. обратное по закону

35 напряжению. смещения, до которого этот. конденсатор зарядился ранее. Следовательно, напряжение смещения ОУ 30 оказы вается скомпенсированным. Таким образом, на выходе перемножителя при ра40 венстве емкостей конденсаторов 25, 28. 24 и 27 устанавливается напряжение 0 = О>/С.

Конденсатор 25 будет разряжен.

В течение третьего импульса А запоми45 нающий конденсатор 22 зарядится до на пряжения Ох, а запоминающий конденсатор

23 разрядится до нуля. На выходе первого

ОУ 29 установится напряжение 0 - 02/С, до которого зарядится конденсатор 25.

50 В течение третьего импульса В на затворе транзистора 31 установится напряжение

Ux/2, а запоминающий конденсатор 24 получит заряд

55 03 КТ (— -0 — От)

В то же время интегрирующий конденсатор 28 получит заряд Qz и напряжение на выходе перемножителя будет ц=(01 + 02)/С.

1820396

В течение четвертого импульса А второй запоминающий конденсатор 23 зарядится до напряжения Uy, На выходе ОУ 29 установится напряжение U = Оэ/С. Кроме того. поскольку ключ 17 остается замкнутым, интегрирующий конденсатор 28 теряет заряд

Оз. На выходе перемножителя устанавливается напряжение

U = (Qi + Qz — Оэ)/С . В течение четвертого импульса В на затворе транзистора 31 устанавливается напряжение Uy/2, а запоминающий конденсатор 24 получит заряд

Q4=кт(-u u,)

Запоминающий конденсатор 25 разряжается через ключи 15 и 16. На этом цикл работы перемножителя завершается.

В течение первого импульса А нового цикла на выходе ОУ 29 устанавливается напряжение 0 = Qp/С, а интегрирующий конденсатор 28 теряет заряд Q4. На выходе перемножителя устанавливается напряжеwe

U = (Ql + Ог — 0з — 04)/С = 2 С Uxuy, КТ т,е. результат перемножения напряжений

Ux u Uy с масштабным коэффициентом

КТ/2С.

В течение первого импульса В нового цикла интегрирующий конденсатор 28 разряжается и готов к накоплению результата нового цикла.

Таким образом, предлагаемое устройство обладает повышенной точностью перемножения, поскольку запоминающий конденсатор 24 заряжается током только одного р-канального транзистора.

Формула изобретения

Перемножитель электрических сигналов, содержащий первый операционный усилитель, неинвертирующий вход которого соединен с.общей шиной, с "eðeîão по десятый ключи, с первого по третий запоминающие конденсаторы, первый интегрирующий конденсатор, первые выводы первого и второго ключей соединены, первые выводы третьего и четвертого ключей соединены, а вторые выводы второго и четвертого ключей соединены с первым выводом пятого ключа, второй вывод пятого ключа соединен с общей шиной, первые выводы шестого и седьмого ключей соединены, первые выводы восьмо;о и девятого ключей соединены, второй вывод девятого ключа подключен к общей шине, а второй вывод. седьмого ключа соединен с инвертирующим входом первого операционного усилителя, первый вывод десятого ключа подключен к. инвертирующему входу первого операционного усилителя, а второй вывод десятого ключа соединен с выходом первого операционного усилителя, вторые выводы первого и третьего ключей подключены

5 соответственно к первому и второму входам перемножителя, первый вывод первого запоминающего конденсатора подключен к первым выводам первого и второго ключей, а первый вывод второго запоминающего

10 конденсатора соединен с первыми выводами третьего и четвертого ключей, вторые . выводы первого и второго запоминающих конденсаторов подключены к общей шине, а первый вывод третьего запоминающего

15 конденсатора соединен с первыми выводами шестого и седьмого ключей, второй вы-. вод третьего запоминающего конденсатора подключен к первым выводам восьмого и девятого ключей, первый интегрирующий

20 конденсатор включен между инвертирующим входом и выходом первого операционного усилителя, р-канальный

МДП-транзистор, исток которого соединен с положительной шиной источника питания, 25 а затвор подключен к первому выводу пятого ключа, отличающийся тем, что, с . целью повышения точности перемножения, в него введены с одиннадцатого по двадцать первый ключи, второй операционный

30 усилитель, четвертый и пятый запоминающие конденсаторы, второй интегрирующий конденсатор, первые выводы одиннадцатого и двенадцатого ключей соединены с вторыми выводами соответственно, первого и

-35 третьего ключей, а вторые выводы соединены с общей шиной, токовое зеркало, содержащее первый, второй и третийи-канальные МДП-транзисторы и тринадцатый ключ, первый вывод которого подклю40 чен к стоку р-канального МДП-транзистора, а второй вывод соединен со стоком и затвором первого и-канального МДП-транзистора, истоки первого и второго п-канальных

МДП-транзисторов подключены к отрица45 тельной шине источника питания, затвор второго и-канального МДП-транзистора соединен с затвором первого и-канального

МДП-транзистора, а сток второго и-каналь. ного МДП-транзистора подключен к истоку

50 третьего и-канального МДП-транзистора, . затвор которого подключен к источнику напряжения смещения, а сток соедичен с вторым выводом шестого ключа, первые выводы четырнадцатого и пятнадцатого

55 ключей подключены к первому выводу четвертого запоминающего конденсатора, а второй вывод четырнадцатого ключа соединен с выходом первого операционного усилителя, первые выводы шестнадцатого и семнадцатого ключей подключены к второ1820396 му выводу четвертого запоминающего конденсатора, вторые выводы пятнадцатого, шестнадцатого, девятнадцатого и двадцатого ключей соединены с общей шиной, а вто рой вывод самнадцатого и первый вывод восемнадцатого ключей подключены к инвертирующему входу второго операционного усилителя, второй вывод восемнадцатого ключа соединен с выходом второго операционного усилителя, при этом первый вывод второго интегрирующего конденсатора подключен к инвертирующему входу второго операционного усилителя, а второй вывод-. к выходу второго операционного усилителя, первый вывод пятого запоминающего конденсатора и первый вывод девятнадцатого ключа подключены к неинвертирующему

5 входу второго операционного усилителя, второй вывод пятого запоминающего конденсатора и первые выводы двадцатого и двадцать первого ключей соединены, ори

° этом второй вывод двадцать первого ключа

10 подключен к выходу операционного усищателя, второй вывод восьмого ключа соединен с положительной шиной источника питания.

1820396

Составитель Д. Шлемин

Редактор С. Кулакова Техред M.Моргентал Корректор Н. Король

Заказ 2031 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г, Ужгород. ул.Гагарина, 101