Устройство для измерения времени установления цифроаналоговых преобразователей

Иллюстрации

Показать всеРеферат

Изобретение относится к измерительной технике, может быть использовано для измерения и допускового контроля времени установления цифроанэлоговых преобразователей (ЦАП) и позволяет расширить функциональные возможности путем дополнительной способности измерения динамического параметра от результата воздействия любой сменяемой преобразуемой информации. Задатчик 1 кода задает диапазон измерения, а источники 22 и 23 напряжения. УВХ 31 и резисторы 16-21 задают зоны установившихся значений напряжения с выхода контролируемого ЦАП 39. Блок 2 элементов И, цифровой компаратор 5, генератор 3 импульсов, реверсивный счетчик 4, триггер 7 обеспечивают динамический режим работы контролируемого ЦАП 39. Элементы И 8 и 9. счетчик 10, цифровой компаратор 6 определяют момент съема информации с компараторов 11 и 12 напряжения . Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 13 элемент задержки 33, элемент И 34, первый RS-триггер 32 формируют окончание процесса измерения. Задатчики кода 24 и 25, блоки элементов И 26 и 27, элемент ИЛИ 29 обеспечивают измерение времени установления ЦАП 39 при его переключении с большего преобразуемого кода на меньший и наоборот. Второй RS-триггер 36, элемент И 35, резистор 37 и конденсатор 38 обеспечивают работу устройства после смены кодов задатчиков, обеспечивающих режим испытания ЦАП 39. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (sl)5 Н 03 M 1/10

ГОСУДАРСТВЕН.ЮЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Sh

° " г

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4918145/24 (22) 11.03.91 . (46) 07,06.93. Бюл. hk 21 (71) Пензенское производственное объединение "Завод им. Фрунзе" (72) Г,С.Власов, Н.А.Ермолаев и В.Г.Сараев (56) Авторское свидетельство СССР

М 790298, кл. Н 03 М 1/10. 1980.

Авторское свидетельство СССР

М 1223366, кл. Н 03 M 1/10, 1986. (54) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ВРЕМЕНИ УСТАНОВЛЕНИЯ ЦИФРОАНАЛО.ГОВЫХ ПРЕОБРАЗОВАТЕЛЕЙ (57) Изобретение относится к измерительной технике, может быть использовано для измерения и допускового контроля времени установления цифроаналоговых преобразо. вателей (ЦАП) и позволяет расширить функциональные возможности путем дополнительной способности измерения динамического параметра от результата воздействия любой сменяемой преобразуемой информации. Задатчик 1 кода задает Ы,„, I820482 А1 диапазон измерения, а источники 22 и 23 напряжения, УВХ 31 и резисторы 16 — 21 задают зоны установившихся значений напряжения с выхода контролируемого ЦАП 39, Блок 2 элементов И, цифровой компаратор

5, генератор 3 импульсов, реверсивный счетчик 4, триггер 7 обеспечивают динамический режим работы контролируемого ЦАП

39. Элементы И 8 и 9. счетчик 10, цифровой компаратор 6 определяют момент съема информации с компараторов 11 и 12 напряжения. Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 13 элемент задержки 33, элемент И 34, первый

RS-триггер 32 формируют окончание процесса измерения. Задатчики кода 24 и 25, блоки элементов И 26 и 27, элемент ИЛИ 29 обеспечивают измерение времени установления ЦАП 39 при его переключении с большего преобразуемого кода на меньший и наоборот. Второй RS-триггер 36, элемент И

35, резистор 37 и конденсатор 38 обеспечивают работу устройства после смены кодов задатчиков, обеспечивающих режим испытания ЦАП 39. 2 ил.

1820482 выход которого соединен с входом "Вычитание" реверсивного счетчика 4 и с вторым входом второго элемента Р 9, выход первого элемента И 8 соединен со счетным входом счетчика 10, первый вход — со счетным входом триггера 7 и с выходом первого цифрового компаратора 5, второй вход которого соединен с выходом реверсивного счетчика

4 и с первым входом второго цифрового

10 компаратора 6, второй вход которого соединен с выходом счетчика 10. а выход — с первым входом второго элемента И 9, Вход обнуления реверсивного счетчика 4 подключен к входу й-обнуления триггера 36, пря15 мой вход которого через резистор 37 соединен со своим инверсным выходом и через конденсатор 38 с нулевой шиной, а прямой выход подключен к первому входу элемента И 35, второй вход которого соединен с выходом элемента И 9, а выход подключен к стробирующим. входам компараторов 11 и 12, выходы которых подключены к входам элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 13, выход генератора 3

25 импульсов подключен к счетному входу реверсивного счетчика 4. Инверсный выход устройства 31 выборки и хранения подсоединен к второму 17 и четвертому 19 резисторам R, управляющий вход через

30 одновибратор 30 соединен с выходрм элемента 2И-ИЛИ 28, а вход аналогового сигна-ла подключен к входной клемме и к первому

16 и третьему 18 резисторам R, вторые вы- воды которых соединены с вторыми выводами второго 17 и четвертого 19 резисторов R, c ïåðâûìè выводами компараторов 11 и 12 напряжения и через резисторы R> 20 — 21 с противоположными полюсами первого и второго источников 22 и 23 опорного напря"0 жения, другие полюсы которых подключены к общей шине и другим входам компараторов 11 и,12 напряжения, причем вторая управляющая клемма 15 соединена с вторым прямым и четвертым инверсным входами

55. чен к выходной шине устройства, а первый

Изобретение относится к измерительной технике и может быть использовано для измерения и допускового контроля времени установления цифроаналоговых преобразователей (ЦАП).

Целью изобретения является расширение функциональных возможностей путем обеспечения способности устройства измерять время установления при смене любых преобразуемых кодовых комбинаций.

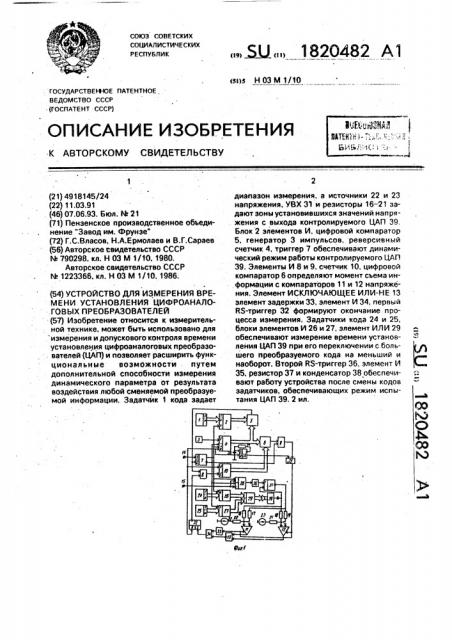

На фиг,1 изображена функциональная схема устройства; на фиг.2 — эпюры напря.жений на выходах соответствующих узлов и блоков функциональной схемы. Временные диаграммы 0з, От, Ug; 0зэ, 014, 0зв — напря жения на-выходах элементов функциональной схемы: генератора 3 импульсов, триггера 7, второго элемейта И9, на выходе испытуемого ЦАП 39, первой управляющей клеммы 14, RS-триггера 36;

01, 0л, U1 -04 — эквивалентные опор1 1 ные напряжения, устанавливающие границы зон вхождения сигнала испытуемого

ЦАП при его динамических испытаниях;

Тдрр период, пропорциональный коду задатчика 1 кодов;

t1, тг — интервалы времени разрешения . для компараторов 11 и 12 напряжения.

Устройство содержит задатчик 1 кода, являющийся по существу задатчиком периода переключения испытуемого ЦАП (задатчик диапазона измерения, который позволяет программно изменять период воздействия входного .сигнала на испытуемый ЦАП), блок 2 элементов И,тенератор 3 импульсов, реверсивный счетчик 4, цифровые компараторы 5 и 6, триггер 7, элементы

И 8 и 9, счетчик 10, стробируемые компараторы 11 и 12 напряжения, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 13, управляющие клеммы 14 и 15, резисторы R 16-19, резисторы Rn 20-21, источники 22 и 23 опорного напряжения, задатчики 24 и 25 кода, блоки

26 и 27 элементов И, элемент 2И-ИЛИ 28, элемент ИЛИ 29, одновибратор 30, устрой- 4 ство 31 выборки и хранения (УВХ), RS-триггер 32, элемент 33 задержки, элементы И 34 и 35, RS-триггер 36, резистор 37, конденсатор 38, испытуемый ЦАП 39, Первая управляющая клемма 14 подключена к входу R-обнуления реверсивного счетчика 4, входу S триггера 7, входу R-обнуления счетчика 10, выходная шина первого задатчика 1 кодов подключена к первому входу. блока элементсв И, выход которого подсоединен к первому входу первого цифрового компаратора 5, а второй управляющий вход соединен с входом

"Суммирование" реверсивного счетчика 4 и ... с прямым выходом триггера 7, инверсный элемента 2И-ИЛИ 28, первый вход которого соединен с управляющим входом второго блока элементов И 26 и с прямым выходом триггера 7, инверсный выход которого соединен с третьим входом элемента 2И-ИЛИ

28 и управляющим входом третьего блока элементов И 27, информационный вход которого соединен с выходом третьего задатчика 25 кодов, выход — с вторым входом элемента ИЛИ 29, выход которого подклювход соединен с выходом второго блока элементов И 26, информационный вход которого соединен с выходом второго задатчика 24 кодов, а выход элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ-НЕ 13 соединен с первым входом

1820482 третьего элемента И 34. второй вход которого через элемент 33 задержки соединен с входами стробирования компараторов 11 и

12 напряжения, выход же подключен к Sвходу RS-триггера 32, R-вход которого соединен с первой управляющей клеммой 14, а инверсный выход- с вторым входом первого элемента.

Устройство работает следующим образом.

При поступлении управляющего импульса 0<> (стартовый сигнал) на первую управляющую клемму 14 триггер 7 устанавливается в единичное состояние, обнуляется реверсивный счетчик 4 и счетчик

10, устанавливается в нулевое состояние

RS-триггер 32. Одновременно импульс Ос> поступает на R-вход RS-триггера 36, устанавливая его в нулевое состояние, которое будет поддерживаться до тех пор, пока не зарядится конденсатор 38 через резистор

37. Сформированный на выходе RS-триггера 36 импульс длительностью Тстудерживает в закрытом состоянии элемент И 35.

Триггер 7; устанавливаясь в единичное состояние, разрешает прохождение импульсов генератора 3 импульсов на суммирование реверсивного счетчика 4.

Одновременно приходит сигнал разрешения на первый блок 2 элементов И, который пропускает при этом кодовую комбинацию с выхода первого эадатчика 1 кодов на первый вход цифрового компаратора 5.

При достижении на выходе реверсивного счетчика 4 кодовой комбинации; эквивалентной той, которая поступает на первый вход цифрового компаратора 5, на выходе появляется импульс, который перебрасывает триггер 7 в противоположное состояние и проходит через элемент И 8 на счетный вход счетчика 10, записывая в его памяти единицу. Далее реверсивный счетчик 4 работает на вычитание, блок 2 элементов И не пропускает кодовой комбинации с выхода первого задатчика 1 кодов, поэтому на первом входе цифрового компаратора 5 присутствует нулевой код, предопределяя таким образом появление на выходе цифрового компаратора 5 второго импульса пря достижении на выходе реверсивного„счетчика 4 нулевой кодовой комбинации. Но перед этим срабатывает цифровой компаратор 6, сигнал с которого появится раньше, чем на выходе цифрового компаратора 5 на длительность, равную периоду импульсов задающего генератора 3, Через интервал времени Тс с начала запуска этот сигнал придет через второй элемент И 9 и через элемент И 35 на стробируемые входы компараторов 11 и12 напряжения, осуществляя тем самым опрос их состояния. Инта::.-л времени Т, на который после начала з=,пуска закрыт элемент М 35. необходим для обеспечения запоминания устаноьиВШ гс," ся уровня сигнала испытуемого ЦАП пер;ед началом его компарирования. В свою очередь компараторы 11 и 12 напряжения в момент прихода "строб"-импульса будут находиться в определенном состоянии. Если, 10 например, сигнал, снимаемый с выхода испытуемого ЦАП 35, находитс1я внчтаи опорной зоны 01, Оъ Оз, 04, О1, Uz и т.д. (см, фиг.2., эпЮра 35), то компаратор 1": будет находиться в единичном состоянии, а кпмпаратор 12- в нулевом. При этом с Выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 13 будет сниматься логический "0". При зтом икпульс напряжения не пройдет через логический элемент И 34 на S-вход RS--1риггера 32, который останется при этом в нулевом состоянии. На фиг.2 T - длительность периода поступления импульсов напряжения с выхода цифрового компаратора 5, в свою очередь это половина периода работы

20 триггера 7: tt-т2 — интервалы времени стробирования компараторов 11 и 12. . Пороговые зоны 01 — Uz и т.д. формируются благодаря элементу 2И-ИЛИ 28, одновибратору 30, устройству 31 выборк

30 хранения 1, резисторам 16-21 и опор -i;. элементам 22 и 23. Синхронно с приВязкой к фронту сигнала с выхода триггера 7 происходит опрос испытуемого ЦАП 39 устроэс-:вом УВХ 31, так что контроль времени установления на "спаде" и на "фронте" заэтом сопротивления резисторов 16-19 Выбираются одинакового номинала, а сопоотивление резисторовйл 20 и 21 Выбираю -СЯ в зависимости от значения напряже:.ия опорных источников 22 и 23 из соотношения

50 еы.и -(т+1) ю д Е где Rn- подстроечного типа; m — число разрядов ЦАП 39. Иа графике Оз9 (фиг,21 штриховыми линиями Озэ, 039 изображены динамические процессы на выходе ис-.ыту" емого ЦАП 39 при различных кода", снимаемых с выходов второго и треть"=ro задатчиков 24 и 25 кодов. висят от уровня логического сигнала на клемме 15, Пря этом одновибратор 30 позволяет записывать в УВХ устанОВиВшийсЯ на выходе ЦАП 39 процесс.

40 Токовая схема суммирования на злементах 16-17, 20 и 18-19, 21 позволит с высокой точностью и простотой органи.=;— вать опорйую зону 01-Uz, Ua-Un и т.д, При

1820482

Следующий опрос компараторов 11 и 12 напряжения произойдет на интервале времени 1г (см,фиг.2).

Так как с каждым последующим опросом компараторов 11 и 12 напряжения растет число в счетчике 16 импульсов, То естественно происходит и сдвиг стробирующего импульса в начало переходного процесса. В тот момент, когда напряжение на выходе испытуемого ЦАП 39 (см.фиг.2, Озэ) выйдет из опорной зоны U>-Uz, состояние компараторов станет либо "0" — "0", либо "1"

; "1", где "0" — логический ноль,."1" — логическая единица, При этом на S-axopxpurrepa 32 пройдет импульс напряжения и установит его в единичное состояние, Триггер 32 при этом выдаст на второй вход первого элемента И 8 сигнал, запрещающий дальнейшее поохождение в счетчик 10 импульсов. В счетчике 10 одного состояния в другое на результат измерения..

Результирующее значение времени установления подсчитывается следующим образом (2) lyci = (N1 ч2) Т где Nl- код на выходе задатчика 1 кодов;

Nz — код, установленный в счетчике 10;

Т вЂ” период импульсов задающего генератора 3, Таким образом, предложенное устройство обладает в сравнении с прототипом сравнительной простотой и более широкими функциональными воэможностями при сохранении точности измерения.

Формула изобретения устройство для измерения времени установления цифроаналоговых преобразователей, содержащее последовательно соединенные первый задатчик кода, первый блок элементов И, первый цифровой компаратор, вторые входы которого объединены с соответствующими первыми входами второго цифрового компаратора и подключены к соответствующим выходам реверсивного счетчика, первый вход которого соединен с выходом генератора импульсов, вход объединен с управляющим входом первого блока элементов И и подключен к прямому выходу счетного триггера, вход установки в

"1" которого объединен с третьим входом реверсивного счетчика, входом установки в

"0" счетчика и является шиной "Пуск", а счетный вход объединен с первым входом останется кодовая комбинация Nz. Элемент

33 задержки, элемент И 34 и RS-триггер 32 повышают надежность в работе устройства, позволяя исключить влияние переходов из

20

40

50 первого элемента И и подключен к выходу первого цифрового компаратора. выход второго цифрового компаратора соединен с первым входом второго элемента И, а вторые входы соединены с соответствующими выходами счетчика, счетный вход которого соединен с выходом первого элемента И, два компаратора напряжения, два источни-. ка опорного напряжения и элемент ИСКЛ ЮЧАЮЩЕЕ ИЛИ, отличающееся тем, что, с целью расширения области применения, в него введены четыре преобразователя напряжение-ток, каждый из которых выполнен из резистора, два токозадающих

5 элемента, каждый из которых выполнен на резисторе, два RS-триггера, элемент обратной связи, выполненный на резисторе, накапливающий элемент, выполненный на конденсаторе. два задатчика кода, два блока элементов И, элемент 2И-ИЛИ, два элемента И, элемент задержки. одновибратор, блок элементов ИЛИ и устройство выборки и хранения, инверсный выход которого соединен с первыми выводами первого и вто5 рого резисторов, второй вывод последнего соединен с первыми выводами третьего и четвертого резисторов и подключен к первому входу первого компаратора напряжения, второй вход которого и первый вход второго компаратора напряжения являются шиной нулевого потенциала, стробирующие входы первого и второго компараторов напряжения объединены с входом элемента задержки и подключены к выходу третьего

5 элемента И, первый вход которого соединена с выходом второго элемента И, а второй вход с прямым выходом первого RS-триггера, инверсный выход которого через первый резистор соединен с входом установки в "1" первого RS-триггера и первым выводом конденсатора, второй вывод которого является шиной нулевого потенциала, а вход установки в "0" первого RS-триггера является шиной "Пуск", причем четвертый вход

5 реверсивного счетчика объединен с вторым входом второго элемента И, первым входом элемента 2И-ИЛИ, управляющим входом второго. блока элементов И и подключен к инверсному выходу счетного триггера, прямой вход которого соединен с управляющим входом третьего блока элементов И и вторым входом элемента 2И-ИЛИ, третий и четвертый входы которого являются управляющей шиной, а выход через одно5 вибратор соединен с управляющим входом устройства выборки и хранения, информационный вход которого соединен с первым выводом шестого резистора, вторым выводом третьего регистра и является входной шиной, а второй вывод шестого резистора

1820482

Корректор Н. Кешеля

Составитель Г. Власов

Техред М.Моргентал

Редактор

Заказ 2036 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/S

Производственно-издательский комбинат "Патент, г. Ужгород, ул.Гагарина, 101 обьединен с вторым выводом первого резистора, первым выводом седьмого резистора и подключен к второму входу второго компаратора напряжения, выход которого и вы-ход первого компаратора напряжения 5 соединены соответственно с первым и вторым входами элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ-НЕ, выход которого соединен с первым входом четвертого элемента И, второй вход которого соединен с выходом элемента 10 задержки, а выход c S-входом второго RSтриггера, R-вход которого является шиной

"Пуск", а инверсный выход соединен с вторым входом первого элемента И, при этом входы второго и третьего блоков элементой

И соединены соответственно с соответствующими выходами второго и третьего задатчиков кодов, а выходы соединены с соответствующими первыми и вторыми входами блока элементов ИЛИ, выходы которого являются выходной шиной, а выходы первого и второго источников опорного напряжения соединены с вторыми выводами четвертого и седьмого резисторов соответственно.