Устройство для приема дискретных сигналов

Иллюстрации

Показать всеРеферат

Устройство содержит: 1 ограничитель

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧ Е СКИХ

РЕСПУБЛИК

est)s Н 01 3 27/14

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4875795/09 (22) 16,10.90 (46) 23,06.93. Бюл. М 23 (71) Самарский электротехнический институт связи (72) А.И.Тяжев и А.М, Глотов (56) Бухвинер В.Е. Дискретные схемы в фазовых системах радиосвязи.— M,: Связь, 1969, с. 61. (54) УСТРОЙСТВОДЛЯ ПРИЕМАДИСКРЕТНЫХ СИГНАЛОВ (57) Устройство содержит: 1 ограничитель (1), 1 аналого-цифровой преобразователь

„„5U„„1823146 А1 (2), 1 блок вычисления амплитуды (3), 2 фазовращателя (4, 11), 2 решающих блока (5, 12), 4 управляемых ключа (6, 9, 14, 16). 1 выделитель фронтов и следов (7), 1 регистр (8), 1 выделитель фронтов (10), 1 RS-триггер (13), 1 Т-триггер (14), 1 инвертор (17), 2 формирователя импульсов (18, 19). 1 делитель частоты (20), 1 элемент И (21), 1 элемент ИЛИ (22). 1 генератор тактовых импульсов (23), 1 анализатор формы сигнала (24), 1 — 7 — 11 — 1618 — 21 — 20-17 — 10-2-8 — 12 — 14-19 — 22 — 21. 2—

3-5 — 9-13, 3 — 12 — t6, 2 — 5 — 6-13, 10 — 4 — 9, 1 — 4 — б, 10 — 8. 7 — 24 — б, 24 — 9, 24 — 14, 24 — 1 б, 2015 — 11 — 14, 23 — 22. 2 ил.

1823146

Изобретение относится к радиотехнике, Цель изобретения -- обеспечение приема сигналов, передаваемых с использованием частной манипуляцией с минимальными отвесом.

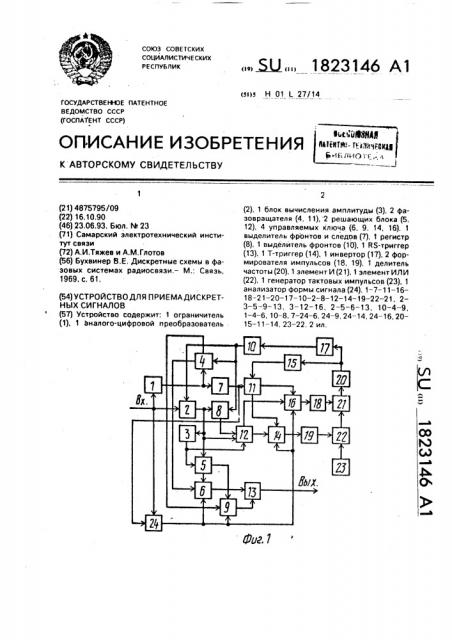

l4a фиг,1 изображение структурная электрическая схема предложенного устройства; на фиг,2 — схема арматура формы сигнала, Устройство содержит ограничитель 1, аналого-цифровой преобразователь (АЦП)

2, блок 3 вычисления арматуры, первый фазорасширитель 4, первый решающий блок

5, третий управляемый ключ 6, выделитель

7 фронтов и срезов, регистр 8, четвертый управляемый ключ 9, выделитель 10 фронтов, второй фазорасщепитель 11, отарой решающий блок 12, RS-триггер 13, первый управляемый ключ 14, Т-триггер 15, второй управляемый ключ 16, инвертор 17, второй формирователь 18 импульсов, первый формирователь 19 импульсов, делитель 20 частоты, элемент И 21, элемент ИЛИ 22, генератор 23 тактовых импульсов, анализатор 24 формы сигнала. Анализатор 24 содержит выпрямитель 25, электронный ключ 26, пороговый блок 27, счетчики 28, 29.

Устройство работает следующим образом.

Принимаемые сигналы поступают одновременно на входы ограничители 1, АЦП 2 и анализатора 24, на выходе которого в зависимости от формы входного сигнала устанавливается высокий уровень единицы или низкии уровень нуля. Этот уровень поступает и» упраолчющие входы всех четырех управляемых ключей 6, 9, 14, 16, Если на вход заявляемого устройства поступает дискретный сигнал то на выходе анализатора 24 устанавливается уровень единицы, который воздействует на чегыре управляемых ключа

6,9, 14, 16.

Если же на вход заявляемого устройства поступает сигнал с использованием часто гной модуляции с минимальным сдвигом, lo на выходе анализатора 24 устанавливается уровень нуля, который воздействует на четыре управляемых ключа 6, 9, 14 и 16 таким образом, что ко входам RS-триггера

13 подключается выходы решающего блока

5, а к формирователчм 18 и 19 место выходов фазооращателя 11 подключаются соответственно выходы решающего блока 12. В результате такого изменения конфигурации подстройка фазы импульсов на выходе делителя 20 осуществляется по описанному выше механизму, но под действием сигналоо с выходов решающего блока 12. На его входы поступает очередная выборка иэ

55 входного сигнала с выхода АЦП 2 и задержанная на длительность посылки Т выборки из сигнала с выхода регистра 8. На соответствующий вход решающего блока 12 поступает значение амплитуды сигнала с выхода блока 3. Подстройка фазы происходит по знаку выборки, попадающей на колебания удвоенной частоты, с учетом знака задержанной в регистре 8 выборки, Если эта выборка попадает примерно на середину колебания удвоенной частоты, то она по модулю значительно меньше амплитуды сигнала частотной манипуляции с минимальным сдвигом, Этот фактор является признаком того. что знак данной выборки можно использовать для подстройки фазы импульсов с выхода Т-триггера 15, При этом, если предыдущая выборка по модулю велика и близка к амплитуде. тогда при одинаковых знаках очередной и предыдущей выборке формируется импульс добавления. При разных знаках очередной и предыдущей выборок формируется импульс исключения. В других случаях когда обе выборки по модулю велики или обе малы, импульсы добавления и исключения не формируются, Таким образом обеспечивается фазирование импульсов управления моментами выборки из входного сигнала, поступающими на управляющие входы АЦП 2 и регистра 8 с выхода выделителя 10, Формирование выходного сигнала осуществляется с помощью решающего блока 5. На фиг. его вход поступает выборка с выхода АЦП 2, а на другой вход— значение амплитуды сигнала с выхода блока

3. Если выборка по модулю близка к амплитуде сигнала, то, в зависимости от ее знака формируется импульс на одном иэ двух выходов решающего блока 5. При положительной выборке этот импульс с одного выхода решающего блока 5 через управляемый ключ 6 поступает на S-вход RS-триггера 13 и устанавливает его в единицу. При отрицательной выборке импульс появляется на другом выходе решающего блока 5 и через управляемый ключ 9 поступает на

R-вход RS-триггера 13 и устанавливает его в нуль, Если выборка из сигнала по модулю гораздо меньше амплитуды сигнала, в этом случае импульсы на выходах решающего блока 5 отсутствуют, поэтому RS-триггер 13 не изменяет своего состояния

Блок вычисления амплитуды работает следующим образом, Он отбрасывает малые по модулю выборки и усредняет модули большим выборок.

Анализатор формы сигнала определяет наличие полуволн длительностью около

То/2 свидетельствуют о том. что на входе

1823146

Фиг 2

Составитель Н,Лазарева

Техред М.Моргейтал Корректор M.Êåðåöìàí

Редактор

Заказ 2187 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101 устройства действует сигнал частотной манипуляции с минимальным сдвигом.

Отсутствие или редкое появление на его входе полуаолн сигнала длительностью

To/2 свидетельствует о действии на входе устройства дискретной сигнала.

Формула изобретения

Устройство для приема дискретных сигналов, содержащее последовательно соединенные генератор тактовых импульсов, элемент ИЛИ, элемент И, делитель частоты инвертор, выделитель фронтов и первый фазорасщепитель. ограничитель, вход которого -является входом устройства, а выход соединен с вторым входом первого фаэа расщепителя и входом выделителя фронтов и срезов, выход которого соединен с первым входом фазорасщепителя, второй вход которого соединен с выходом Т-триггера, вход которого соединен с выходом делителя частоты, первый формирователь импульсов, выход которого соединен с вторым входом элемента ИЛИ. второй формирователь импульсов, выход которого соединен с вторым входом элемента И, а также RS-триггер, выход которого является выходом устройства, о т л и ч а ю щ е е с я тем, что, с целью обеспечения приема сигналов, передаваемых с использованием частотной манипуляции с минимальным сдвигом, введены анализатор формы сигнала, аналого-цифровой преобразователь, регистр, блок вычисления амплитуды, первый, второй решающие блоки, четыре управляемых ключа, причем входы аналого-цифрового преобразователя и анализатора формы сигнала являются входом устройства, синхровход анализатора формы сигнала соединен с выходом делителя фронтов и срезов, а выход— с управляющими входами управляемых ключей, выход аналого-цифрового преобра5 эователя соединен с первым входом регистра, входом блока вычисления амплитуды, с первым входами первого решающего блока и второго решающего блока, второй вход которого соединен с выходом регистра, а

10 третий вход — с выходом блока вычисления амплитуды, соединенным также с вторым входом первого решающего блока. первый выход второго фаэовращателя соединен с первым входом первого управляемого клю15 ча, второй вход и выход которого соединены соответственно с первым выходом второго решающего блока и входом первого формирователя импульсов, второй выход второго фазорасщепителя соединен с первым вхо20 дом второго управляемого ключа, второй вход и выход которого соединены соответственно с вторым выходом второго решающего блока и входом второго формирователя импульсов, выход выделителя фронтов сое25 динен с управляющими входами аналогоцифрового преобразователя и регистра, первый выход первого фазорасщепителя соединен с первым входом третьего управляемого ключа, второй вход которого и выход

30 соединены соответственно с первым выходом первого решающего блока и S-входом

RS-триггера, второй выход первого фаэорасщепителя соединен с первым входом четвертого управляемого ключа, второй

35 вход и выход которого соединены соответственно с вторым выходом первого решающего блока и R-входом Rs-триггера.