Цифровой частотно-фазовый дискриминатор

Иллюстрации

Показать всеРеферат

Использование: радиотехника, цифровые системы фазовой автоподстройки частот . Сущность изобретения: цифровой частотно-фазовый дискриминатор содержит счетчик 1, блок 4 привязки импульсов входного сигнала и счетчик импульсов, статический регистр 8, блок запрета 7, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8, 9. D-триггеры 10-15 и три элемента И-НЕ 17-19. В устройстве обеспечивается последовательная запись состояний выходов первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 8 и 9 соответственно в третий и четвертый D-триггеры 10 и 11, а затем запись состояний выходных разрядов счетчика 1 в статический регистр 6, что повышает стабильность работы. При этом обеспечивается выключение режима сравнения частот в непосредственной близости от момента равенства частот входного и опорного сигналов , что сокращает время перехода режима сравнения частот в режим сравнения фаз. 2 ил.

союз советских

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)5 Н 03 0 13/00

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) ву(ЩщяР,:;:

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4922319/09 (22) 28.03,91 (46) 07.07.93, Бюл. № 25 (71) Центральное конструкторское бюро

"Алмаз" (72) В.Г.Аристов (56) Авторское свидетельство СССР

¹ 1251289, кл. Н 03 0 13/00, 1985. (54) ЦИФРОВОЙ ЧАСТОТНО-ФАЗОВЫЙ

ДИСКРИМИНАТОР (57) Использование; радиотехника, цифровые системы фазовой автоподстройки частот. Сущность изобретения; цифровой частотно-фазовый дискриминатор содержит счетчик 1, блок 4 привязки импульсов входного сигнала и счетчик импульсов, стаИзобретение относится к радиотехнике, в частности к радиоавтоматике и импульсной технике. Изобретение может быть использовано в цифровых системах фазовой автоподстройки частоты, Целью изобретения является повышение стабильности и сокращение времени перехода из режима сравнения частот в режим сравнения фаз.

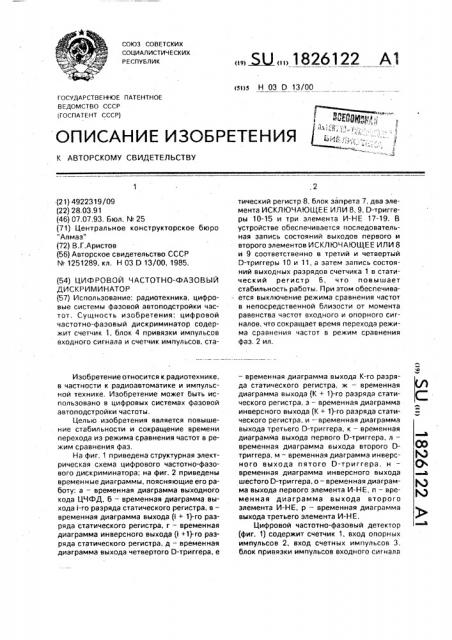

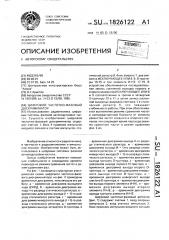

На фиг. 1 приведена структурная электрическая схема цифрового частотно-фазового дискриминатора; на фиг, 2 приведены временные диаграммы, поясняющие его работу: а — временная диаграмма выходного кода ЦЧФД, б — временная диаграмма выхода i-го разряда статического регистра, в— временная диаграмма выхода () + 1)-ro разряда статического регистра, г — временная диаграмма инверсного выхода (i +1)-го разряда статического регистра, д — временная диаграмма выхода четвертого О-триггера, е,, Ы„„1826122 А1 тический регистр 8, блок запрета 7, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8, 9, 0-триггеры 10-15 и три элемента И-НЕ 17-19. В устройстве обеспечивается последовательная запись состояний выходов первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 8 и 9 соответственно в третий и четвертый

D-триггеры 10 и 11, а затем запись состояний выходных разрядов счетчика 1 в статический регистр б, что повышает стабильность работы, При этом обеспечива- ется выключение режима сравнения частот в непосредственной близости от момента равенства частот входного и опорного сигналов, что сокращает время перехода режима сравнения частот в режим сравнения фаз, 2 ил. — временная диаграмма выхода К-ro разряда статического регистра, ж — временная диаграмма выхода (К + 1)-го разряда статического регистра, з — временная диаграмма инверсного выхода (К + 1)-го разряда статического регистра, и — временная диаграмма выхода третьего D-триггера, к — временная диаграмма выхода первого D-триггера, л— временная диаграмма выхода второго Dтриггера, м — временная диаграмма инверсного выхода пятого D-триггера, н— временная диаграмма инверсного выхода шестого D-триггера, о — временная диаграмма выхода первого элемента И-НЕ, и — временная диаграмма выхода второго элемента И-НЕ, р — временная диаграмма выхода третьего элемента И-НЕ.

Цифровой частотно-фазовый детектор (фиг. 1) содержит счетчик 1, вход опорных импульсов 2, вход счетных импульсов 3. блок привязки импульсов входного сигнала

1826122 к счетным импульсам (БП) 4, вход импульсов входного сигнала 5, статический регистр 6, блок запрета 7, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8, 9, шесть О-триггеров 10-15, элемент ИЛИ 16 и три элемента И-НЕ 17-19, Вход обнуления R и счетный вход T счетчика 1 являются соотве ственно входами опорных 2 и счетных 3 импульсов, Первый и второй входы БП 4 соединены соответственна со входом 5 цифрового частотно-фазового дискриминатора и входом 3 счетных импульсов, Первый выход БП 4 соединен с

С-входами третьего О-триггера 10 и четвертого О-триггера 11, Второй выход БП 4 соединен с С-входом записи информации 15 регистра 6, информационные входы которого соединены с соответствующими выходами счетчика 1, выходы К разрядов статического регистра 6 соединены с входами блока запрета 7, в выходы К-ro u i-ro 20 разрядов статического регистра 7 соединены с первыми входами соответственна первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 и второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 9.

Выход элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 8 25 и 9 соединены с О-входами соответственно третьего О-триггера 10 и четвертага О-триггера 11. Выход третьего О-триггера 10 соединены с О-входами первого О-триггера 12 и второго О-три гера 13, С-вход первого О- 30 триггера 12 соединен с выходам (К + 1)-го знакового разряда статического регистра 7.

Инверсный выход (К+ 1)-го знакового разряда статического регистра 7 соединен с вторым входом первого элемента 35

ИСКЛЮЧАЮЩЕЕ ИЛИ 8, с С-выходом второго О-триггера 13 и первым входом элемента ИЛИ 16. Выход четвертого О-триггера

11 соединен с О-входами пятого О-триггера

14 и шестого О-триггера 15, С-вход пятого 40

О-триггера 14 соединен с выходам (i + 1)-ro разряда статического регистра 7. Инверсный выход (i + 1)-ro разряда статического регистра 7 соединен с вторым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 9 и с 45

С-входом шестого О-триггера 15. Прямой выход первого О-триггера 12 соединен с первым входом первого элемента И-HE 17 и инверсным R-входом шестого О-триггера

15. Прямой выход второго О-триггера 13 са- 50 единен с вторым входам первого элемента

И-НЕ 17 и инверсным R-входам пятого О-. триггера 14. Выход первого элемента И-НЕ

17 соединен с инверсным 8-входам первого

О-триггера 12 и второго О-триггера 13, Ин- .55 версные выходы пятого О-триггера 14 и щестого О-триггера 15 соединены с инверсными 3-входами соответственно первого 0-триггера 12 и второго 0-триггера

13, Инверсные выходы первого О-триггера

12 и второго О-триггера 13 соединены соответственно с первым и вторым входами вто- . рого элемента И-НЕ 18, выход которого соединен с управляющим входом блока запрета 7 и вторым входом элемента ИЛИ 16.

Выход элемента ИЛИ t6 соединен с первым входом третьего элемента И-НЕ 19, второй вход третьего элемента И-НЕ 19 соединен с инверсным выходом второго О-триггера 13, Выход третьего элемента И-HF 19 является выходом знакового разряда цифрового частотно-фазового дискриминатора. Выход второго элемента И-НЕ 18 и выход блока запрета 7 являются выходами значащих разрядов цифрового частотно-фазового дискриминатора.

Предлагаемый цифровой частотно-фазовый дискриминатор работает следующим . образом.

Опорные импульсы, поступающие от входа 2 на вход R установки нуля счетчика 1, увеличивают "0" на его выходных разрядах.

На счетный вход Т счетчика 1 от входа 3 поступает непрерывная последовательностьсчетных импульсов, под воздействием которых изменяются состояния выходных разрядов счетчика 1. При этом частота счетных импульсов определяется выражением:

2 — 1 сч— где 2 -1 — емкость счетчика 1; к+1

Т вЂ” период опорных импульсов.

БП 4, на который поступает последовательность счетных импульсов обеспечивает выделение на первом выходе первого "цело- го" счетного импульса, а на втором выходе — второго "целого" счетного импульса, следующих за импульсом входного сигнала, поступающего по входу 5 цифрового частотно-фазового дискриминатора.

Следующие за импульсам входного сигнала первый "целый" счетный импульс осуществляет запись состояний выходов первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ.8 и второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ

9 соответственно в третий О-триггер 10 и четвертый D-триггер 11, а второй "целый" счетный импульс осуществляет запись состояний выходных разрядов счетчика 1 в статический регистр 6. На выходе этого регистра формируется двоичный код, величина N которого пропорциональная разности фаз входного и опорного импульсов.

В режиме синхрониэма, когда разность фаз импульсов входного и опорного сигнала переходит через л(что соответствует нулевому значению фазовой характеристики

ЦЧФД), происходит переключение выхода (К + 1)-го знакового разряда.статического

1826122

50 регистра 6 из "1" в "0" или из "0" в "1" в зависимости от направления изменения разности фаэ входного и опорного сигнала.

Одновременно осуществляется переключение К младших выходных разрядов статического регистра 6 соответственно иэ нулевых значений в единичные или из единичных в нулевые в зависимости от направления изменения разности фаэ импульсов входного и опорного сигналов. В этом случае в ре зультате состязания фронтов сигналов на входах первого элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ 8 появляется импульсная помеха единичного уровня. Однако последовательная запись сначала состояния выхода первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 в третий

0-триггер 10, а затем состояний выходных разрядов счетчика 1 в статический регистр

6, осуществляемая с помощью выходных импульсов Efl 4, поступающих эа импульсом входного сигнала, исключает воэможность включения первого D-триггера 12 или второго 0-триггера 13 от импульсной помехи единичного уровня.

Если частота импульсов входного сигнала, поступающих по входу 5 больше частоты опорных импульсов, поступающих по входу

2 (1вх > оп), то разность фаз этих сигналов убывает от цикла к циклу е направлении от

2 л до О, одновременно убывает и величина двоичного кода N на выходе цифрового частотно-фазового дискриминатора (фиг. 2э).

Когда разность фаз входного и опорного сигналов достигает е момент времени т1 значения Оо, а величина двоичного кода на выходе ЦЧ ФД вЂ” значения Моор.макс и роисходит скачкообразное изменение разности фаэ входных сигналов от 0 до 2 л . Одновременно происходит переключение (К+1)ro знакового разряда статического регистра

6 из "0" в "1" (фиг. 2ж), с помощью которого осуществляется запись "1" с выхода третьего 0-триггера 10 (фиг. 2и) в первый 0-триггер 12.

Временная диаграмма третьего 0-триггера 10 (фиг. 2и) формируется с помощью элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8, íà входы которого поступают сигналы с выхода

К-го (фиг. 2е) и инверсного выхода (К+1)-ro (фиг. 2з) разрядов статического регистра 6.

На прямом выходе Д-триггера 12 появляется "1" (фиг. 2к), а на инверсном — "0", что вызывает появление "1" на выходе второго элемента И-НЕ 18 (фиг 2п), т.е. в старшем значащем разряде выходного кода ЦЧФД.

Эта "1" отключит младшие значащие разряды выходного кода ЦЧФД, поступающего через блок запрета 7, и удержит "1" на выходе элемента ИЛИ 16. На выходе третьего элемента И-НЕ 19. т.е, в знаковом разряде выходного кода ЦЧ ФД установится "0" (фиг.

2р). ЦЧФД перешел в режим сравнения частот со знаком "0".

В режиме сравнения частот "1" с прямого выхода первого 0-триггера 12, поступая на инверсный R-вход шестого D-триггера

15, снимает его обнуление. При уменьшении частотной расстройки уменьшается скорость изменения разности фаз входного и опорного сигналов и в момент времени т2 частоты входного и опорного сигналов становятся равными по величине, скорость изменения разности фаз равна нулю, после чего меняется знак разности частот и начинает возрастать от цикла к циклу разность фаэ входного и опорного сигналов в направлении от 0 до 2 л, В момент времени t2 происходит скачкообразный сдвиг фазы на л сигнала на выходе четвертого 0-триггера

11 (фиг, 2д) относительно сигнала с инверсного выхода (!+1)-го разряда (фиг. 2г) статического регистра 6, которые поступают соответственно на 0- и С-входы шестого

0-триггера 15. Временная диаграмма выхода четвертого 0-триггера 11 (фиг. 2д) формируется с помощью элемента

ИСКЛЮЧАЮЩЕЕ ИЛИ 9, на выходы которого поступают сигналы с выхода i-го (фиг. 2б) и инверсного выхода (i+1)-го (фиг. 2г) разрядов статического регистра 6. В момент времени тз происходит переключение инверсного выхода (i+1)-го разряда статического регистра 6 из "0" в "1" {фиг. 2г), с помощью которого осуществляется запись

"1" с выхода четвертого D-триггера 11 (фиг.

2д) в шестой D-триггер 15. Нулевой импульс с инверсного выхода шестого 0-триггера 15 (фиг. 2н), воздействуя на инверсный S-вход второго D-триггера 13, устанавливает на его выходе "1" (фиг, 2л). Единичные уровни на выходах первого элемента И-Н Е 17, вызы вают появление импульса нулевого уровня на его выходе, с помощью которого осуществляется выключение сначала D-триггеров 12 и 13, а затем шестого 0-триггера 15, На выходе второго элемента И-НЕ 18 (фиг, 2п) появляется "0", а на выходе третьего элемента И-НЕ 19 (фиг. 2р) — "1". Происходит выключение режима сравнения частот.

ЦЧФД переходит в режим сравнения фаз и устанавливает режим синхронизма.

В режиме сравнения частот на интервале (t>...тз) многократно осуществляется переключение 1 младших выходных разрядов статического регистра 6 из нулевых значений е единичные или из единичных е нулевые в зависимости от направления изменения разности фаз импульсов еходно5

15

55 го и опорного сигналов. В этом случае в результате состязания фронтОВ сфндлов на входах второго элемента ИСКЛ ЮЧАЮЩЕ Е

ИЛИ 9 появляется импульсная помеха единичного уровня, которая может вызвать ложный переход иэ режима сравнения частот в режим сравнения фаз. Однако последовательная запись сначала состояния выхода второго элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ 9 в четвертый 0-триггер 11, а затем состОЯний Выходных разрЯдов счетчика 1 В статический регистр 6, осуществляемая с помощью выходных импульсов БП 4, поступающих за импульсом входного сигнала. включает возможность включения от импульсной помехи единичного уровня шестого D-триггера 15 или пятого 0-триггера 14 в зависимости от направления изменения разности фаэ входных сигналов.

Аналогично происходит работа ЦЧФД, когда частота входных импульсов меньше опорных (f»< < f0<). Только в этом случае разность фаз входных сигналов сначала увеличивается от цикла к циклу в направлении от 0 до 2 л и переход в режим сравнения частот осуществляется после включения второго 0-триггера 13, а переход в режим сравнения фаз происходит после изменения знака разности частот, когда начинает уменьшаться от цикла к циклу разность фаз входных и опорных сигналов в направлении оТ 2 x po О. В 3ToM voveHT происходит скачкообразный сдвигфаэы на лсигнала на выходе четвертого 0-триггера 11 относительно сигнала с выхода (i+1)-ro разряда статического регистра 6, которые поступают соответственно на 0- и С-входы пятого 0триггера 14, Временные диаграммы выхода четвертого 0-триггера 11 и выхода (i+1)-m разряда статического регистра б соответствуют диаграммам, приведенным на фиг. 2д и фиг, 2в на интервале (11.. tz). Вкл очается пятый Dтриггер 14 и нулевой импульс с его инверсного выхода, воздействуя иа инверсный

S-вход первого 0-триггера 12, устанавливает на его выходе " 1", Единичные уровни на входах перво, о элемента И-НЕ 17 вызывают появление импульса нулевого уровня на его выходе, с помощью которого осуществляется выключение сначала D-триггеров 12 и 13, а затем пятого 0-триггера 14, Г роисходит выключение режима сравнения частот.

ЦЧФД переходит в режим сравнения фаз, Выключение режима сравнения частот в предлагаемом дискриминаторе осуществляется в непосредственной близости от момента равенс"aa частот входного и

ОПОриого сигналоВ, что приводит !< значительному сокращению времени перехода из режима сравнения частот в режим сравнения фаз.

Значение i должно находится в пределах 1 < i < К-1, причем уменьшение благоприятно сказывается на сокращении времени перехода из режима сравнения частот в режиме сравнения фаз.

Использование изобретения позволит по сравнению с известным уменьшить длительность и амплитуду выброса фазовой ошибки и, следовательно, увеличить быстродействие систем частотно-фазовой автоподстройки частоты.

ПО данному техническому предложению изготовлен макет цифрового частотнофазового дискриминатора, Были проведены его испытания. Результаты испытаний положительныеые, Формула изобретения

Цифровой частотно-фазовый дискриминатОр, содержащий последовательно соединенные счетчик, вход и выход сброса которого являются соответственно входом счетных импульсов и входом опорных импульсов, статический регистр и блок запрета, первый и второй D-триггеры, D-входы которых объединены, С-входы подключены соответственно к прямому и инверсному выходам (К+1)-го знакового разряда статического регистра, первый элемент И-НЕ, входы которого подключены к прямым выходам первого и второго D-триггеров. а выход — к инверсным R-входам первого и второго

О-триггеров, второй элемент И-НЕ, вход которого подключены к инверсным выходам первого и второго 0-триггеров, последовательно соединенные элемент ИЛИ, входы которого подключены к инверсному выходу (К+1)-го знакового разряда статического регистра и выходу второго элемента И-НЕ, и третий элемент И-НЕ, другой вход которого подключен к инверсному выходу второго 0триггера, а также первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, один вход которого и вход управления блока запреты подключены к инверсному выходу (К+1)-го знакового разряда статического регистра, выход блока запрета и выход второго элемента И-НЕ являются выходами значащих разрядов цифрового частотно-фазового дискриминатора, а выход третьего элемента И-НŠ— его выходом знакового разряда, отличающийся тем, что, с целью повышения стабильности и сокращения времени перехода иэ режима сравнения частот в режиме сравнения фаз, в него введены третий D-триггер, включенный между выходом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, другой вход которого подключен к выходу К-го разряда статического регист1826122

10 ра, и объединенными Р-входами первого и второго О-триггеров, последовательно соединенные второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, входы которого подключены к выходу I-ro, где (1 < i < K -1) и инверсному выходу (i + 1)-го разрядов статического регистра, и четвертый О-триггер, пятый и шестой

О-триггеры, 0-входы которых подключены к прямому выходу четвертого 0-триггера, Свходы — к прямому и инверсному выходам (i

+ 1)-го разряда статического регистра, инверсные R-входы — к прямому и выходам первого и второго D-триггеров, инверсные выходы пятого и шестого D-триггеров подключены к инверсным S-axopa первого и второго 0-триггеров соответственно, а также

5 блок привязки импульсов входного сигнала к счетным импульсам, один вход которого подключен к входу счетных импульсов, другой является входом цифрового частотно-фазового дискриминатора, первый выход подключен

10 к С-входам третьего и четвертого D-триггеров, а второй выход — к входу разрешения записи статического регистра.

1826122

Составитель В.Аристов

Техред M.Моргентал Корректор Л.Ливринц

Редактор

Заказ 2322 Тираж Подписное

ВНИИПИ ГосУдарственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35 Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул,Гагарина, 101