Генератор псевдослучайных последовательностей

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использовано в радиотехнике и вычислительной технике Сущность изобретения устройство содержит генератор тактовых импульсов, элемент И, две схемы сравнения, два счетчика импульсов , два блока памяти, сумматор, вход управления , вход задания длины последовательности выход с соответствующими связями 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)з Н 03 К 3/84

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) ОПИСАНИЕ ИЗОБРЕТЕНИЯ (21) 4908128/21 (22) 04.02.91 (46) 07,07.93. Бюл. М 25

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (72) В,И,Петренко и А.Ф.Чипига (56) Авторское свидетельство СССР

Ф 1347165, кл. Н 03 К 3/84, 1985. (54) ГEHEPATOP ПСЕВДОСЛУЧАЙНЫХ ПОСЛ ЕДОВАТЕЛ Ь Н ОСТЕ Й

Изобретение относится к импульсной технике и может быть использовано в радиотехнике и вычислительной технике.

Цель изобретения — расширение функциональных возможностей.

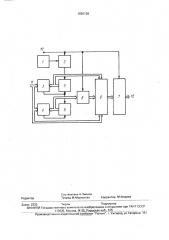

На чертеже представлена функциональная схема генератора псевдослучайных последовательностей.

Генератор содержит генератор 1 тактовых импульсов, элемент И 2, первую 3 и вторую 4 схемы сравнения, первый 5 и второй 6 счетчики, первый 7 и второй 8 блоки .,памяти, сумматор 9 по модулю, вход 10 управления генератором, вход 11 задания длины последовательности генератора и выход

12 генератора.

Генератор псевдослучайных последовательностей работает следующим образом.

В исходном состоянии счетчики 5 и 6 обнулены. Начало работы генератора определяется моментом подачи на его вход 10 управления единичного потенциала, который удерживается в течение всего времени работы генератора. В блоке 7 памяти (при организации N х К) хранится N К разрядных слов, что обеспечивает возможность генерации К различных ПСП с их циклической перестройкой. При этом s блоке 7 памяти

„„5U „„18261 28 А1

{57) Изобретение относится к импульсной технике и может быть использовано в рэдиотехнике и вычислительной технике. Сущность изобретения: устройство содержит генератор тактовых импульсов, элемент И, две схемы сравнения, два счетчика импульсов, два блока памяти, сумматор, вход управления, вход задания длины последовательности, выход с соответствующими связями. 1 ил. хранятся только базовые {опорные) ПСП, Для одной базовой ПСП в каждом слове (ячейке) отведен один разряд, т.е. ее элементы хранятся в N смежных ячейках с адресами с нулевого по N-1. Чтение числа из блока

7 памяти разрешается единичным потенциалом, поступающим на его вход разрешения чтения со входа 10 управления генератора. В блоке 8 памяти хранятся значения начальных адресов {при организации

N x flog N), определяющих величину циклической сдвижки формируемых ПСП для каждого цикла формирования ПСП.

Тактовые импульсы с выхода генератора 1 тактовых импульсов через открытый элемент И 2 поступают на счетный вход счетчика 5, который осуществляет их последовательное суммирование. . Длительность N кодов последовательностей задается двоичным кодом, подаваемым на вход 11 генератора, При этом модуль пересчета счетчиков 5 и 6 будет определяться величиной N. Счетчик 6 подсчитывает импульсы, которыми обнуляется счетчик 5 с выхода схемы 3 сравнения. Обнуление счетчика 6 осуществляется импульсом с выхода схемы сравнения 4. Коды чисел с выхода счетчика 5 и блока 8 памяти суммируются

1826128 сумматором 9 по модулю. Результат суммирования поступает на адресный вход блока

7 памяти, который и формирует ПСП.

Третий вход сумматора 9 является входом задания модуля, по которому осуществляется суммирование чисел, поступающих на первый и второй входы сумматора 9. Суммирование по модулю исключает возможность подачи на вход блока 7 памяти несуществующих адресов, т,е. если, например, генерируются последовательности, записанные в блоке 7 памяти с О по 999 адрес, то на третий вход сумматора 9 по модулю необходимо подавать двоичный код чисел

1000, а на выходе сумматора 9 будут образовываться числа от О до 999. Информация с 1000 и тд, адресов блока 7 памяти считываться не будет, что исключает искажения формируемых последовательностей.

В результате, в течение каждых N тактов работы генератора на l-и цикле формирования ПСП на выходе сумматора 9 по модулю образуются последовательности чисел; (j,j+ 1, j+ 2,.„,! + К вЂ” 1) mad N, где j — число, записанное по i-му адресу в блоке 8 памяти.

Итак, в течение одного цикла работы за

N тактов на выходе 12 генератора будут сформированы и элементов всех К ПСП, записанные в блоке 8 памяти, а в каждом последующем цикле формируются последовательности, образованные из базовых последовательностей с циклическим сдвигом ча," элементов. Записывая в блок 8 памяти произвольные j, noëó÷èì в каждом цикле ПСП cQ случайными (определяемыми величиной )) циклическими сдвижками, Формула изобретения

Генератор псевдослучайных последовательностей, содержащий генератор тактовых импульсов, первый и второй счетчики импульсов, первый и второй блоки памяти, сумматор, информационные выходы которого подключены к адресным входам первого блока памяти, первая группа

5 информационных входов — к информационным выходам первого счетчика импульсов, а вторая группа информационных входов — к информационным выходам второго блока памяти, адресные входы которого подклю"0 чены к информационным выходам второго счетчика импульсов, содержащий также выходную шину, отличающийся тем, что, с целью расширения функциональных возможностей за счет формирования широкого

15 спектра псевдослучайных последовательностей, в него введены первая и вторая схемы сравнения, элемент И, информационная кодовая шина, управляющая шина, подключенная к управляющим входам первого и второго блоков памяти и первому входу элемента И, второй вход которого подключен к выходу генератора тактовых импульсов, а выход — к счетному входу первого счетчика импульсов, информационные выходы которого подключены к первой группе информационных входов первой схемы сравнения, выход которого подключен к входу установки в"0" первого счетчика импульсов и счетному входу второго счетчика импульсов, М информационные выходы которого подключены к первой группе информационных входов второй схемы сравнения, выход которого подключен к входу установки в "0" второго счетчика импульсов, причем инфорЗ5 мационная кодовая шина подключена к вторым группам информационных входов первой и второй схем сравнения и к третьей группе информационных входов сумматора, а информационные выходы первого блока памяти подключены к выходной шине, выполненной кодовой

1826128

Составитель А.Чипига

Техред М.Моргентал Корректор M.Kåøåëÿ

Редактор

Заказ 2322 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Мсскаа, Ж-35 Ра3искаа наб.. 4/5

Производственно-издательский комбинат "Патент". r, Ужгород, ул.Гагарина, 101