Устройство фазовой автоподстройки частоты

Иллюстрации

Показать всеРеферат

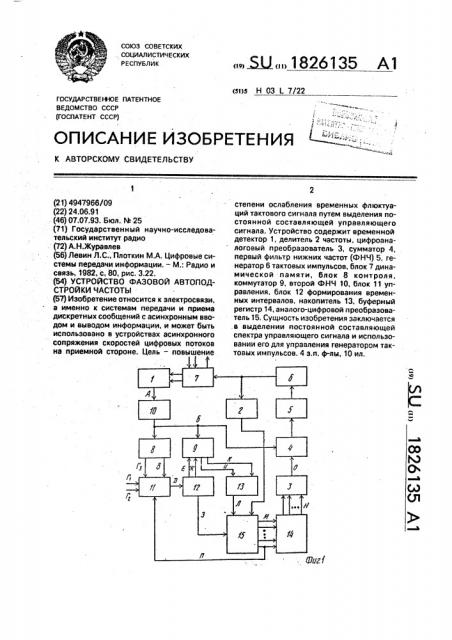

Изобретение относится к электросвязи, а именно к системам передачи и приема дискретных сообщений с асинхронным вводом и выводом информации, и может быть использовано в устройствах асинхронного сопряжения скоростей цифровых потоков на приемной стороне. Цель - повышение U fстепени ослабления временных флюктуации тактового сигнала путем выделения постоянной составляющей управляющего сигнала. Устройство содержит временной детектор 1, делитель 2 частоты, цифроаналоговый преобразователь 3, сумматор 4, первый фильтр нижних частот (ФНЧ) 5, генератор 6 тактовых импульсов, блок 7 динамической памяти, блок 8 контроля, коммутатор 9, второй ФНЧ 10, блок 11 управления , блок 12 формирования временных интервалов, накопитель 13, буферный регистр 14, аналого-цифровой преобразователь 15. Сущность изобретения заключается в выделении постоянной составляющей спектра управляющего сигнала и использовании его для управления генератором тактовых импульсов. 4 з.п. ф-лы, 10 ил. 00 ю о со ел Фиг. f

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) (э1)э Н 03 L 7(22

ГОСУДАРСТВЕН.К)Е ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЪСТВУ (21) 4947966/09 (22) 24,06.91 (46) 07.07.93. Бюл.. М 25 (71) Государственный научно-исследовательский институт радио (72) А.Н.Журавлев (56) Левин Л.С.. Плоткин M.À. Цифровые системы передачи информации. — M.: Радио и связь, 1982, с, 80, рис. 3.22. (54) УСТРОЙСТВО ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЪ (57) Изобретение относится к электросвязи, а именно к системам передачи и приема дискретных сообщений с асинхронным вводом и выводом информации, и может быть использовано в устройствах асинхронного сопряжения скоростей цифровых потоков на приемной стороне. Цель — повышение степени ослабления временных флюктуаций тактового сигнала путем выделения постоянной составляющей управляющего сигнала. Устройство содержит временной детектор 1, делитель 2 частоты, цифроаналоговый преобразователь 3, сумматор 4, первый фильтр нижних частот (ФНЧ) 5, генератор 6 тактовых импульсов, блок 7 динамической г)амяти, блок 8 контроля, коммутатор 9, второй ФНЧ 10, блок 11 управления, блок 12 формирования временных интервалов, накопитель 13, буферный регистр 14, аналого-цифровой п реобразователь 15. Сущность изобретения заключается .в выделении постоянной составляющей спектра управляющего сигнала и использовании его для управления генератором тактовых импульсов. 4 з.п. ф-лы, 10 ил.

1826135

Изобретение относится к электросвязи, а именно к системам пеаедачи и приема дискретных сообщений с асинхронным вводам и выводам информации, и может быть использована в устройствах асинхронного сопряжения скоростей цифровых потоков на приемной GTopoHG.

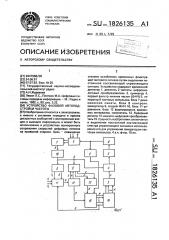

Цель изобретения — повышение степени ослабления временных флюктуаций такToâoã0 сигнала путем выделения постоянной составляющей спектра управляющего сигнала, На фиг, 1 приведена структурная электрическая схема предлагаемого устройства фазавой автападстрайки частоты; на фиг. 2 — структурная электрическая схема блока контроля; на фиг. 3 — блок управления; на фиг. 4 — блок формирования временных интервалов; на фиг. 5 — накопители; на фиг. 6 — блок динамической памяти; на фиг. 7— временные диаграммы рабаты устройства фазовой автападстрайки частоты в режиме поиска; на фиг. 8 — временные диаграммы работы блока контроля в режиме поиска; на фиг, 9 — временные диаграммы работы устройства фазавай автападстрайки в режиме захвата и установившемся режиме; на фиг.

10 — временные диаграммы работы блока контроля и режиме захвата и установившемся режиме.

Устройство фазовай автападстрайки частоты содержит временной детектор 1, делитель 2 частоты, цифроаналоговый преобразователь (ЦАП) 3, сумматор 4, первый фильтр нижних частот (ФНЧ) 5,генератор 6 тактовых импульсов, блок 7 динамической памяти, блок 8к,онтроля,,коммутатор 9, второй ФНЧ 10, блок 11 управления, блок 12 формирования временных интервалов, накопитель 13, буферный регистр 14, аналога-цифровой преобразователь (АЦП) 15, блок 8 контроля содержит первый, "».торой и третий кампараторы 1618, первый, второй и третий источники 19-21 опорного напряжения, первую и вторую дифференцирующие цепи 22, 23, выпрямитель 24, элемент ИЛИ 25, элемент запрета

26, блок 11 управления содержит элемент

ИЛИ 27, коммутатор 28, RS-триггер 29, блок

12 формирования гременных интервалов содержит первь1й, второй, третий и четвертый ждущие мультивибратары 30 :3. Накопитель 13 содержит первь1й .„ второй повторители 34, 35 напряжения, резисторы

36-38, конденсатор 39, резистор 40, конденсатор 41, блок 7 динамической памяти содержит распределитель записи 42, распределитель считывания 43, ячейки памяти 44,1-44.L, каждая иэ которых содержит элемент И 45, элемент памяти 46, элемент

ИЛИ 47. . Устройство фазовай автопадстройки частоты работает следующим образом.

5 Сигнал пилообразной формы с размахом Uo с входа блока 8 поступает на прямой вход первого компаратора 16 (фиг, 8,Б) на инверсном его входе установлено опорное напряжение Uo«, значение которого опре10 деляется одним из условий:

Озмакс > Ооп1 > Ормакс или Озмин< Uo» <

< Ормин, где Озмакс и Озмин максимальное и минимальное значения входного сигнала, отвечающие границам полосы захвата устройства;

UpìÂêñ и Ормин максимальное и минимальное значения входного сигнала в установившемся режиме..

Рассмотрим работу блока 8 контроля

20 при Uo», установленном по второму условию. При установке Uo» по первому условию, блок 8 работает аналогичным образом.

На выходе компаратора 16 формируются импульсы прямоугольной формы (фиг. 8)

25 (Б1), которые дифференцируются цепью 23 и поступают на вход выпрямителя 24. Выпрямитель 24 импульсы положительной полярности пропускает неизменными, а отрицательной полярности - преобразует в

30 импульсы положительной полярности (фиг.

8 БЗ), Импульсы с выхода выпрямителя поступают на первый вход элемента ЗАПРЕТ

26..

Входной сигнал дифференцируется с помощью дифференцирующей цепи 22 и поступает на прямой вход второго и инверсный вход третьего компараторов 17, 18. На другие входы которых поступают опорные напряжения Ооп2, Оопз (фиг. 8 Б4).

На выходе третьего компаратора 18 формируются прямоугольные импульсы (фиг, 8 Бб) и через элемент ИЛИ 25 поступают на второй вход элемента ЗАПРЕТ 26 и на второй выход блока 8 — сигнал аварии (фиг, 45 8 В). На выход элемента ЗАПРЕТ 26 проходяттолькоте импульсы, поступающие на его первый вход, которые не совпадают с импульсами на втором входе(фиг. 8 ГЗ = сигнал захвата).

Работа блока 8 контроля при наличии на входе пилообразного сигнала со спадающей пологой частью показана на фиг. 8 пун. ктирными линиями. Из временных диаграмм видно, что работа блока не отли55 чается от описанной выше.

При смене на входе блока сигнала пилообразной формы с размахом Оп на сигнал пилообразной формы с размахом Оу прекращается формирования импульсов во всех характерных точках (фиг. 10). На выходе пер1826135

15

RS-триггера 29, который устанавливается в 25 ваго кампаратора 16 устанавливается потенциал лаг "1" (фиг. 10 В1), а на выход первой дифференцирующей цепи проходят импульсы с амплитудами не достигающими пороговых значений (фиг. 10 Б4) Работа блока 8 при наличии на входе пилообразного сигнала размахом Uy со спадающей пологой частью показана на фиг. 10 пунктирными линиями. Из временных диаграмм видно, что отличие состоит только в количестве импульсов. формируемых блокам после смены сигнала на входе блока, что не имеет существенного значения для работы устройства.

Блок 11 управления предназначен для формирования управляющих импульсов и работает следующим образом.

На вход положительного стаффинга, вход отрицательного стаффинга и вход запрета блока 11 поступают импульсы положительного стаффинга, отрицательного стаффинга и сигнала захвата, соответственна. Названные импульсы объединяются элементом ИЛИ 27 и поступают на R-вход состояние лаг "0", открывая коммутатор 28 по второму входу и закрывая па первому и шестому входам. При этом на выход блока

11 проходят импульсы с его входов положительного и отрицательного стаффинга и входа запрета.

Импульсы сигнала аварии, поступающие на информационный вход блока 11, устанавливают RS-триггер 29 в состояние лог.

"1", открывая коммутатор 28 по первому и шестому входам и закрывая его по второму входу. При этом на выход блока 11 проходят импульсы с его импульсного и управляющего входов, Блок 12 формирования временных интервалов предназначен для формирования импульсов заданной длительности и с заданными временными сдвигами и работает следующим образом.

Первый ждущий мультивибратор 30 запускается положительным фронтом импульса, поступившего на вход блока 12 и формирует импульс заданной длительности, Задним фронтом этого импульса запускается второй ждущий мультивибратор 31 и формирует импульс, задним фронтом которого запускается третий ждущий мультивибратор 32. Этот мультивибратор формирует импульс равный по длительности импульсу формируемому первым ждущим мультивибратором 30, а временный сдвиг между ними определяется длительностью импульса, формируемому вторым ждущим мультивибратором 31. Четвертый ждущий мультивибратар 33 запускается за30

55 дним фронтом импульса сформированного третьим ждущим мультивибратарам 32 и формирует импульс. Таким образом, в ответ на каждый входной импульс блок 12 формирует на своих выходах по одному импульсу определенной длительности и с определенными временными сдвигами.

Накопитель 13 предназначен для накопления зарядов, поступающих на ега входы и формирования управляющего сигнала и работает следующим образом.

На входы накопителя 13 поступают импульсы заданной длительности, с переменной амплитудой и с заданным временным сдвигам. Пад действием упомянутых импульсов заряжаются конденсаторы 39 и 41 накопительных RS-цепей R38, С39 и R40, С41. Постоянная времени накопительных

RS-цепей выбрана так, чтобы за время входного импульса. соответствующий конденсатор успел зарядиться до амплитудного значения импульса. Напряжения с конденсаторов 39, 41 через соответствующие повторители напряжений 34, 35 поступают на делитель напряжения состоящий из резисторов 36 и 37. На выходе делителя формируется потенциал равный среднему арифметическому значению напряжений, поступающих на его входы.

Блок 7 динамической памяти предназначен для переноса информационного сигнала с тактовой частоты записи f3 на тактовую частоту считывания 1 путем исключения из него в процессе записи и считывания имеющихся в нем вставок (положительных или отрицательных) и синхросигнала и работает следующим образом.

На вход распределителя 42 записи поступают последовательность тактовых импульсов записи f3. Эта последовательность содержит только импульсы, совпадающие по времени с теми символами цифрового сигнала, которые необходимо перенести на частоту считывания fc . а импульсы, совпадающие с исключаемыми символами цифрового сигнала (например, с символами синхросигнала), из тактовой последовательности исключены, т.е. образуется пауза, В любом тактовом интервале формируется импульс только на одном из выходов распределителя 42. В следующем тактовом интервале импульс формируется на следующем выходе и т.д. до последнего выхода. В следующем тактовом интервале импульс формируется на первом выходе и этот процесс повторяется. Во время паузы в последовательности входных тактовых импульсов импульс, сформированный на одном иэ выходов, на следующий выход не продвигает1826135 ся, дальнейшее продвижение импульса по выходам начинается по окончании паузы.

Аналогичным образом работает распределитель 43 считывания, Отличие состоит только в том, что на его вход тактовые импульсы поступают непрерывно, т,е. без пауз.

Импульсы, формируемые распределителем 42 записи, используются для управления процессом записи цифрового сигнала в ячейки памяти, который поступает на первые (информационные) входы элементов 46 памяти всех ячеек 4 памяти. Запись символов цифрового сигнала в ячейки 44 памяти осуществляется в том же порядке, как и формирование импульсов на выходах распределителя 42 записи. Символы, совпадающие с паузами в тактовой последовательности записи, в ячейки памяти не записываются.

С выхода элемента памяти 46 символ цифрового сигнала поступает на первый вход элемента И 45, при поступлении на второй вход которого импульса считывания названный символ проходит на его выход, т.е. на выход соответствующей ячейки 44 памяти. Считывание символов цифрового сигнала из ячеек 44 памяти осуществляется в том же порядке, как и формирование импульсов на выходах распределителя 43 считывания. Считываемые символы цифрового сигнала обьединяются с помощью элемента

ИЛИ 47 и поступают на выход блока 7 динамической памяти.

Коммутатор 9 предназначен для подключения входного аналогового сигнала к первому или второму выходам и работает следующим образом, В коммутаторе 9 первый вход является сигнальным, второй и третий входы — управляющими входами, а первый и второй выходы — сигнальными выходами. Поддействием управляющего сигнала, поступающего на второй вход, коммутатор 9 подключает входной сигнал к первому выходу, а под действием управляющего сигнала, поступающего на третий вход — к второму выходу.

Временной детектор 1 предназначен для формирования импульсов, равных по длительности временному сдвигу между входными импульсами, и работает следующим образом, Импульсом, поступающим на З-вход, триггер устанавливается в состояние лог.

"1", а — поступающий íà R-вход-в состояние лог, "0". Отсюда ясно, что на выходе триггера формируются импульсы с длительнрстью, равной временному сдвигу входных импульсов.

Буферный регистр 14 предназначен для хранения числа от одного управляющего

40 зуется пауза, Описанная последователь45

5

35 сигнала до следующего и работает следующим образом.

С помощью импульса, поступающего на (m + 1)-й вход регистра 14 осуществляется запись числа присутствующего на его mвходах, Записанное число хранится в регистре до следующего импульса на (m + 1)-м входе, в который записывается следующее число и хранится до следующего импульса и т.д. Отсюда ясно, что на выходах регистра

14 число меняет свое значение только в моменты записи.

Делитель 2 частоты предназначен для деления тактовой частоты считывания до значения допустимого для АЦП 15. Делитель 2 частоты представляет собой разрядныхделитель частоты, где и определяется иэ

УСЛОВИЯ 2" сч/тмаксАЦП, ГДЕ fMBKc ДЦП— максимальная тактовая частота АЦП. Делитель 2 частоты осуществляет деление входной тактовой частоты (1сч) на 2", Устройства фазовой автоподстройки частоты работает при номинальных значениях тактовых частот записи и считывания опре-. деляемых выражением fý.ном = тсчном +

+fcn.ном, где fan.H0M. — номинальное значение частоты следования служебных импульсов (например, синхросигнала, вставок и пр.).

Причем последовательность тактовых импульсов:содержит только импульсы, совпадающие по времени с теми символами цифрового сигнала, которые необходимо перенести на частоту считывания (например, с информационными символами), а им-. пульсы совпадающие с исключаемыми символами цифрового сигнала (например, символами синхросигнала, вставок и пр„ т.е. служебными символами), из тактовой последовательности исключены, т.е. обраность тактовых импульсов поступает на второй вход блока 7 динамической памяти, на первый вход которой поступает непрерывная последовательность тактовых имПУЛЬСОВ СЧИтЫВаНИЯ С ЧаСтатай тсч, Т.К. fg >

>f,T0 временной интервал между моментами записи и считывания изменяется после каждого считывания на Ь1 = Т -Тсч, где Тз =

=1/fý, Тсч =.1/ f„— на эту же величину изменяется временной сдвиг между импульсами на втором и третьем выходах блока 7.

Рассмотрим работу устройства с момента включения, т.е. с режима поиска синхрониэма.

В этом режиме временной интервал между моментами записи и считывания изменяется па линейному закону в пределах от 0 до О сч, где L — количество ячеек памяти в блоке 7 динамической памяти. 8 тех же

1826135

40

50 пределах изменяется длительность импульсов на выходе временного детектора 1, а усредненное значение напряжения изменяется от 0 до амплитудного значения этих импульсов UHM0 где UHMfl амплитуда импульсов на выходе временного детектора 1, спадает до нуля и снова нарастает и т.д„т.е, изменяется по пилообразному закону. с периодом L/ 1з 1сч (фиг. 7.А) напряжение на выходе второго ФНЧ 10 изменяется также по пилообразному закону с тем же периодом и размахом U = U (фиг, 7.Б) и поступает на входы блока 8 контроля коммутатора 9. Блок 8 контроля формирует сигналы аварии (фиг, 7B) и захвата (фиг. 7ГЗ).

На фиг. 7 ГЗ сигнал захвата не показан с той целью, чтобы продемонстрировать режим поиска в полном объеме, а режим прерывания поиска и переход в режим захвата показан на фиг. 7Д, Сформированные блоком 11 управления управляющие импульсы (фиг. 7 Д) поступают на вход блока 12 формирования временных интервалов, который формирует управляющие импульсы для управления работой коммутатора 9 (фиг. 7 Е,Ж) и АЦП 15 (фиг. 7В). При наличии импульса (фиг. 7Е) коммутатор 9 передает входной сигнал на первый выход {фиг. 7И), а при наличии импульса (фиг. 7Ж) — на второй выход (фиг. 7К), В остальное время коммутатор 9 закрыт.

Накопитель 13 формирует сигнал, равный по уровню среднему арифметическому (фиг.

7Л) амплитуд импульсов (фиг. 7И,К). Сигнал (фиг. 7Л) поступает на второй вход АЦП 15, который под действием тактового сигнала, поступающего с делителя 2 частоты на третий вход, и управляющих импульсов (фиг.

73), поступающих на первый вход, преобразует сигнал (фиг. 7Л) в цифровую форму (m-разрядное число M). По окончании преобразования на (m + 1)-й выходе АЦП 15 формируется импульс "Конец преобразования" (фиг. 7П), которым число записывается в буферный регистр 14 (фиг. 7Н), и поступает на вход ЦАП 3, ЦАП 3 преобразует число в аналоговый сигнал (фиг. 7 0). Полученный сигнал поступает на второй вход сумматора

4, а на первый вход его поступает управляющий сигнал с выхода второго ФНЧ 10, Коэффициент суммирования по первому входу значительно меньше, чем по второму (К1 «К2 =1), и выбирается таким, чтобы при наличии на первом входе сигнала с размаxoM Uy на выходе управляющий сигнал изменялся на величину одного уровня квантования hU. Полученный сигнал с выхода сумматора 11 через первый ФНЧ5 поступает на вход генератора 6 тактовых импульсов, состоя5

25 щего из последовательно соединенных усилителя постоянного тока, управляемого синусоида IbMolo генератора и компаратора.

Синусоидальный сигнал с выхода управляемого генератора поступает на вход компаратора, который формирует прямоугольные импульсы той же частоты (f ) — тактовые импульсы. Под действием управляющего сигнала генератор 6 тактовых импульсов перестраивается в сторону уменьшения расстройки, Импульс "Конец преобразования" (фиг.

7П) через блок 11 управления поступает на вход блока 12 формирования временных.интервалов и запускает его. С этого момента начинается следующий цикл работы блоков: блока 12 формирования временных интервалов, коммутатора 9, накопителя 13, АЦП

15 и блока 11 управления, т.е. замыкается кольцо поиска (импульсы П,Д,З). Длительность цикла в кольце поиска — период поиска Тп — определяется временем задержки импульса (фиг. 73) по отношению к импульсу (фиг. 7Д) ЛТф и временем преобразования в аналого-цифровом преобразователе

ЛТдцп, Тп = Жф + Л ТАцп Причем Тп< Тсч

« Т,, где Т, — период согласования частот (период следования вставок). При этом обеспечивается быстрая перестройка генератора тактовых импульсов — уменьшается время поиска.

Режим захвата. При поступлении на вход положительного стаффинга и вход отрицательного стаффинга блока 11 управления импульса положительного или отрицательного стаффингэ (фиг. 9. Г1, Г2) соответственно, или на вход запрета импульса захвата (фиг. 9 ГЗ) блок t1 управления переходит в режим захвата. При этом на выход блока 11 проходит поступивший импульс, а кольцо поиска размыкается. Частота и фаза генератора тактовых импульсов подстраиваются к установившимся значениям (фиг. 9). При этом уменьшаются величины изменения временного интервала .между моментами записи и считывания в блоке 7 динамической памяти. длительности импульсов на выходе временного детектора 1 и усредненного значения напряжения этих импульсов до величины

Uy. Прекращается формирование импульсов аварии и захвата блоком 8 контроля (фиг. 9В, ГЗ), а управление осуществляется импульсами вставок(фиг. 9 Г1, Г2). В промежутках времени между импульсами вставок (фиг. 9 Г1, Г2) управляющий сигнал остается неизменным. Значение управляющего сигнала изменяется только при поступлении вставки, В этом режиме подстройка генератора тактовых импульсов происходит мед1826135

12 леннее, чем в режиме поиска. Временное положение (фаза) тактовых импульсов подстраивается K установившемуся значению, Далее значение управляющего сигнала остается неизменным, что исключает временные флюктуации тактовых импульсов и наступает установившийся режим, Из изложенного выше видно, что управляющий сигнал имеет дискретные значения, а следовательно, и частота тактового генератора также имеет дискретные значения, что является причиной ухода временного . положения тактовых импульсов от установившегося значения при сверхнизкой частоте следования вставок, Для устранения этого недостатка используется сумматор 4, в котором рассматриваемый управляющий сигнал складывается с ослабленным управляющим сигналом, снимаемым с выхода второго ФНЧ 10. С помощью последнего осуществляется регулирование частоты генератора тактовых импульсов в промежутках между дискретными значениями, Т.к. управляющий сигнал на выходе второго ФНЧ 10 имеет переменную (пилообразную) составляющую, то и в суммарном управляющем сигнале присутствует переменная составляющая, которая приводит к временным флюктуэциям тактовых импульсов.

При медленных изменениях фазы входного сигнала (тактовой последовательности). обусловленной нестабильностью тактовых генераторов записи и считывания на передающей стороне системы связи, устройство осуществляет подстройку фазы генератора тактовых импульсов, как описано в режиме захвата. В случае срыва синхронизации устройство переходит в режим поиска, описанный выше.

Формула изобретения

1. Устройство фазовой автоподстройки частоты, содержащее временной детектор, делитель частоты, цифроаналоговый преобразователь (ЦАП) и последовательно соединенные сумматор, первый фильтр нижних частот (Ф Н Ч) и генератор тактовых импул ьсов, о т л и ч а ю щ е е с я тем, что, с целью повышения степени ослабления временных флюктуаций фазы сигнала тактовой частоты путем выделения постоянной составляющей управляющего сигнала, введены буферный регистр, аналого-цифровой преобразователь (АЦП), накопитель, блок формирования временных интервалов, коммутатор, блок управления, блок контроля, второй ФНЧ и блок динамической памяти, первый и второй входы ко",îðîãî являются соответственно информационным и тактовым входами устройства. э к третьему входу

55 блока динамической памяти и входу делителя частоты подключен выход генератора тактовых импульсов, при этом первый выход блока динамической памяти является информационным выходом устройства, а второй и третий выходы блока динамической памяти подключены соответственно к первому и второму входам временного детектора. выход которого через второй ФНЧ подключен к входу блока контроля, первым входам коммутатора и сумматора, к второму входу которого подключен выход ЦАП, при этом первый и второй входы блока управления являются соответственно входами положительного и отрицательного стаффинга устройства, а первый и второй выходы блока контроля подключены соответственно к входу запрета и информационному входу блока управления, выход которого подключен к входу блока формирования временных интервалов, первый и второй выходы которого подключены соответственно к второму и третьему входам коммутатора, первый и второй выходы которого подключены соответственно к первому и второму входам накопителя, при этом выходы блока формирования временных интервалов, накопителя и делителя частоты подключены соответственно K первому, второму и третьему входам аналого-цифрового преобразователя (АЦП), m + 1 выходов которого подключены к m + 1 выходам буферного регистра, m выходов которого подключены к m входам ЦАП, причем m + 1 выход ЦАП подключен к управляющему входу блока управления.

2. Устройство по и, 1, о т л и ч а ю щ е ес я тем, что блок контроля содержит первый, второй и третий источники опорных напряжений, первую и вторую дифференцирующие цепи, первый, второй и третий компараторы, элемент ИЛИ, выпрямители .и элемент ЗАПРЕТ, выход которого является первым выходом блока контроля, вторым выходом которого является выход элемента

ИЛИ, подключенный к первому входу элемента ЗАПРЕТ, к второму входу которого подключен выход выпрямителя, при этом выходы первого и второго источников опорного напряжения подключены к инверсным входам соответственно первого и второго компэраторов, выходы которых подключены соответственно к входу второй дифференцирующей цепи и первому входу элемента ИЛИ, к второму входу которого подключен выход третьего компаратора, к прямому входу которого подключен выход третьего источника опорного напряжения, причем к прямому входу второго компаратора и инверсному входу третьего компарато182 á135

Ра подключен выход первой дифференцирующей цепи, вход которой соединен с прямым входом первого компаратора и является входом блока контроля, а выход второй дифференцирующей цепи подклю- 5 чен к входу выпрямителя, 3. Устройство по и. 1, о тл и ч а ю ще ес я тем, что блок управления содержит элемент ИЛИ, RS-триггер и коммутатор, выход которого является выходом блока управле- 10 ния, входом положительного стаффинга, входом отрицательного стаффинга и входом запрета которого являются соответственно первый, второй и третий входы элемента

ИЛИ, выход которого подключен к второму 15 входу коммутатора и R-входу RS-триггера, S-вход которого соединен с первым входом коммутатора и является информационным входом блока управления, при этом прямой выход RS-триггера подключен к третьему и 20 четвертому входам коммутатора, а инверсный выход RS-триггера подключен к пятому входу коммутатора, шестой вход которого является управляющим входом блока управления. 25

4, Устройство по п.1, о т л и ч а ю щ е ес я тем, что блок формирования временных интервалов содержит последовательно соединенные по инверсным выходам первый, второй, третий и четвертый ждущие мульти- 30 вибраторы, при этом прямые выходы первого. третьего и четвертого ждущих мультивибраторов являются соответственно первым, вторым и третьим выходами блока формирования временных интервалов. входом которого является вход первого ждущего мультивибратора.

5, Устройство по п.1, отл и ча ю ще ес я тем, что накопитель содержит первый и второй повторители напряжения, делитель напряжения, состоящий из первого и второго резисторов, первые выводы которых объединены и являются выходом накопителя, а вторые выводы первого и второго резисторов соединены с выходами соответственно первого и второго повторителей напряжения, а также две накопительные цепи. каждая из которых состоит из резистора и конденсатора, первый вывод которого соединен с общей шиной. при этом первые выводы резисторов первой и второй накопительных цепей являются соответст-. венно первым и вторым кодами накопителя, при этом вторые выводы резисторов первой и второй накопительных цепей соединены с вторыми выводами конденсаторов соответствующей накопительной цепи и входами соответственно первого и второго повторителей напряжения.

1826i35

1826135 г, г; с

1826135

1826135

Уу

1826135

Составитель Г.Лерантович

Техред M.Ìîðãåíòàë Корректор М.Самборская

Редактор

Производственно-издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101

Заказ 2322 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035 Москва Ж-35 Ра шская наб. 4/5