Тестопригодный цифровой автомат

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в диагностических комплексах для проверки правильности функционирования цифровой аппаратуры. Цель изобретения - повышение быстродействия диагностирования, изобретение содержит группу из п триггеров-защелок 1, группу из (п-1) сумматоров 2 по модулю два, группу из п D-триггеров З, комбинационный решающий блок 4, группу информационных выходов 5, группу информационных входов 6, первый 7, второй 8, третий 9 тактовые входы, вход начальной установки автомата, четвертый тактовый вход 11, информационный вход 12, выход 13 результата контроля. Поставленная цель достигается тем, что процедура контроля всего автомата сводится к проверке правильности функционирования лишь его комбинационной части с одновременным формированием нового испытательного набора и фиксацией текущего состояния в течение одного такта контроля. 4 ил., 1 табл. 1

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я >я 6 06 F 11/00

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛ ЬСТВУ! !

00 (Ь2 О 43

1о (21) 4875043/24 (22) 15.10.90 (46) 23.07.93. Бюл. N 27 (71) Киевский политехнический институт им,50-летия Великой Октябрьской социалистической революции (72) А.М,Романкевич, B.В,Гроль и О.А,Петлин (56) Патент США М 4503537. кл. G 06 F 11/00, 1985. (54) ТЕСТОПРИГОДНЫЙ ЦИФРОВОЙ АВТОМАТ (57) Изобретение относится к вычислительной технике и может быть использовано в диагностических комплексах для проверки правильности функционирования цифровой аппаратуры. Цель изобретения — повыше„„Я2„„1829036 А1 ние быстродействия диагностирования.

Изобретение содержит группу из и триггеров-защелок 1, группу из (и-1) сумматоров 2 по модулю два, группу из и D-триггеров 3, комбинационный решающий блок 4, группу информационных выходов 5, группу информационных входов 6, первый 7, второй 8, третий 9 тактовые входы, вход начальной установки автомата, четвертый тактовый вход 11, информационный вход 12, выход

13 результата контроля. Поставленная цель достигается тем, что процедура контроля всего автомата сводится к проверке правильности функционирования лишь его комбинационной части с одновременным формированием нового испытательного набора и фиксацией текущего состояния в течение одного такта контроля. 4 ил., 1 табл.

1829036

Изобретение относится к вычислительной технике и может быть использовано в диагностических комплексах для проверки правильности функционирования цифровой аппаратуры, Цель изобретения — повышение быстродействия диагностирования.

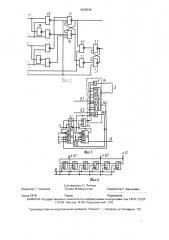

На фиг. 1 приведена функциональная схема автомата; на фиг. 2 — пример реализации триггера-защелки; на фиг, 3 и 4 — примеры реализации двухразрядного автомата и генератора псевдослучайных чисел.

Автомат содержит группу из и триггеров-защелок 1, группу из (n-1) сумматоров по модулю два, группу из n D-триггеров 3, комбинаци. нный решающий блок 4, группу информационных выходов 5, группу информационных входов 6, первый 7, второй 8, третий 9 тактовые входы, вход 10 начальной установки автомата, четвертый тактовый вход 11, информационный вход 12, выход 13 результата контроля, На фиг. 1 показаны также выходы 14.1 — 14.п блока 4.

Триггер-защелка содержит элементы ИНЕ 15 — 18 и элемент ИЛИ-НЕ 19, элементы

И-НЕ 20 — 23, а также элементы И-НЕ 24, 25 и элемент ИЛИ-HE 26, Автомат работает в системном и тестовом режимах.

В системном режиме текущее состояние выходов блока 4 определяется состоянием элементов памяти автомата и информацией, поступающей на входы 6 от внешней функционального блока системы в составе которой автомат работает, Начальное состояние элементов памяти автомата определяется пользователем, причем, если в исходном состоянии на первом выходе триггера 1,i (i = 1, n) должен быть установлен единичный потенциал, то ко входу V триггера 1л должен быть подключен четвертый вход элемента И-НЕ 19 (фиг. 2). При этом в течение времени, пока на входе V установлен логический нуль, на выходе элемента

И-НЕ 19 будет удерживаться единичный сигнал.

В системном режиме на входы 8 и 11 подаются неперекрывающиеся друг относительно друга серии тактовых импульсов, а входы 7 и 9 не активизируются и на них установлен лог, О. На входы 8 и 11 автомата подаются неперекрывающиеся друг относительно друга серии тактовых импульсов, а входы 9 и 7 не активизируются, В системном режиме триггер 1л функционирует следующим образом, Информация со входа D 2 (фиг. 2) при появлении на входе С2 тактового импульса переписывается в триггер, образованный элементами И-НЕ 17, 18. На входах С1 и СЗ триггера установлен логический

55 нуль. Таким образом, триггер 1.i в системном режиме функционирует как однотактный D-триггер. В системном режиме сумматоры 2 выполняют функции повторителей сигналов с выходов 12 блока 4, т.к, на вторых выходах триггеров 1 установлен нулевой потенциал. В результате пара триггеров 1,1 и 3.1 образуют двухтактный 1-й элемент памяти автомата. Запись информации в такой элемент памяти осуществляется при последовательном появлении синхроимпульсов на входах 8 и 11 автомата, В тестовом режиме работы автомата на его информационные входы 6 и 12 подаются псевдослучайные числа, а на входы 7 — 9, 11 — неперекрывающиеся друг относительно друга серии тактовых импульсов.

Фиг, 3 иллюстрирует тестовый режим двухразрядного автомата.

На фиг, 4 приведен пример реализации шестиразрядного генератора псевдослучайных чисел 13, который состоит из D-триггера и пяти Т-триггеров, соединенных последовательно. Прямые выходы триггеров являются выходами генератора. Входы

6.1 и 6.2 проверяемого автомата подсоединены к первому и четвертому выходам шестиразрядного генератора псевдослучайных чисел 13, а вход 12 — к шестому выходу генератора 13.

B таблице представлена процедура тестирования цифрового автомата в течение 7 тактов функционирования генератооа псевдослучайных чисел. Генератор устанавливается в исходное состояние 111111 одновременно с тестируемым автоматом (код 10 на первых выходах триггеров 1.1 и

1.2 принят в качестве кода начального состояния элементов памяти рассматриваемого автомата в системном режиме. При появлении на входе 11 автомата очередного тактового импульса код 10 с выходов триггеров 1 переписывается в соответствующие триггеры 3. Снятием сигнала начальной установки со входа 10 на входе начинается процедура тестирования автомата (см. таблицу).

В тестовом режиме триггер 1,i функционирует следующим образом. При появлении тактового импульса на входе С2 триггера информации со входа D2 записывается в триггер, образованный из элементов И-НЕ

17, 18 (на выходах элементов И-НЕ 15 и 16 установлен единичный сигнал, т,к. в момент действия импульса на входе 22 вход 21 не активизируется), С приходом на вход СЗ очередного тактового импульса информация с выхода триггера, образованного из элемента И-НЕ 17 и 18, переписывается в триггер, образованного из элементов И-НЕ 22, 23.

1829036

При появлении на входе С1 тактового импульса информация с входа D1 переписывается в триггер, образованный из элементов

И-НЕ 17 и 18 (на выходах элементов И-НЕ

24. 25 установлен единичный сигнал, т.к. в 5 момент действия импульса на входе С1 вход

С2 не активизируется). Триггеры, образованные элементами И-Н Е 22 и 23 триггеровзащелок 1, предназначены для хранения промежуточной информации с выходов бло- 10 ка 4 автомата. По мере продвижения информации в цепочке триггеров 1, на втором выходе k-го триггера 1 (k = 2), формируется результат суммы по модулю два сигналов со второго выхода (k-1)-го триггера 1 блока 4. 15

Сигнал с выхода 14,1 блока 4 записывается в триггер 1.1. В случае проявления на одном из выходов блока 4 ошибочного сигнала использование сумматоров 2 в цепочке триггеров 1 гарантирует. что этот ошибочный 20 сигнал не будет замаскирован по мере загрузки и продвижения тестовой информации на выход 13 автомата.

Формула изобретения 25

Тестопригодный цифровой автомат. содержащий группу из и триггеров-защелок и комбинационный решающий блок, группа входов и группа выходов которого образуют группу информационных входов и группу 30 информационных выходов автомата соответственно, отличающийся тем, что, ! целью повышения быстродействия диагР Выхоыы Bx0let так-! генератора автоыата та

1 ! 123458!7118910 ! I .zzzzzz î oîz о

I и ооо о

t !о zoo o

t !o czo z

2 100000!0 OOI 1

1 и ooo z

I !о zоо z ! !о czo z

3 !OIOOOO!O OOI

1 и ооо ! !о zîо

1 !Î ÎZ0Z

1 I

4 OII 000!0 OOI I ! и ооо ! !o zoo z

I !О О1О 1

5 010100!О OOI 1 ! и ооо

1 !О 1ОО

1 !Î 0ZО

6 OII II 0!O 001 I

t И ООО 1 ! .о zîo z

1 I

7 rOIOOPI ro 001 I ! !Z OOO 1 ! о zoo z

t ОО 1О 1 ностирования. в него введены группа из Il

D-триггеров и группа иэ и-1 сумматоров по модулю два, причем первый информационный вход первого триггера-защелки является информационным входом автомата, первый выход i-го триггера-защелки группы соединен с информационным входом i-го

D-триггера (i=1, и), выход j-го 0-триггера соединен с первым информационным входом (j+1)-го триггера-защелки и с i-м входом комбинационного решающего блока (j = 1, п-1), выход и-го D-триггера соединен с и-м входом комбинационного решающего блока, первый выход которого соединен с вторым информационным входом первого триггеразащелки, второй выход j-го триггера-защелки соединен с первым входом j-ro сумматора по модулю два, второй вход которого подключен к соответствующему выходу. начиная с второго, комбинационного решающего блока, выход j-ro сумматора по модулю два соединен с вторым информационным входом (j+1)-го триггера-защелки, второй выход и-го триггера-защелки является выходом результата контроля автомата, входы установки в исходное состояние п триггеров-защелок образуют вход начальной установки автомата, первые, вторые и третьи тактовые входы триггеров-эащелок группы образуют соответственно первый, второй и третий тактовые входы автомата, тактовые входы D-триггеров группы образуют четвертый тактовый вход автомата. ! Выходы !Зыхолы !Состояння ! блока 4 !трхггеров!триггеров ! I

I Z 1 1 ! 14.1 14.2! пер- вто- 3.1! 3.2

1 не

Х Х !IO!PO!Z !Х

Х Х !1ООО !Х !Х о о !zo!oo!z !о ! О О !00!00!I !О !

00!CO!00!I !0 ! О О OI!00 I !О ! О О !Oi!GD!0 !1 ! О О !00roo !0 !i ! О О !00!00!0 !I

О О !00!00!0 !1 ! I О !00!00!0 !О о !zo!oo!î !о

1 1 ) 1 ! I О !I 0 !1 0 О r 0 ! I О !00!IO!0 !О ! I О !00!10!0 !О ! 1 О . 11ИО !О !Р

О IZ!ZZ! O !О

0 0 OrI I r 0 P

О -ООИ1! Î Î о !Iz!Iz!о .о

О !ZZ!I

О !ООИ1!O !О о !oo!11!o !о

1 1

О IZZ!Z ° !О !О

О I O!I Z 0 . О

О O !10!11!I

О О 01111 I Z

1829036

77 к!2

Корректор Т. Ваш кович

Редактор T. Иванова

Заказ 2476 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035. Москва, Ж-35. Раушская наб.. 4/5

Производственно-издательский комбинат "Патент". г. Ужгород, ул,Гагарина, 101

8

Составитель О. Петлин

Техред М.Моргентал