Устройство для симметрирования бинарных сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и связи. Его использование в технике цифровой передачи данных позволяет повысить точность симметрирования. Устройство содержит на передающей стороне регистр 1 сдвига, параллельно-последовательный регистр 2, счетчики 3, 4 четности и управляемый инвертор 5, на приемной стороне - регистр 11 сдвига, блок 14 синхронизации приема и управляемый инвертор 13. Благодаря введению на передающей стороне элемента И 6, элемента НЕ 7, блока 8 синхронизации передачи и источника 9 (логической единицы, а на приемной стороне - параллельно-последовательного регистра 13 в устройстве обеспечивается более точное симметрирование передаваемого сигнала.4 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) ОПИСАНИЕ ИЗОБРЕТЕНИ нал

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4876508/24 (22) 22.10.90 (46) 23.07.93. Бюл. М 27 (71) Новосибирский электротехнический институт связи им. Н.Д.Псурцева (72) H.В.Верховский, Г.Х.Гарсков и А.Н.Горидько (56) Авторское свидетельство СССР

М 476696, кл. Н 03 M 5/18, 1972.

Заявка Великобритании hh 2072998, кл, Н 04 1 25/49, 1981. (54) УСТРОЙСТВО ДЛЯ СИММЕТРИРОВАНИЯ БИНАРНЫХ СИГНАЛОВ (57) Изобретение относится к вычислительной технике и связи. Его использование в

„„ „„1829118 А1 (51)5 Н 03 М 7/00, Н 04 25/49 технике цифровой передачи данных позволяет повысить точность симметрирования, Устройство содержит на передающей сто. роне регистр 1 сдвига, параллельно-последовательный регистр 2, счетчики 3, 4 четности и управляемый инвертор 5, на приемной стороне — регистр 11 сдвига, блок 14 синхронизации приема и управляемый инвертор 13. Благодаря введению на передающей стороне элемента И 6, элемента Н Е 7, блока 8 синхронизации передачи и источника 9 логической единицы, а на приемной стороне — параллельно-последовательного регистра 13 в устройстве обеспечивается более точное симметрирование передаваемого сигнала. 4 ил.

1829118

Изобретение относится к вычислительной технике и связи и может быть использовано в технике цифровой передачи данных.

Цель изобретения — повышение точности симметрирования.

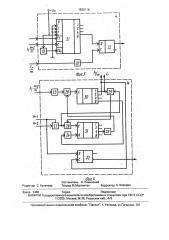

На фиг.1 изображена функциональная схема устройства для симметрирования бинарных сигналов; на фиг.2 и 3 — примеры реализации первого и второго счетчиков четности на передающей стороне; на фиг,4 — пример выполнения блока синхронизации приема.

Устройство для симметрирования бинарных сигналов содержит на передающей стороне регистр 1 сдвига, параллельно-последовательный регистр 2, первый и второй счетчики 3, 4 четности, управляемый инвертор 5, элемент 6 И, элемент 7 НЕ, блок 8 синхронизации передачи и источник 9 логической единицы. Вход устройства обозначен поз.10. На приемной стороне устройство содержит регистр 11 сдвига, параллельно-последовательный регистр 12, управляемый инвертор 13 и блок 14 синхронизации приема. Выход устройства обозначен поз.15.

Первый счетчик 3 четности выполнен (фиг.2) на элементе 16 задержки, двоичном счетчике 17 и триггере 18.

Второй счетчик 4 четности выполнен (фиг.3) на первом и втором элементах 19, 20 задержки, двоичном счетчике 21 и триггере 22.

Блок 14 синхронизации приема для случая m = 2 (m — длина входного кодового слова) содержит (фиг.4) первый-третий элементы

23 — 25 задержки, элемент 26 ИЛИ, первый и второй элементы 27, 28 ИСКЛЮЧАЮЩЕЕ

ИЛИ, элемент 29 И, первый и второй двоичные счетчики 30, 31 и триггер 32.

Устройство работает следующим образом.

На передающей старане входные двоичные кодовые символы, поступающие с входа 10 со скоростью Ч, определяемой тактовой частотой Рт и подаются .одновременно на m-разрядный регистр 1 сдвига и первый счетчик 3 четности. Один раз за каждые m тактов накопленная в регистре 1 сдвига информация переписывается в ïàраллельно-последовательный регистр 2, имеющий m+2 разрядов. Одновременно в его (m+1)-й разряд записывается уровень логической единицы с источника 9, а в (гп+2)й разряд — уровень лагическога нуля с выхода элемента 7 НЕ. После этого осуществляется вывод записанной информации из регистра 2 в последовательном

m+2 коде со скоростью Ч через управляемый инвертор 5, на второй вход которого поступает управляющий сигнал с выхода элемента 6 И. В зависимости от этого сигнала на выходе управляемого инвертора 5 появляется инвертированное или неинвертированное (m+2)-разрядное кодовое слово, поступающее в последователь10 ном коде в канал связи. Первый счетчик 3 четности вычисляет алгебраическую сумму

Si символов каждой m-значной комбинации (если поступает сигнал с уровнем логической единицы, сумма $} увеличивается на

15 единицу, нуля — уменьшается на единицу):

Si= а(, (1)

I =1 где а(— входной кодовый символ;

1 — порядковый номер комбинации;

J — порядковый номер символа в каждой

m-значной комбинации, и в зависимости от ее знака подает сигнал на элемент 6 И (если знак положительный —.

25 уровень логической единицы, отрицательной — логического нуля). Второй счетчик 4 четности содержит информацию об асимметрии выходного сигнала и подает на второй вход элемента 6 И сигнал, 30 определяемый как

Sign Sx(i-1} Sign g Ьь (2}

k=1 где 3с - (3-1) (я+2);

Ь вЂ” символы на выходе управляемого

35 инвертора5, Если знак суммы на выходе второго счетчика 4 совпадает са знаком суммы на выходе первого счетчика 3, на выходе элемента 6 И формируется сигнал с уровнем

40 логической единицы и данная (а+2)-значная комбинация инвертируется, т.е. уровень асимметрии сигнала уменьшается. При несовпадении знаков сумм инвертирования не происходит. Блок 8 синхронизации пере45 дачи обеспечивает согласованную работу передающей стороны, На приемной стороне двоичный сигнал с выхода канала связи са скоростью

m +2

50 Ч поступает на (в+2)-разрядный регистр 11 сдвига; Один раз за m+2 тактов накопления, информация с m выходов этого регистра 11 сдвига переписывается по сигналу с блока 14 синхронизации. приема в

55 параллельна-последовательный регистр 12, откуда считывается со скоростью Ч в последовательном коде, поступая на информационный вход управляемого инвертора 13.

Блок !4 синхронизации приема по всегда

1829118

15

25

40 инвертированным по отношению друг к другу сигналам (а+1)-го и (я+2)-го разрядов на выходах регистра 11 сдвига определяет границу кодового слова и дает сигнал на запись в регистр 12. По знаку (гп+1)-го разряда регистра 11 сдвига блок 14 также определяет, было ли инвертировано переданное кодовое слово, и в зависимости от этого подает управляющий сигнал на управляющий вход инвертора 13 для восстановления исходной кодовой комбинации, Формула изобретения

Устройство для симметрирования бинарных сигналов, содержащее на передающей стороне регистр сдвига, информационный вход которого является входом устройства, параллельно-последовательный регистр, первый и второй счетчики четности и управляемый инвертор, на приемной стороне — регистр сдвига. блок синхронизации приема, тактовый вход которого является тактовым входом приемной стороны, и управляемый инвертор, выход которого является выходом устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения точности симметрирования, на передающей стороне введены элемент И, элемент HE, источник логической единицы и блок синхронизации передачи, первый выход которого соединен с тактовым входом регистра сдвига и счетным входом первого счетчика четности, вход реверсирования счета которого подключен к входу устройства, первый — m-й выходы регистра сдвига (m — длина входного кодового слова) соединены с одноименными информационными входами параллельно-последовательного регистра, (гп+1)-й и (m+2)-A информационные входы которого непосредственно и через элемент

НЕ подключены к источнику логической единицы, второй выход блока синхронизации передачи соединен с входом разрешения записи параллельно-последовательного регистра и с входами разрешения считывания первого и второго счетчиков четности, выходы которых подключены соответственно к первому и второму входам элемента И, выход которого соединен с управляющим входом управляемого инвертора, третий выход блока синхронизации передачи подключен к счетному входу второго счетчика четности и тактовому входу параллельно-последовательного регистра, выход которого соединен с информационным входом управляемого инвертора, выход которого подключен к входу реверсирования счета второго счетчика четности и является выходом передающей стороны, на приемной стороне введен параллельно-последовательный регистр, информационный вход регистра сдвига является информационным входом приемной стороны, тактовый вход регистра сдвига подключен к тактовому входу приемной стороны, первый — m-й выходы регистра сдвига соединены с одноименными информационными входами параллельно-последовательного регистра, (m+1)-й и (m+2)-й выходы регистра сдвига подключены к первому и второму управляющим входам блока синхронизации приема, первый и второй выходы которого соединены соответственно с входом разрешения записи и тактовым входом параллельно-последовательного регистра, выход которого и третий выход блока синхронизации приема подключены соответственно к информационному и управляющему входам управляемого инвертора.

ЩlГ 4 Составитель О. Ревинский

Редактор С. Кулакова Техред М.Моргентал Корректор А Козор»

Заказ 2480 Тираж Подписное

БНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. ужгород, ул.Гагарина, 101