Устройство для подсчета количества единиц

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и позволяет определять количество единиц в параллельном коде в двоично-десятичной системе счисления. УСТРОЙСТВО содержит делители количества единиц на две группы 1, определяющие младшие разряды тетрад результата, и делители количества единиц на пять групп 2, вычисляющие три старших результата. 4 ил., 2 табл.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (54)5 Н 03 М 7/04

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1 (21) 4878857/24 (22) 30.10.90 (46) 23.07.93. Бюл. 1Ф 27 (71) Одесский политехнический институт (72) А.В.Дрозд, Е.Л.Полин, T..Ï.Ìåëüíè÷óê и Ю.В.Дрозд (56) Авторское свидетельство СССР

f4 726526, кл, Н 03 М7/04,,1978.

Авторское свидетельство СССР

hh 450160, кл. Н 03 М 7/04, 1972. (54) УСТРОЙСТВО ДЛЯ ПОДСЧЕТА КОЛИЧ БСтВА ЕДИНИЦ

„„. Ц „„1829119 А1 (57) Изобретение относится к вычислительной технике и позволяет определять количество единиц в параллельном коде в двоична-десятичной системе счисления. Устоойство содержит делители количества единиц на две группы 1, определяющие младшие разряды тетрад результата, и делители количества единиц на пять групп 2, вычисляющие три старших результата. 4 ил., 2 табл.

18291 19

Изобретение относится к вычислительной технике и может использоваться в арифметических блоках 3ВМ, работающих в двоичНо-десятичной системе счисления.

Цель изобретения — расширение класса решаемых задач за счет возможности получения результата в двоично-десятичной системе счисления, Изобретение по сравнению с известными решениями содержит делители количества единиц на пять, позволяющие в совокупности с вновь введенными связями выполнить вычисление результата в двоично-десятичной системе счисления.

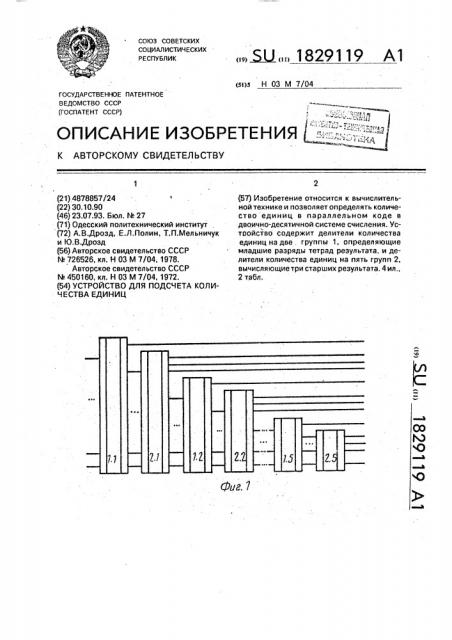

Структурная схема устройства показана на фиг.1.

n+1

Устройство содержит г = )!оцщ

2 блоков деления количества единиц в коде на два 1.1 — 1.r и. блоков деления количества единиц в коде на пять 2.1-2.r, где r- разрядность входного кода, причем входы блока

1.1 являются входами устройства, выходы частного каждого блока деления количества единиц в коде на два 1 1-1.г соединены соответственно с входами соответствующего блока деления количества единиц в коде на пять 2.1-2;г, выходы частного каждого. предыдущего блока деления количества единиц в коде на пять соединены с соответствующими входами последующего по номеру блока деления количества единиц в коде на два, выходы остатка соответствующих блоков деления количества единиц в коде на пять являются выходами разрядов соответствующих тетрад устройства, начиная с младшей тетрады, выход частного последнего блока деления количества единиц в коде на пять 2 является выходом первого разряда старшей (г+1)-й тетрады устройства.

Устройство работает следующим образом.

На выходы устройства поступает код, в котором необходимо определить количество единиц в двоично-десятичной системе счисления. Этот код подается на входы первого блока деления количества единиц в коде на два 1.1, который на выходах частного формирует код с количеством единиц, равным целочисленному частному от деления на два количества единиц входного кода, а на выходе остатка — остаток от указанного деления, являющийся младшим разрядом младшей тетрады искомого результата. Код, полученный на выходах частного блока 1.1 поступает на входы блока деления количества единиц в коде на пять 2.1, который на выходах частного формирует код с количеством единиц, равным целочисленному частному от деления на пять количества единиц его входного кода, а на выходах остаткэ— трехразрядный код остатка от указанного деления, определяющий три старших разряда младшей тетрады результата.

Код, полученный на выходах частного блока, поступает далее на входы блока деления количества единиц в коде на два 1.2, который аналогично блоку 1.1, описанному выше, определяет на выходе остатка младший разряд второй тетрады результата и код на выходах частного, обрабатываемый далее в блоке деления количества единиц в коде на пять 2,2 с получением трех старших

15 разрядов второй тетрады результата на выходах остатка и кода на выходах частотного для вычисления последующих тетрад результата на последующих блоках деления количества единиц в коде на два и пять. На последних делителях блоках деления коли-. чества единиц в коде на два 1.r и пять 2.r формируются разряды последней тетрэды результата (соответственно младший и три старших разряда тетрэды), а также младший

25 (единственный) разряд старшей тетрады результата на выходе частного блока 2 г. В случае нулевого значения этого разряда предпоследняя тетрада оказывается старшей тетрадой результата, Полученные раз30 ряды тетрад результата с выходов остатка блоков деления количества единиц в коде на два и пять, а также с выхода частного блока

2.r поступают на выходы устройства.

Блок деления количества единиц в коде на пять показан на фиг,2 и содержит сумматоры первой группы 3, сумматоры второй группы 4 и сумматор 5, все входы сумматоров первой группы 3 являются входами блока, выходы суммы и переноса первого

40 сумматора 3.1 группы соединены соответственно с входами первого и второго разрядов

nepaoro слагаемого первого сумматора 4.1 группы, вход переноса которого подключен к нулевой шине, первый и второй выходы

45 первого разряда и выход второго разряда каждого предыдущего сумматора группы 4 соединены соответственно с входом переноса и входами первого и второго разрядов пе рвого слагаемого последующего сумматоM ра группы 4, входы первого и второго разрядов второго слагаемого каждого сумматора группы 4 соединены соответственно с выходами суммы и переноса сумматора группы 3 с большим на единицу номером, первый и второй выходы первого разряда и выход второго разряда последнего сумматора группы 4 соединены соответственно с выходами соответствующих разрядов сумматора

5, выходы которого являются выходами остатка блока; а выходы переноса сумматоров

1829119 группы 4 являются выходами частного блока.

Сумматоры группы 3 выполняются на микросхемах К555ИМ5 и приводят входной код кувухоазрядным кодам с весами разря- 5 дов 2 и 2 соответственно на выходах суммы и переноса. Эти коды поступают на соответствующие входы сумматорсгв группы

4, которые выполняют сложение и формируют единичное значение на выходе переноса IO при сумме, равной или превышающей пять, а на двух выходах первого разряда и выходе второго разряда формируют код, равный сумме, если она не превышает пять,и сумме за вычетом пяти в противном случае. Сум- 15 маторы группы 4 организуют последовательное сложение двухразрядных кодов, что определяет на их выходах переносов код частного делителя на пять, а с выходов разрядов последнего сумматора группы 4 20 снимается код остатка с весами разрядов . 2, 2 и 2 . Для птоиве1дения кода остатка к весам разрядов 2, 2 и 2 он поступает на выход делителя.

Сумматор группы 4 показан на фиг.3 и 25 выполняется на микросхеме К155ИМ2 и логических элементах по табл.1, связывающей выходы микросхемы К155ИМ2 и выходы сумматора группы 4. Сумматор 5 выполнен по табл,2 и показан на фиг.4. 30

Рассмотрим подсчет количества единиц предложенным устройством на примере входного кода 001101110100. На выходе частного и остатка блока 1;1 формируются коды частного (с в два раза меньшим 35 количеством единиц по сравнению с входным кодом):01.1100 и остаток:О. Полученный код частного поступает на вход блока 2.1.

При этом на выходах входящих в состав блока 2.1 сумматоров 3.1, 3.2, 4.1 и 5 форми- 40 руются соответственно следующие коды 01, 10, 1100 (веса: 2, 2, 2, Р), 011..

Последний из этих кодов является кодом остатка на выходе остатка блока 2,1, а значение 0 на выходе P сумматора 4,1 — 45 кодом частного на выходе частного блока

2.1, Таким образом, результатом подсчета количества единиц во входном коде является двоично-десятичный код, состоящий из младшей и неполной старшей тетрэды; 0

0110, Пример окончен.

По сравнению с прототипом предложенное устройство позволяет определять количество единиц во входном коде в двоично-десятичной системе счисления, что расширяет класс решаемых задач.

Формула изобретения

Устройство для подсчета количества

n+1 единиц, содержащее r = )!9 2 (блоков деления количества единиц в коде на два (и — разрядность входного хода), к-й из которых (к = 1,r) содержит группу из и/ 2к сумматоров, вход переноса (i+1)-го из которых (I = 1,n/2к-1) соединен с выходом суммы 1-го сумматора группы, выходы переносов всех сумматоров к-й группы являются выходами частного к-го блока деления количества единиц входа на два, выход остатка которого соединен с выходом суммы последнего сумматора к-й группы и является выходом младшего разряда соответствующей к-й тетрады устройства, )-й и {i+1)-й входы которого соединены с входами fll-го сумматора группы (m = 1,п /2к) и являются входами первого блока деления количества единиц в коде на два, о т л и ч а ю щ е е с я тем, что, с целью расширения класса решаемых зада < за счет получения результата в двоично-десятичной системе счисления, оно содержит r блоков деления количества единиц в коде на пять, причем выходы частного к-го блока деления количества единиц в коде на два соединены с входами к-го блока деления количества

Единиц вкоде на пять,,выходы частного I-го из которых соединены с входами (i+1)-го блока деления количества единиц в коде на два, выходы остатка к-го блока деления количества единиц в коде на пять являются выходами трех старших разрядов к-й тетрады устройства, выход первого разряда старшей тетрады которого соединен с выходом частного. последнего блока деления количества единиц в коде на пять.

1829119

Таблица 1 (Таб лица 2

1829119

1829119

Составитель А. Дрозд

Техред ММоргентал Корректор И. Шмакова

Редактор С. Кулакова

Производственно-издательский комбинат "Патент", r. Ужгород, ул,Гагарина, 101

Заказ 2480 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Вмоскве, Ж 35, Раушская наб., 4/5