Перестраиваемый цифровой фильтр

Иллюстрации

Показать всеРеферат

-СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУГ>ЛИК (51)5 Н 03 Н 17/06

ИСАНИЕ ИЗ БР

llATE MTY ность изобретения — перестраиваемый цифровой фильтр содержит информационный вход 1, аналого-цифровой преобразователь

2, сумматор 3, блок 4 приема-передачи, блоки 5, 6 памяти, блок 7 усреднения, информационный выход 8, блок 9 управления, генератор 10 тактовых импульсов, вход 11 запуска, счетчик 12 адреса, вход 13 задания количества точек анализа, счетчик 14 циклов, вход 15 задания количеств: циклов, выход 16 сигнала конца преобразования. 2 ил.

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) (21) 4922446/09 (22) 28.03.91 (46) 23.07.93. Бюл, N 27 (75) А.Б.Ордынский и Н.С.Евсикова (7-6) Н.С.Евсикова (56) Авторское свидетельство. СССР

Й 1314444, кл. Н 03 Н 17!04, 1987. (54) ПЕРЕСТРАИВАЕМЫЙ ЦИФРОВОЙ

ФИЛЬТР (57) Использование: радиотехника, в системах цифровой обработки сигналов, Сущ Ы„„1830185 АЗ

1830185

Х (пТ), 55

Изобретение относится к радиотехнике и может быть использовано в системах цифровой обработки сигналов.

Цель изобретения — повышение быстродействия.

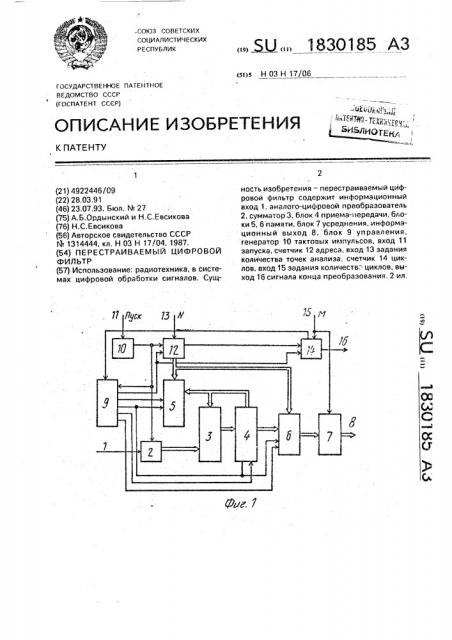

На фиг,1 приведена электрическая структурная схема перестраиваемого цифрового фильтра; на фиг.3 — алгоритм его работы.

Перестраиваемый цифровой фильтр (фиг.1) содержит информационный вход 1, аналого-цифровой преобразователь (АЦП)

2, сумматор 3, блок 4 приема-передачи, первый 5 и второй 6 блоки памяти, блок 7 усреднения, информационный выход, блок 9 управления, генератор 10 тактовых импульсов (ГТИ), выход 11 запуска, счетчик 12 адреса, вход 13 задания количества точек анализа, счетчик 14 циклов, выход 15 задания количества циклов, вход 16 сигнала конца преобразования.

Работает перестраиваемый цифровой фильтр следующим образом.

Начальному моменту работы предшествует выполнение следу ощих операций. Перед подачей сигнала запуска в счетчике 12 адреса записывается число N, à в счетчике 14 циклов число М, Количество циклов анализа M определяется требуемой статической достоверностью результата. Содержимое первого блока 5 обнулено.

Перестраиваемый цифровой фильтр работает по алгоритму, представленному на фиг,2. Сигнал запуска, включает ГТИ 10, ко. торый начинает вырабатывать тактовые импульсы. По каждому тактовому импульсу

АЦП 2 осуществляет преобразование амплитуды входного сигнала 1 в цифровой код, поступающий на вход сумматора 3. Счетчик

12 устанавливает на выходе адрес ячейки первого 5 и второго б блоков памяти, блок 9 управления вырабатывает сигнал выбора кристалла первого блока 5 и высокий уровень (чтение) по выходу "чтение-запись". После считывания содержимое ячейки памяти с информационнОго ВыхОдя первого блока 5 поступают на другой вход сумматора 3. Сигнал чте11ия первого блока 5 удер>кивается в течение Времени, достаточного для Выполнения чтения ячейки памяти и суммирооация ее содержимого с выходным кодом АЦП 2. По стробу записи, поступающему от блока.9 управления, результат суммирования записывается в блоке 4 приема-передачи, с его выхода поступает

HB информационныЙ вход первого блока 5 и но "игналу. записи, вырабатываемому блоком 9 управления, записывается в ячейку памяти, адрес которой установлен на адресных входах. С приходом следующего такто5

40 вого импульса на адресном входе первого блока 5 устанавливается адрес очередной ячейки памяти, АЦП 2 выдает код следующего отсчета и аналогично предыдущему такту происходит процесс чтения ячейки памяти первого блока 5, суммирования ее содержимого с входным кодом АЦП 2 и запись результата в- первый блок 5 по тому же адресу.

Каждый цикл анализа выделяемой частоты состоит из N тактов. С поступлением

N-ro импульса на выходе счетчика 12 адреса вырабатывается сигнал, по которому осуществляется предустановка счетчика 12 адреса на число N для прохождения следующего цикла, начинающегося с приходом очередного импульса ГТИ, М-1-циклов анализа выполняется аналогично.

С окончанием M-1-циклов счетчик 14 вырабатывает сигнал, поступающий на блок 9 управления, по которому производится настройка блока 9 управления на завершающий цикл анализа. Чтение содержимого ячейки первого блока 5, суммирование его с кодом АЦП 2 и запись результата в блоке 4 приема-передачи выполняется так же, как и в тактах предыдущих циклов, Затем блок 9 управления переводит сигнал выбора кристалла первого блока 5 в пассивное состояние, выбора кристалла второго. блока 6 — в активное, сигнал по выходу "Чтение-запись" с высокого уровня на низкий (запись), сигнал направления передачи информации через блок 4 приема-передачи на передачу к второму блоку 6, что инициирует процесс записи результата суммирования во второй блок 6 по адресу, установленному в начале такта на адресных входах первого 5 и второго 6 блоков памяти.

Таким образом выполняются все такты за- к вершающего цикла анализа. Результат анализа содержится в К последовательно размещенных ячейках второго блока б памяти, Содержимое каждой ячейки представляет собой сумму одноименных отсчетов за M циклов. где Х(п Г) — значение цифрового кода входного сигнала в i-ом такте.

По окончании завершающего цикла счетчик 14 циклов вырабатывает сигнал конца преобразования, по которому результат может быть считан со второго блока 6 для последующей обработки. Наличие выделяемой частоты в исходном входном сигнале однозначно определяется по закону изменения выходных отсчетов.

1830185

Управление вторым блоком 6 при считывании результата осуществляется внешним считывающим устройством (микроЭВМ либо контроллером).

Формула изобретения 5

Перестраиваемый цифровой фильтр, содержащий первый и второй блоки памяти, сумматор, отличающийся тем, что, с целью повышения быстродействия, введены генератор тактовых импульсов, счетчик 10 адреса, счетчик циклов, блок приема-передачи, блок усреднения, блок управления и аналого-цифровой преобразователь, первый вход которого является информационным входом перестраиваемого цифрового 15 фильтра, второй вход соединен с первым входом блока управления, выходом генератора тактовых импульсов, вход которого является входом запуска перестраиваемого цифрового фильтра, первым входом счетчи- 20 ка адреса, второй вход которого является входом задания количества точек анализа, а третий вход — входом управления начальной установкой и соединен с первым входом счетчика циклов и первым выходом блока 25 управления, первый выход соединен с вторым входом счетчика циклов. э второй выход с первым входом второго блока памяти и первым входом первого блока памяти, второй вход которого соединен с вторым выходом блока управления, а третий вход с третьим выходом блока управления, первым входом блока приема-передачи и вторым входом второго блока памяти, четвертый вход/выход соединен с первым выходом блока приема-передачи и первым входом сумматора, второй вход которого подключен к выходу аналого-цифрового преобразователя, а выход подключен к второму входу блока приема-передачи, третий вход которого является входом управления направлением передачи информации и подключен к четвертому выходу блока управления, à второй выход подключен к первому входу блока усреднения, выход которого является информационным выходом перестраиваемого цифрового фильтра, а второй вход соединен с третьим входом счетчика циклов, первый выход которого соединен с вторым входом блока управления, э второй выход является выходом сигнала конца преобразования перестраиваемого цифрового фильтра.