Способ определения времени запаздывания элемента задержки

Иллюстрации

Показать всеРеферат

Изобретение может быть использовано при измерении времени запаздывания электрических сигналов в различных элементах задержки. Цель изобретения - повышение точности измерения времени запаздывания элемента задержки. Способ определения времени запаздывания элемента задержки заключается в том, что преобразуют последовательность импульсов с частотой следования fex в последовательность импульсов с временной модуляцией со средней частотой fk, изменяют частоту fBX последовательности импульсов, определяют частоту fBx. на которой подавляются спектральные составляющие на частотах fk±m/T, где m 1, 3, 5,...; Т 1 /fk, измеряют частоту fax и используют результаты измере,ния для вычисления времени запаздывания по формуле Тз 1/2 причем fk меньше fex в дробное число раз. 4 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ass)s G 04 F 10/00

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР3

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4766307/21 (22) 11.10,89 (46) 30.07,93, Бюл. М 28 (71) Московский институт связи (72) В.Н,Кочемасов и А.Д.Ревун (56) Авторское свидетельство СССР

М 1262443, кл. С 04 F 10/00, 1984. (54) СПОСОБ ОПРЕДЕЛЕНИЯ ВРЕМЕНИ

ЗАПАЗДЫВАНИЯ ЭЛЕМЕНТА ЗАДЕРЖКИ (57) Изобретение может быть использовано при измерении времени запаздывания электрических сигналов в различных элементах задержки, Цель изобретения — повышение точности измерения времени запаздывания элемента задержки. Способ

Изобретение относится к радиоизмерительной технике и может быть испол ьзовано для прецизионного измерения наносекундных и пикосекундных задержек различных физических элементов (отрезков линий, интегральных схем и т.д.).

Целью изобретения является повышение точности.

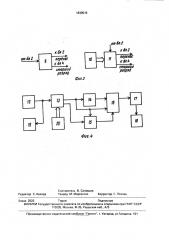

На фиг. 1 изображены функции фазовой модуляции (фиг. 1а,в) и соответствующие им спектры модулируемых сигналов (фиг. 1б,г); на фиг. 2 — пример реализации измерителя на основе делителя с переменным коэффициентам деления (ДПКД); на фиг. 3 — варианты реализации блока управления; на фиг, 4 — пример реализации измерителя на основе накопителя кодов, Измеритель времени запаздывания элемента задержки по схеме фиг, 2 содер„„. Ж„„1830515 А1 определения времени запаздывания элемента задержки заключается в том, что преобразуют последовательность импульсов с частотой следования f8X в последовательность импульсов с временной модуляцией со средней частотой fk, изменяют частоту f» последовательности импульсов, определяют частоту 4»*, на которой подавляются спектральные составляющие на частотах

1 +п /Т, где m = 1, 3, 5„.,; Т > 1/fk, измеряют частоту f»* и используют результаты измерения для вычисления времени запаздывания по формуле Тз = t/2 f<>*, причем fp меньше f» в дробное число раз. 4 ил. жит генератор 1 импульсной последовательности, делитель 2 с переменным коэффициентом деления (ДПКД), элемент 3 задержки, коммутатор 4, триггер 5, анализатор 6 спектра, частотомер 7, блок 8 управления.

Блок 8 управления по схеме фиг. За содержит счетчик 9, а в случае выполнения по схеме фиг. Зб — пульт 10 и накопитель 11 кодов.

Измеритель времени запаздывания элемента задержки по схеме фиг. 4 содержит генератор 12 импульсной последовательности, накопитель 13 кода задержки, одноразрядный статистический регистр 15, коммутатор 16, триггер 17, анализатор 18 спектра, частотомер 19, блок 20 управления.

Способ определения времени запаздывания Тз элемента задержки базируется на следующих положениях:

1830515

pl

1; При введении в сигнал с частотой Ь пилообразной фазовой модуляции с периодом Т - 1/F > 1/тк (фиг. 1а) в его спектре присутствуют составляющие на частотах

4 pF. где и - О, 1, 2, 3,... (фиг.1б). - .

2. При вдвое меньшей амплитуде и вдвое большей частоте функции пилообразной фазовой модуляции (фиг. 1в) в спектре сигнала исчезают составлрющие на часто тах Ь mF, где а " 1, 3, 5,... (фиг, 1г).

В соответствии с данным способом частота входной импульсной последовательности 4» делится в R или R + 1 раэ в зависимости от текущего значения определенным образом сформированного кода управления, в результате чего в спектре выходного квазимеандра появляются дискретные составляющие на частотах 4 + nF, где n..= =1, 2, 3, 4,... (фиг. 16). Часть импульсов полученной таким образом нерегулярной последовательности пропускается через элемент задержки с временем запаздывания Тз,.Алгоритм управления и частота 4» входных импульсов при этом подбираются таким. образом, чтобы неравномерность следования импульсов уменьшилась вдвое, до значения Тз = 1/2 4»*. Момент строгого выполнения равенства фиксируется по исчезновению спектральных составляющих с номерами rn = 1, 3, 5,... (см, фиг. 1б). Далее измеряют значение f è по формуле Т= 1/2»

»4,* рассчитывают время запаздывания элемента задержки, На основе данного способа может быть реализовано несколько вариантов измерителей (фиг. 2, 4).

В одном из них (фиг. 2) дробное давление частоты выполняется делителем 2 с переменным коэффициентом деления.

Деление на R или на R + 1 осуществляется по командам блока 8 управления, в котором формируется двоичный управляющий код

Кфс) = 4 «-Оепт (L),>

Давление осуществляется при условии, что код Куф) > Ку(К-1), 8 противном случае входная последовательность импульсов делителя e R + 1 раз. Выходной импульс ДПКД 2 поступает на вход триггера 5 непосредственно, если код Кф ) < Q/2 и через исследуемый элемент 3 задержки, если Ку(К) > О/2.

Такой режим прохождения импульсов обеспечивается коммутатором 4, управляемым старшим разрядом кода Kgk), который формируется в блоке 8 управления.

Блок 8 управления может быть выполнен либо на основе счетчика 9 (фиг. За). либо на основе кодов 11 (фиг. Зб). В первом случае L - m, Q — модуль пересчета счетчика 9, довательностью с частотой 4», где L = R>; 0 — код, подаваемый на вход накопителя 13 кодов;

Кфс} = Ва-Qent (Ra/Q), 30

К- номера импульсов переполнения накопителя 13 кодов. Управление коммутатором 16 осуществляется сигналом старшего

35 разряда кода управления Ky(k), который запоминается в одноразрядном статическом регистре 15. Остальные элементы схемы фиг. 4 выполняют те же функции, что и аналогичные элементы в схеме фиг. 2.

Частота выходного квазимеандра fk u частота F в предлагаемом способе равны

fk=, 0,5 4х/(Я + L/Q) F 2 fk 1 /О.

Основным преимуществом предлагаемого способа определения времени запаздывания является его высокая точность, которая достигается за счет исключения операции измерения амплитуд спектральных составляющих сформированного сигнала.

Формула изобретения

Способ определения времени запаздывания элемента задержки. заключающийся

55 в том, что преобразуют последовательность импульсов с частотой следования 4» в последовательность импульсов с временной модуляцией со средней частотой 4, о т л ич а ю шийся тем, что, с целью повышения точности, изменяют частоту f» последовакод Ky(k) соответствует числу, накопленному в счетчике 9 e k-й момент времени. Если блок 8 управления реализован по схеме, представленной на фиг. Зб, то код L, задава. емый с пульта 10, может принимать значения от 1 до 0 — 1, где 0-емкость накопителя кодов 11, код Kgk) соответствует числу, на10 копленному в k-й момент времени в накопителе 11 кодов. В обоих случаях (фиг. За,б) коммутатор 4 управляется сигналом со старшего разряда счетчика 9 или накопителя 11 кодов.

Во втором варианте измерителя (фиг. 4) дробное деление частоты осуществляется с помощью накопителя 13 кодов, из сигнала переполнения которого и формируется ква-. эимеандр, На вход N-разрядного накопите20 ля 13 кодов в этом случае падается код Q -(й/R) « 1.. а й/R — выбирается исходя из требуемой точности измерения запаздывания. В первом приближении точность измерения обратно пропорциональна

25 отношению N/R. Тактирование накопителя

13 кодов осуществляется импульсной после1830515

t 4, Фиг. / тельности импульсов, определяют частоту

4x*, на которой подавляются спектральные составляющие на частотах 4» +. m/T (где m=

-1, 3, 5,...; Т > 1/h4 измеряют частоту fex* и используют результаты измерения для вычисления времени запаздывания по формуле Тз - — fax*, причем fk меньше f x в дроб1

2 ное число раз.

1830515 рюзря

Составитель В. Соловьев

Техред M. Моргентал Корректор С. Пекарь

Редактор С. Коляда

Производственно-издательский комбинат "Патент" г. Ужгоро .Г жгород. ул. агарина, 101

Заказ 2522 Тираж

ВНИИПИГо а т

Подписное

Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Рауаская наб.. 4/5