Устройство для синхронизации вычислительной системы

Иллюстрации

Показать всеРеферат

Изобретение относится к устройствам генерирования и/или распределения синхронизирующих импульсов и может быть использовано при построении вычислительных систем на базе нескольких однотипных цифровых вычислительных машин. Цель изобретения - повышение точности синхронизации. Устройство содержит зада

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5п5 G 06 F 1/04

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4911133/24 (22) 12.02.91 (46) 30.07.93. Бюл. ЬЬ 28 (71) Научно-производственное объединение автоматики (72) Ф.Ф.Мингалеев, Н.Т.Пластун и В,А.Ковалев (56) Авторское свидетельство СССР

ГЬ 1539759, кл. G 06 F 1/04, 1987.

Авторское свидетельство СССР

М 1149235. кл. G 06 F 1/04, 1983. Ы, 1830527 А1 (54) УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ

ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ (57) Изобретение относится к устройствам генерирования и/или распределения синхронизирующих импульсов и может быть использовано при построении вычислительных систем на базе нескольких однотипных цифровых вычислительных машин.

Цель изобретения — повышение точности синхронизации, Устройство содержит зада1830527 ющий генератор 1, счетчик 2, дешифратор 3. триггеры 4, 5„элементы И 6-9, элементы НЕ

10-13, элемент ИЛИ 14, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 15. элемент И-НЕ 16, вход

17 сигнала точного времени общей системы отсчета, вход 18 сигнала режима работы без

Изобретение относится к устройствам генерирования и (или) распределения синхронизирующих импульсов и может быть использовано при построении вычислительных систем на базе нескольких однотипных цифровых вычислительных машин.

Целью изобретения является повышение точности синхронизации.

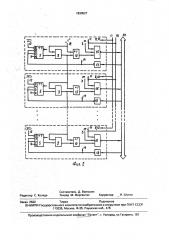

На фиг, 1 приведена схема устройства для синхронизации вычислительной системы, на фиг. 2 — соединение схем выбора приоритета устройств в вычислительной системе.

Устройство содержит задающий генератор 1, счетчик 2, дешифратор 3, триггеры

4, 5, элементы И 6, 7, 8, 9, элементы НЕ 10, 11, 12, 13, элемент ИЛИ 14, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 15, элемент И-НЕ 16, вход 17 сигнала точного времени общей системы отсчета, вход 18 сигнала режима работы без общей системы отсчета, вход 19 приоритета устройствэ1общую магистраль

20 вычислительной системы, выходы 21 устройства.

Каждый канал устройства содержит схему выбора приоритета (фиг. 2). содержащую триггер 5, элемент И 9, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 15. Схемы выбора приоритета всех каналов соединены между собой последовательно через шину 19 приоритета, Шина 19 приоритета первого канала (устройства) соединена с сигналом логической единицы.> т.е. первое устройство вычислительной системы имеет высший приоритет.

Устройство синхронизирует каждую

ЦВМ вычислительной системы с сигналами точного времени, поступающими по входу I7, плавно с дискретом в один такт частоты работы задающего генератора 1.

Устройство работает следующим образом, В исходном состоянии триггеры 4, 5, находятся в единичном состоянии, т.е. на инверсном выходе триггера 4 присутствует нулевой потенциал, а на прямом выходе триггера 5 — единичный потенциал.

Задающим генератором 1 формируется непрерывная серия тактовых импульсов, которая поступает на счетный вход счетчика 2.

40 общей системы отсчета, вход 19 приоритета. выходы 21 устройства. При отсутствии сигналов точного времени каналы ЦВж вычислительной системы синхронизируются между собой через устройство, обладающее высшим приоритетом. 2 ил.

По состояниям счетчика 2 на выходах дешифратора 3 при синхронном режиме работы устройства с сигналом точного времени формируется m выходных сигналов, а при несинхронном режиме работы — (m-1) выходных сигналов. Несинхронная работа устройства по сигналу точного времени, поступающему по входу 17, фиксируется на триггере 4. В зависимости от состояния триггера 4 последний и-й сигнал на выходе элемента ИЛИ 14 вырабатывается по принятию счетчиком 2 состояния m или (m-1). При появлении последнего(п-1) сигнала на выходе элемента ИЛИ 14 производится обнуление счетчика 2 и запись единицы на триггер

4, т.е. переход на следующий цикл выработки управляющих сигналов.

При синхронной работе устройства с сигналом точного времени цикл выработки управляющих сигналов является постоянным, т.е. последний управляющий сигнал цикла формируется íà m-м значении счетчика 2.

При несинхронной работе устройства с сигналом точного времени цикл выработки управляющих сигналов уменьшается на величину длительности одного такта (Л t) частоты работы задающего генератора 1. При этом количество управляющих сигналов в цикле остается неизменным, т.е. последний управляющий сигнал. цикла формируется на (m-1)-м значении счетчика 2.

При отсутствии сигналов точного времени по шине 17 (при неисправности или отсутствии общей системы отсчета) по шине

18 поступает во все устройства сигнал режима работы без общей системы отсчета. При этом на элементе 17 устройств запрещается прохождение сигнала из m-го входа дешифраторэ 3 на выходы 21 устройств и элементе

И-HE 16 открывается выход схемы приоритета на общую магистраль 20. При выработке сигнала на выходе (m-2-) дешифратора 3, на выходе (n-1) устройства через элемент

НЕ 12 производится обнуление триггера 5

При этом на выходе элемента И 9 первого устройства вычислительной системы устанавливается нулевой потенциал, который блокирует схемы выбора приоритета всех

1830527 других устройств (фиг. 2). Формируемый нулевой потенциал на выходе элемента И-НЕ

16 первого устройства через общую магистраль 20 в каждом устройстве поступает через элемент НЕ 13 и элемент ИЛИ 14 на выходы 21 устройства. При этом производится обнуление счетчика 2 и запись единицы на триггеры 4, 5, т.е. переход на следующий цикл выработки управляющих сигналов. В совокупности триггер 5 и элемент И вЂ” НЕ 16 контролируют исправность устройства, т.е. последовательное формирование значений счетчика 2 (m-2) и m.

При исключении из работы первого устройства высшим. приоритетом по синхронизации обладает второе устройство и т.д.

Формула изобретения

Устройство для синхронизации вычислительной системы, содержащее задающий генератор, счетчик, дешифратор, два элемента И, элемент ИЛИ, элемент НЕ, триггер, причем инверсный выход задающего генератора соединен со счетным входом счетчика, группа выходов которого соединена соответственно с группой входов дешифратора, (m-1)-й выход которого соединен с первыми входами первого и второго элементов И, вход сигнала точного времени общей системы отсчета устройства соединен с вторым входом второго элемента И и через первый элемент НŠ— с R-входом первого триггера, инверсный выход которого соединен с вторым входом первого элемента И, шина нулевого потенциала устройства соединена с К-входом первого триггера, выходы дешифратора с первого по (m-2)-й являются соответственно выходами с первого по {и-1)-й устройства, выходы первого и второго элементов И соединены соответственно с первым и вторым входами элемента

ИЛИ, выход которого соединен с входом установки в "0" счетчика, с J- и С-входами первого триггера и являются и-м выходом устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения точности синхронизации, в устройство введены триггер, два элемента

И, элемент И-НЕ, три элемента НЕ, элемент

ИСКЛЮЧАЮЩЕЕ ИЛИ, причем m-й выход дешифратора соединен с первыми входами третьего элемента И и элемента И-НЕ, вход сигнала режима работы без общей системы отсчета устройства соединен с вторым входом элемента И вЂ” НЕ и через второй элемент

НŠ— с вторым входом третьего элемента И, (m-2}-й выход дешифратора соединен через третий элемент НЕ с R-входом второго триггера, прямой выход которого соединен с первым входом четвертого элемента И, вход устройства для подключения к общей магистрали синхронизируемой вычислительной системы через четвертый элемент Н Е соединен с третьим входом элемента ИЛИ и с Jи С-входами второго триггера. выход третьего элемента И соединен с четвертым входом элемента ИЛИ. шина нулевого потенциала устройства соединена с К-входом второго триггера, выход четвертого элемента И является выходом наращивания устройства для подключения к входу приоритета последующего устройства и с первым входом элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ, вход приоритета соединен с вторыми входами четвертого элемента И и элемента

ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с третьим входом элемента И-НЕ, открытый коллекторный выход которого соединен с выходом устройства для подключения к общей магистрали синхронизируемой вычислительной системы, вход приоритета первого устройства соединен с шиной единичного потенциала устройства, 1830527

4иа 2

Редактор С. Коляда

Заказ 2522 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб„4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул,Гагарина, 101

}e

1 ! !

I

Составитель Д. Ванюхин

Техред М. Моргентал Корректор И, Шулла