Устройство для оценки точности вычислений

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть использовано при отладке и оценке точности многоверсионных программ. Цель изобретения - повышение точности оценки. Поставленная цель достигается за счет возможности сопоставительной оценки точности вычислений при многовариантной реализации вычислительной функции и определении, какой из вариантов реализации является более точным как на одном выбранном наборе исходных данных, так и на заданном потоке исходных данных. 2 ил., 1 табл.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (si)s G 06 F 11/00

ГОСУДАРСТВЕНЮЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4907270/24 (22) 23.11.90 (46) 30.07.93. Бюл. М 28 (72) А.В.Александров, А.Н.Лисиченок, Н.Б.Парамонов и Н.А. Шестериков (56) Авторское свидетельство СССР

tk 1205147, кл. G 06 F 11/00, 1984.

Авторское свидетельство СССР

hh 1462322, кл. G 06 F 11/00, 1987. (54) УСТРОЙСТВО ДЛЯ ОЦЕНКИ ТОЧНОСТИ ВЫЧИСЛЕНИЙ

Изобретение относится к области вычислительной техники и может быть использовано при отладке и оценке точности многоверсионных программ.

Цель изобретения — повышение точности оценки.

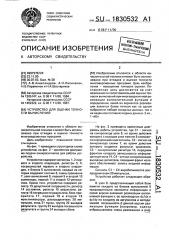

На фиг. 1 приведена структурная схема устройства; на фиг. 2 — временная -диаграмма подачи синхросигналов для работы устройства.

Устройство содержит регистры 1, 2 первого и второго операндов, регистры 3, 4, погрешностей первого и второго операндов, и блоков 5вычислений,,каждый из которых содержит счетчик 6, схему сравнения

7, узел вычислений 8, первый 9 и второй 10 сумматоры, первый 11 и второй 12 умножители. Кроме того, устройство содержит регистр 13 допустимой погрешности, регистр

14 состояния, регистр 15 результата, регистр 16 погрешности результата, блок приоритета 17, первый 18 и второй 19 мультиплексоры, распределитель 20 импульсов, вход 21 пуска, группу 22 выходов результата, группу 23 выходов погрешности результата и группу 24 выходов сбоев,,,SLY„, 1830532 А1 (57) Изобретение относится к области вычислительной техники и может быть использовано при отладке и оценке точности многоверсионных программ. Цель изобретения — повышение точности оценки, Поставленная цель достигается за счет возможности сопоставительной оценки точности вычислений при многовариантной реализации вычислительной функции и определении, какой иэ вариантов реализации является более точным как на одном выбранном наборе исходных данных, так и на заданном потоке исходных данных. 2 ил., 1 табл.

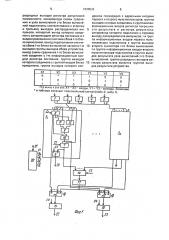

На фиг. 2 приведены временные диаграммы работы устройства, где С1 — сигнал на синхровходе узла 8, на время действия которого с выходов узла памяти 8 снимаются информационные сигналы, С2 — сигнал на синхровходе схемы 7, во время действия которого выдается результат сравнения, СЗ вЂ” синхросигнал регистра 14, передним фронтом которого записывается информация в регистр 14, С4 — сигнал синхронизации выходных регистров, передний фронт которого обеспечивает запись входной информации.

Сигналы С1 — С4 вырабатываются распределителем 20 импульсов.

Устройство работает следующим образом.

В узел 8, представляющий собой блок памяти каждого из блоков вычислений 5 предварительно заносится информация о своей версии значений реализации выполняемой функции г, ее производных dz/dx u

dz/dy по каждому из аргументов и методической погрешности б данной версии реализации функции (например, оценка отбрасываемого члена разложения в ряд).

1830532

Счетчики и регистры обнулены (цепи сброса условно не показаны) каждый цикл работы устройства состоит в следующем. В регистры 1 — 4 и 13 заносятся GOOTBGTcTBBHHO значения операндов, их погрешности и допустимая погрешность вычислений. На вход распределителя 20 со входа 21 устройства поступает сигнал пуска. который запускает очередной цикл работы устройства. С приходом сигнала С1 на выходах узлов 8 сформируются соответствующие значения производных dz/dx,-dz/dy и методической погрешности d. На выходе умножителей 11, 12 будут вычислены значения частных погрешностей dx/x hx и d/у Лу, которые суммируются на сумматоре 9, на выходе сумматора 11 — полная погрешность, включающая методическую погрешность d, то есть на первый вход схемы 7 сравнения и соответствующий информационный вход мультиплексора 19 подается значение погрешности, вычисленное по формуле

Ь = dz/dx + dz/dy + d.

Кроме того, с выходов результата узла 8 значения z подаются на соответствующие информационные входы мультиплексора 18.

По сигналу С2 схемы 7 сравнения выдают результаты сравнения, характеризующие допустимую погрешность 6. Если погрешность вычислений функции больше допустимой, то на выходе схему 7 появится единица, которая по сигналу С3 увеличит на единицу содержимое счетчика 6 и запишется в соответствующий разряд сигнала регистра 14. блок 17 формирует адрес выбранной версии реализованной функции.

Прошивка блока 17 определяет выбор первой версии реализации функции, для которой погрешность не превосходит допустимую.

Пример задания таблицы истинности блока 17 для трехверсионной реализации приведен в таблице.

По сигналу С4 выбранное значение к записывается в регйстр 15, а значение hz— в регистр 16.

Устройство готово к следующему циклу работы. Диаграмма подачи сигналов С1 — С4 приведены на фиг. 2.

Количество сбоев, подсчитанное в счетчиках 6, определяет точность соответствующей версии реализуемой функции.

Формула изобретения

Устройство для оценки точности вычислений, содержащее распределитель импульсов, вход пуска которого является

)-го блока вычислений (j = 2; и - 1) подключены к группам разрядных выходов регистров первого и второго операндов соответственно. вторые группы входов первого и второго умножителей !-ro блока вычислений подключены к группам разрядных выходов регистров погрешности первого и второго операндов соответственно. первая группа информационных входов схемы сравнения

j-го блока вычислений подключена к группе одноименным входом устройства, регистр первого и регистр второго операндов, регистр погрешности первого и регистр погрешности второго операндов, регистр допустимой погрешности, регистр погрешности результата, группа выходов которого является группой выходов погрешности результата устройства и блок вычислений, в состав которого входят узел вычислений, "0 два умножителя, первый сумматор и схема сравнения, первая группа информационных входов которой подключена к группе разрядных выходов регистра допустимой погрешности, первый и второй и третий выходы распределителя импульсов соединены с синхровходами регистра погрешности результата, схемы сравнения и узла вычислений, первая и вторая группы информационных входов которого подключены к

20 группам разрядных выходов регистров первого и второго операндов соответственно, первая и вторая группы выходов частных производных узла вычислений соединены с первыми группами входов первого и второго умножителей соответственно, вторые группы входов которых подключены к группам разрядных выходов регистра погрешности первого и регистра погрешности второго операндов соответственно, о т л и30 ч а ю щ е е с я тем, что, с целью повышения точности„в него введены n — 1 блоков вычислений, где и — возможное число реализаций вычисляемой функции, регистр состояния, блок приоритета, два мультиплексора и регистр результата, кроме того, каждый 1-й блок вычислений (I =.,1, п) дополнительно содержит второй сумматор и счетчик сбоев, причем группы выходов первого и второго умножителей соединены с первой и второй

40 группами входов первого сумматора, группа выходов которого соединена с первой группой входов второго сумматора, вторая группа входов которого подключена к группе выходов методической погрешности узла

45 вычислений, группа выходов второго сумматора соединена с второй группой информационных входов схемы сравнения, выход схемы сравнения соединен со счетным входом счетчика сбоев, первые и вторые группы

50 информационных входов узла вычислений

1830532

П р и м е ч а н и е: Х1 — ХЗ вЂ” входы. Y1 — Y3 — выходы. Значение

* в таблице означает пооизвольный сигнал (либо 0, либо 1). разрядных выходов регистра допустимой погрешности, синхровходы схемы сравнения и узла вычислений J-го блока вычислений подключены соответственно к второму и третьему выходам распределителя импульсов, четвертый выход которого соединен с синхровходом регистра состояния и с входом разрешения счетчика сбоев I-го блока вычислений, выход переполнения счетчика сбоев 1-го блока вычислений является l-м выходом группы выходов сбоев устройства, выход схемы сравнения I-го блока вычислений соединен с 1-м информационным входом регистра состояния, группа выходов которого соединена с группой входов блока приоритета, группа выходов которого соединена поразрядно с адресными входами первого и второго мультиплексоров, группы выходов которых соединены с группами информационных входов регистра погрешно5 сти результата и регистра результата, синхровход которого подключен к первому выходу распределителя импульсов, 1-я группа информационных входов первого мультиплексора подключена к группе выходов

10 второго сумматора I-ro блока вычислений, i-я группа информационных входов второго мультиплексора подключена к группе выходов результата узла вычислений i-го блока вычислений, группа разрядных выходов ре-.

15 гистра результата является группой выходов результата устройства, 1830532

С2

Фиу 2

Составитель А. Лисиченок

Техред М. Моргентал Корректор Л. Пилипенко

Редактор H. Коляда

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

Заказ 2523 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва. Ж-35, Раушская наб., 4/5