Устройство для исправления ошибок в кодовой комбинации

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи и может быть использовано в системах передачи дискретной информации с решающей обратной связью. Цель изобретения - повышение вероятности обнаружения ошибки. Устройство дополнительно содержит счетчик, дешифратор, элемент ИЛИ. Вновь введенные элементы позволяют реализовать алгоритм, при котором обнаруживается ошибка кратности gKJ -1 (d - кодовое расстояние) за счет учета стираний в каждом повторении кодовой комбинации. За счет использования стираний для обнаружения ошибок кратности g,-d -1 в устройстве удалось повысить вероятность обнаружения ошибок и уменьшить вероятность трансформации. 1 ил.

союз советских

СОЦИАЛИСТИЧЕСКИХ

РеспуБлик (ч)л Н 03 M 13/00

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) 093НИ

ТГИ1 1 t 1F fl fс Р Д

1ОТЕНЯ, ОПИСАНИЕ ИЗОБРЕТЕН

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4911219/24 (22) 13.02.91 (46) 30.07.93. Бюл. М 28 (72) Q.Н.Жуков, О,П.Малофей, В.Г.Резинько и В.H.Øåâ÷åíêî (56) Авторское свидетельство СССР

М 1374434, кл. Н 03 Н 13/02, 25.08. 86.

Авторское свидетельство СССР

N 1077050, кл. Н 03 Н 13/00, 9.11,82, Авторское свидетельство СССР

М 634469, кл. Н 03 M 13/02, 13.05.77. (54) УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ

ОШИБОК В КОДОВОЙ КОМБИНАЦИИ (57) Изобретение относится к электросвязи и может быть использовано в системах пеИзобретение относится к электросвязи и может быть использовано в системах передачи дискретной информации с решающей обратной связью.

Целью изобретения является повышение вероятности обнаружения ошибки.

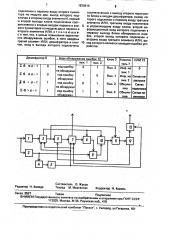

На чертеже изображена блок-схема предлагаемого устройства.

Устройство содержит пороговые блоки

1 и 2, ключ 3, элементы ИЛИ 6, 11, 13, счетчик 4, дешифратор 5, накопитель 7, сумматоры 8, 10 по модулю два, элемент И 9, блок

12 обнаружения ошибок.

Входы пороговых блоков 1,2 соединены со входом устройства. первым выходом которого является выход накопителя 7, а вторым выходом — выход элемента ИЛИ 13.

Выход порогового блока 1 подключен ко входу ключа 3, первый выход которого подключен к первым входам сумматоров 8, 10 по модулю два. Второй выход ключа 3 подключен к первым входам элементов ИЛИ 6, 11. Выход порогового блока 2 подключен к

„„5lj „„183061 6 А1 редачи дискретной информации с решающей обратной связью. Цель изобретения— повышение вероятности обнаружения ошибки. Устройство дополнительно содержит счетчик, дешифратор, элемент ИЛИ, Вновь введенные элементы позволяют реализовать алгоритм, при котором обнаруживается ошибка кратности gkt - 1 (d — кодовое расстояние) за счет учета "стираний" в каждом повторении кодовой комбинации. За счет использованиг. "стираний" для обнаружения ошибок кратности g;d 1 в устройстве удалось повысить вероятность обнаружения ошибок и уменьшить вероятность трансформации. 1 ил, первому входу элемента И 9 и через последовательно соединенные счетчик 4 и дешифратор 5 — с третьим входом накопителя

7 и вторымц входами ключа 3 и элемента

ИЛИ 13, Первый выход блока 12 обнаружения ошибок подключен к первому входу элемента ИЛИ 13, а второй выход подключен к третьему входу ключа 3 и ко второму входу накопителя 7, выход которого подключен ко второму входу сумматора 8 по модулю два, . выход которого подключен ко второму входу элемента И 9, выход которого подключеч ко второму входу сумматора 10 по модулю два, выход которого подключен ко вторым входам элемента ИЛИ 11 и ИЛИ 16, выходы которых подключены соответственно ко входу блока 12 обнаружения ошибок и к первому входу накопителя 7.

Все элементы и блоки известного устройства, за исключением ключа 3 и накопителя 7. функционируют без изменений, поэтому поясним назначение вновь введенных элементов, ключа 3 и накопителя 7.

Ключ 3 коммутирует информацию, поступающую с выхода порогового блока 1 на вход элемента ИЛИ 6. В случае, если «opîoàë комбинация принята с ошибками, но ее возможно испольэовать для исправления ошибок, па сигналам, поступающим от дешифратора 5 на второй и от блока 12 обнаружения ошибок на третий входы, ключ

3 коммутирует информацию с выхода порогового блока 1 на сумматоры 8 и 10 по модул,ю два.

Счетчик 4 подсчитывает количество сигналов стираний О, вырабатываемых пороговым блоком 2, которые свидетельству от о ненадежности принятых Элементов кодовой комбинации.

Дешифратор 5 служит для выдачи сигнала при превышении количества стираний

0 числ d-1, rpe d — кодовое расстояние.

Накопитель 7 предназначен для накап- 20 ления кодовой комбинации, поступающей с эломента ИЛИ 6, и ее выдачи па сигналам уйравления, поступающим на второй и третий входы От блока 12 обнаружения ошибок и дешифратора 5, на первый выход, являю- 25 щийся выходом устройства, или второй выход, соединенный с сумматором 8 r!o модулю два.

Назначение элемента ИЛИ 13 не требует пояснений, 30 .Вновь введенные элементы могут быть реализованы на стандартных микросхемах, выпускаемых отечественной промышленностью.

Устройство работает следующим абра- "В

ЗОМ.

Счетчик 4 и накопитель 7 обнулены, ключ 3 скоммутираван на второй выход, устройство синхронизирована са входным информационным потокам. Счетчик 4 обнулчется перед каждым повторам кодовой комбинации.

Принимаемая кодовая комбинация со входа устройства поступает на пороговые блоки 1 и 2, Пороговый блок 1 атождествля- 45 ет элементы Х2 кодовой комбинации с 0 или

1, сравнивая их с порогом По, т.е, реализует правила

1, Х > >Ho, O,Х <По

Пороговый блок 2 выносит решение а качестве принимаемого символа Xi и„если он не мажет быть дастатачнО точна Отождествлен с 0 или 1, выдает сигнал стирания 6. "àêèì

Образам,реализуется правила

)(, О,Г)1 <А <П2, (О, П1 > Х или Xi > П2 где П1 и П2 — уровни порогов, причем П1 <

<ПО < П2 и П2-ПО = ПО-П1, С выхода порогового блока 1 комбинация в виде последовательности нулей и единиц через ключ 3 и элемент ИЛИ 6 записывается в накопитель 7, а через элемент ИЛИ 11 комбинация вводится в блок

12 обнаружения ошибок. Одновременно счетчик 4 подсчитывает количества сигналов стираний 9, соответствующих некачественным элементам принимаемой кодовой комбинации, По синхраимпульсу окончания кодовой комбинации: в случае Х 6l > d-1 появляется сигнал на выходе дешифратора

5; в случае обнаружения ошибки блоком 12 обнаружения ошибок сигнал появляется на первом выходе блока 12, в противном случае — на втором (см. таблицу).

В там случае, когда по окончании приема кодовой комбинации дешифратор 5 выдает сигнал, свидетельствующий о там, что

Х Я > d-1, ктпач 3 остается скоммутированным на отарой выход, информация из накопителя 7 стирается, а через элемент ИЛИ 13 проходит сигнал переспроса на повторную передачу. Таким образам, при 7 6l > d-1 предполагается, чта возможна ошибка, превыша ащая обнаружива ащую способность када. И, независимо от результата поиска ошибок кодам, формируется.- сигнал переспроса, а комбинация; в которой предполагается ошибка кратности больше d-1, стирается, т.к, при исправлении такой комбинации повышается вероятность ошибки (вероятность трансформации). Прием кодовой комбинации начинается сначала.

Если блок 12 Обнаружения ошибок не обнаруживает ошибок в кодовой комбинации и Х Я < d-1, то считается, что кодовая комбинация принята без ошибок. В этом случае клепач 3 остается скоммутированным на выход 2, с выхода элемента ИЛИ 13 сигнал переспроса не формируется, а информация из накопителя 7 выдается на первый выход устройства.

Если блок 12 обнаружения ошибок обнаружил ошибку в кодовой комбинации, а

Z Я < d-1, то считается, что кодовая комб!лнация принята с Ошибкой MBlioA Kp3THOсти и мажет быть использована при исправлении ошибок ва втором повторе кодовой комбинации. В этом случае ключ 3 перекл очается на первый выход, связанный с сумматорами 8 и 10 по модулю два, с выхода элемента ИЛИ 13 формируется сигнал переспроса, а накопитель 7 переключается на второй выход, связанный с сумматором 8 па модулю два. Принятая комбинация второго повторения с первого вы1830616 хода ключа 3 через сумматор 10 по модулю два и элемент ИЛИ 6. осуществляя последовательный сдвиг содержимого накопителя 7 в сумматор 8 по модулю два, записывается в накопитель 7, а через элемент ИЛИ 11 5 поступает в блок 12 обна 1ужения ошибок.

Счетчик 4 аналогично в шеописанному подсчитывает количество игналов стирания Я, соответствующих эл ментам второго повторения. Если код не о "обнаружил ошибку 10 и Х Я d-1, то информ," сия иэ накопителя

7 поступает на выход устройства, B случае, когда Х Я > 0-1, устройство работает аналогично описанному выше. Для уменьшения числа потерь, возникающих в случае 15 искажения обоих повторений (Z Q d-1), обеспечивается исправление ошибки во втором повторении комбинации, Для этого при приеме второго повторения на сумматоре 8 по модулю два происходит поразряд- 20 ное сравнение обеих комбинаций при одновременном выявлении пороговым блоком 2 ненадежных элементов (стираний) второго повторения, Результат сравнения поступает на элемент И 9, на который также 25 выда1отся сигналы стирания, формируемые. пороговым блоком 2. Инвертирование разрядов комбинации второго повторения на сумматоре 10 по модулю два происходит в том случае, когда на первом и втором входах ЗО элемента И 9 одновременно появляются сигнал несовпадения двух повторений, формируемый сумматором 8 по модулю два, и сигнал стирания Я, выявленный пороговым блоком 2. В абсолютном большинстве З5 случаев (при Z о1 < d-1 в обоих повторах) это соответствует исправлению искажений комбинации, Таким образом, при использовании сигналов стираний О во всех повторениях кодо- 40 вой комбинации для обнаружения ошибок, удалось значительно повысить вероятности обнаружения ошибки и снизить вероятность трансформации за счет обнаружения ошибок кратности больше d-1.. 45

Оценим технико-экономическую эффективность предлагаемого устройства по сравнению с известным.

Вероятность обнаружения ошибки в известном устройстве Роо определяется обна- 50 руживающей способностью кода и равна где Ркод — вероятность обнаружения ошибок кодом;

Ро —. вероятность искажения элементарного символа;

d — кодовое расстояние; и — длина кодовой комбинации.

Вероятность обнаружения ошибки в ф предлагаемом устройстве Роо определяется обнаруживающей способностью кода и дополнительной обнаруживающей способностью при помощи подсчета сигналов 6I от детектора качества (порогового блока 2) и равна

d-1

Р..*=Р..д+Рд,= g x

I=1 и х Сп Po (1-Po)" + g X

i — d где Рдк — вероятность того, что при искажении не менее d элементарных символов появится не менее d сигналов стирания 1л;

Рпо — вероятность правильного стирания, т.е, вероятность появления сигнала 61 при условии, что элементарный символ искажен.

Таким образом, выигрыш оценивается следующим соотношением

Pop * Ркод + Рдк Рдк

Роо Ркод Ркод

Из(1) и(2) следует,что Р" > О, откуда

Ркод ф>1.

Следовательно, вероятность обнаружения ошибки в предлагаемом устройстве больше, чем в известном.

Формула изобретения

Устройство для исправления ошибок в кодовой комбинации, содержащее первый и второй пороговые блоки, входы которых объединены и являются информационным входом устройства, выходы первого и второго пороговых блоков подключены соответственно к первому информационному входу ключа и первому входу элемента И, выход которого подключен к первому входу первого сумматора по модулю два, выход которого подключен к первым входам первого и второго элементов ИЛИ, выходы которых подключены соответственно к первому sxoду накопителя и входу блока обнаружения ошибок, первый выход которого соединен с вторым входом накопителя, первый выход которого является информационным выходом устройства, второй выход накопителя

18306

Составитель О.Жуков

Техред М. Моргентал Корректор Н. Король

Редактор Н. Коляда

Заказ 2627 Тираж Подписное

ВНИИПИ. Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва. Ж 35, Раушская наб., 4/5

Производственно-издательский комбинат ".Патент", г. Ужгород, ул.Гагарина, 101 подключен к первому входу второго сумматора по модулю два, выход которого подключен к второму входу элемента И, первый и второй выходы ключа подключены соответственно к вторым входам первого и вто- 5 рого сумматоров по модулю два и первого и второго элементов ИЛИ, о т л и ч а ю щ е ес я тем, что, с целью повышения вероятности обнаружения ошибки, в него введены третий элемент ИЛИ., дешифратора и счет- 10 чик, вход и выходы которого подключены

16 8

/ соответственно к выходу второго порогового блока и входам дешифратора, выход которого подключен к первому входу третьего элемента ИЛИ, третьему входу накопителя и управляющему входу ключа, второй информационный вход которого подключен к первому выходу блока обнаружения ошибок, второй выход которого подключен к второму входу третьего элемента ИЛИ. выход которого является выходом ошибки устройства.