Селектор импульсов

Иллюстрации

Показать всеРеферат

Применение: изобретение откосится к импульсной технике, а именно к устройствам длл селекции последовательностей пар импульсов. Сущность изобретения: устройство содержит генератор, элемент НЕ, два блока памяти, три ключа, два формирователя коротких импульсов, элемент задержки, элемент И, компаратор, вычитатель, триггер , схему защелки, логический комбинационный элемент с соответствующими сзязами. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5пз Н 03 К 5/26

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) списочник H3QEpETEHUI(Иветта

IIEH93- f

Б 1БЛИОТЕи, ;

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4856555/21 (22) 02.08.90 (46) 30.07.93, Бюл, М 28 (71) Всесоюзный нефтегазовый научно-исследовательский институт (72) В.В.Балакин и В.А,Смирнов (56) Авторское свидетельство СССР

М 1190505, кл. Н 03 К 5/26, 1983.

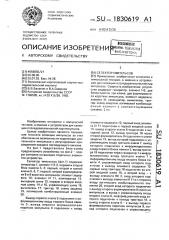

Изобретение относится к импульсной технике, а именно к устройствам для селекции последовательностей пар импульсов, Целью изобретения является повышение точности селекции импульсов за счет обеспечения возможности корреляции длительности импульсов с регулируемым приращением каждого последующего сигнала, На фиг.1 представлена блок-схема предлагаемого устройства; на фиг.2 — зпюры сигналов на выходах отдельных элементов устройства.

Селектор импульсов (фиг.1) содержит генератор 1, элемент НЕ 2, первый и второй блок памяти 3, 4; первый, второй и третий ключи 5, 6, 7; первый, второй формирователи 8 и 9 коротких импульсов; элемент задержки 10; элемент И 11, компаратор 12, выходную шину 13, первую и вторую входные шины 14 и 15, управляющую шину 16, вычитатель 17, триггер 18, схему защелки

19, логический комбинационный элемент

20.

Выход первого ключа 5 подключен к информационному входу первого блока памяти 3, выход первого формирователя коротких импульсов 8 подключен к входу!

Ж 1 83Î619 А1 (54) СЕЛЕКТОР ИМПУЛЬСОВ (57) Применение: изобретение относится к импульсной технике, а именно к устройствам длл селекции последовательностей пар импульсов, Сущность изобретения. устройство содержит генератор, элемент НЕ, два блока памяти, три ключа, два формирователя коротких импульсов, элемент задержки, элемент И, компаратор, вычитатель, триггер, схему защелки, логический комбинационный элемент с соответствующими связами. 2 ил, элемента задержки 10, первый вход элемента И 11 подключен к первой входной шине

14, выход второго ключа 6 подключен к выходной шине 13, вь|ход триггера 18 через второй формирователь 9 подключен к схеме защелки 19, выход которой подключен к управляющему входу третьего ключа 7, выход которого подключен к информационному входу первого блока памяти 3, выход триггера 18 подключен через генератор 1 к информационному входу третьего ключа 7 и информационному входу второго блока памяти 4, управляющий вход которого подкл очен к выходу элемента задержки 10, первый вход триггера 18 подключен ко вто. рой входной шине 15, а второй вход — к выходу элемента НЕ 2, вход которого подключен к выходу элемента И 11 и к первому входу логического комбинационного элемента 20, второй вход которого подключен к выходу второго формирователя 9 коротких импульсов, а выход к управляющему входу второго ключа 6, информационный вход которого подключен к выходу триггера 18, а выход второго ключа 6 — к выходу первого формирователя коротких импульсов 8,, выход которого подключен к управляющему

1830619

3 входу первого ключа 5, выход первого блока памяти З,подключен к первому входу вычитателя 17, второй вход короткого подключен к информационному входу nepaoro ключа 5 и к выходу второго блока памяти 4, а выход — к первому входу компаратора 12, второй вход которого подключен к управляющей шине 16, а выход — к второму входу элемента

И 11.

Устройство работает следующим образом. В момент включения путем подачи сигналов по шине "Сброс" происходит обнуление триггера 18, блоков памяти 3, 4 и на выходе элемента защелки 19 — "1".

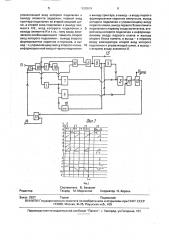

На фиг.фприведены временные диаг- 15 раммы, поясняющие работу устройства.

2 а, б — импульсы на входе первой и второй входной шине;

2 в — на выходе триггера;

2 г — ка выходе генератора;

2 д — на выходе первого формирователя коротких импульсов;

2 е — на выходе схемы защелки„

2 ж — на выходе третьего ключа;

2 з — на выходе второго блока памяти;

2 и — на выходе второго ключа;

2 к — нз выходе первого формирователя коротких импульсов, 2 л — на выходе первого ключа, 2 м — на выходе первого блока памяти; 30

2 н — на выходе вычитатепя, 2 о — на выходе компаратора.

Сигнал, поступающий на первый вход триггера 18, перебрасывает его в "1" (по переднему фронту) t>, фиг.2в, запуская тем 35 самым генератор 1, В случае, если это первый импульс в работе устройства, то информация с генератора 1 — значение амплитуды одновременно записывается в первый блок памяти 3 через третий ключ 7, так как на 40 выходе 19 — "1" и во второй блок памяти 4; анализируется в схеме вычитатепя:17 и сравнивается со значением заданного порога в компараторе 12. Значение заданного регулируемого порога выражено в аналого- 46 вом виде, равное U<, задается оператором, эквивалент длительности заданного порога для проведения корреляции длительности импульса. В случае, если результирующая величина меньше, чем "-О у", на выходе 12 60 — "0" (ц+4) фиг.2о в противном случае — "1".

Второй импульс в первой пачке по переднему фронту через элементы 11,2 перебрасывает триггер 18 в "О" состояние, на выходе элемента 9 появляется сигнал, пере- 56 брасывающий элемент 19 в "0" состояние, запрещающий прохождение сигнала через

6 в 3, На выходе устройства-сигнал, равный длительности между передними фронтами первого и второго импульсов, Регистрирующий импульс задним фронтом через первый формирователь коротких импульсов переписывает информацию из блока памяти 4 в 3 через 10, обнуляет второй блок памяти 4 и система готова к приему следующей пачки информации. Информация, записанная в первом блоке памяти 3, после каждого цикла является базовой для всей системы. В случае, если величина больше, чем Ucr, To процессом передачи информации управляет формирователь импульса

9. Если на выходе устройства поступает не первая пачка, то информация, записывае-. мая в блок памяти 4, анализируется с предыдущей информацией, записанной в блоке памяти 3, в вычитателе 17, далее алгоритм повторяется как и в случае первой пачки импульсов, В случае, если в пачке нет первого импульса, то устройство не отреагирует и на второй.

В случае, если отсутствует второй импульс в пачке, то процессом передачи информации управляют элементы 17, 12, 11, 20. В качестве логического комбинационного элемента 20 используется элемент, работающий по следующему алгоритму; вх1 11 00

Bx„01 01 =p вх2 вх2 $ вх1 вых0111

Формула изобретения

Селектор импульсов, содержащий гекератор, элемент НЕ, первый и второй блоки памяти, первый, второй и третий ключи, первый и второй формирователи коротких импульсов, элемент задержки, элемент И, компаратор, причем выход первого ключа подключен к информационному входу первого блока памяти, выход первого формирователя коротких импульсов подключен к входу элемента задержки, первый вход элемента:И подключен к первой входной шине, выход второго ключа подключен к выходной шине, а также вторую входную шину и управляющую шину, о тли ч а ю щ ий с ятем, что, с целью повышения точности селекции, в него введены вычитатель, триггер, схема защелки и логический комбинационный элемент, причем генератор выполнен в виде генератора пилообразного напряжения, выход триггера через второй формирователь коротких импульсов подключен к схеме защелки, выход которой подключен к управляющему входу третьего ключа, выход которого подключен к информационному входу первого блока памяти, выходтриггера подключен через генератор к информационному входу третьего ключа и информационному входу второго блока памяти, 1830619

9 a Z

Составитель В. Балакин

Техред M. Mo ргентал

Корректор H. Король

Редактор

Заказ 2527 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб.. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101 управляющий вход которого подключен к выходу элемента задержки, первый вход триггера подключен ко второй входной шине, а второй вход подключен к выходу элемента НЕ, вход которого подключен к выходу элемента И и к пь, лому входу логического комбинационного лемента, второй вход которого подключен выходу второго формирователя коротких импульсов, а выход- к управляющему входу второго клокоча, информационный вход которого подключен к выходу триггера, а выход — к входу первого формирователя коротких импульсов, выход которого подключен к управляющему входу первого ключа, выход первого блока памяти

5 подключен к первому входу вычитателя, второй вход которого подключен к информационному входу первого ключа и выходу второго блока памяти, а выход — к первому входу компаратора второй вход которого

10 подключен к управляющей шине, а выход— к второму входу элемента И,