Резервированное устройство

Иллюстрации

Показать всеРеферат

Использование: при построении высоконадежных систем на основе резервируемых блоков ЭВМ, осуществляющих выполнение задач по разным программным и аппаратным версиям. Сущность изобретения: устройство содержит; 4 резервируемых блока (1,2,3,4), 4 схемы сравнения (7,8,9,10), 1 элемент ИЛИ-НЕ(15), 1 выходной регистр

СОЮЗ СОВЕТСКИХ

ЕОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4926419/24 (22) 08.04.91 (46) 15.08.93. Бюл. М 30 (71) Производственное обьединение "Харьковский завод электроаппаратуры" (72) В.С.Харченко, Б.О.Сперанский, Г.Н.Тимонькин, В.Г,Литвиненко, В.С.Бугай и С.Н;Ткаченко (56) Авторское свидетельство СССР

hL 1390612, кл. G 06 F 11/16, 1988.

Авторское свидетельство СССР

N. 1624456, кл. G 06 F 11/18, 1991, „„5U„„1833877 А1 (ю!)з G 06 F 11/18, Н 05 К 10/00 (54) РЕЗЕРВИРОВАННОЕ УСТРОЙСТВО (57) Использование: при построении высоконадежных систем на основе резервируемых блоков ЭВМ, осуществляющих выполнение задач по разным программным и аппаратным версиям. Сущность изобретения: устройство содержит: 4 резервируемых блока (1,2,3,4). 4 схемы сравнения (7,8,9,10), 1 элемент ИЛИ-НЕ (15), 1 выходной регистр (5), 1 коммутатор (6), 3 триггера (11,12.13), 1 элемент И-НЕ (14), 2 входа (21,16), 4 выхода (17,18,19,20). 16-1-7-15-14-11-18, 16-2-7-6-517, 16-3-8-15-.5, 16-4-8-12-19, 21-1-9-14-1320, 21-2-10-14-12, 21-3-9, 21-4-10, 1-6, 3-6, 7 11 8 6 21-5, 21-11, 21-1.2, 21-13, 1 ил.

1833877 — выход отказа первого подканала устройства, 19 — выход отказа второго подканалов, 20 — выход наличия дефекта проектирования устройства, 21 — вход синхронизации устройства, Первый 1 — четвертый 4 резервируемые блоки предназначены для вычисления зада55

Изабретение относится к области цифровой вычислительной техники и автоматики и может быть использовано при построении высоконадежных систем повышенной надежности и достоверности на основе резервируемых блоков (ЭВМ), осуществляющих выполнение задач по разным программным и аппаратным версиям.

Цель изобретения — повышение достоверности контроля устройства. 10

Сущность изобретения состоит в увеличении достоверности контроля путем: а) реализации резервируемых блоков .каждого из подканалов устройства по различным программно и (или) аппаратным версиям, что дает возможность выявлять де- фекты, допущенные при проектировании и разработке и невыявленные при его отладке; б) выявления дефектов проектирования 20 на основе введения и аппаратной реализации дополнительной операции сравнения выходов резервируемых блоков различных подканалов, выполненных по одинаковым программно-аппаратным версиям.

Сущность изобретения реализуется путем введения следующих новых элементов и связей, Введение третьего и четвертого элементов сравнения, элемента И-НЕ и обуслов- 30 ленных ими связей необходимо для идентификации проявившегося ДП, Введение первого и второго триггеров и обусловленных ими связей необходимо для фиксации такого состояния устройства, при котором первый и (или) второй подканалы соответственно признаны отказавшими.

Введение третьего триггера и обусловленных им связей необходимо для фиксации такого состояния устройства, при 40 котором было обнаружено искажение выходных данных, вызванное проявлением

ДП.

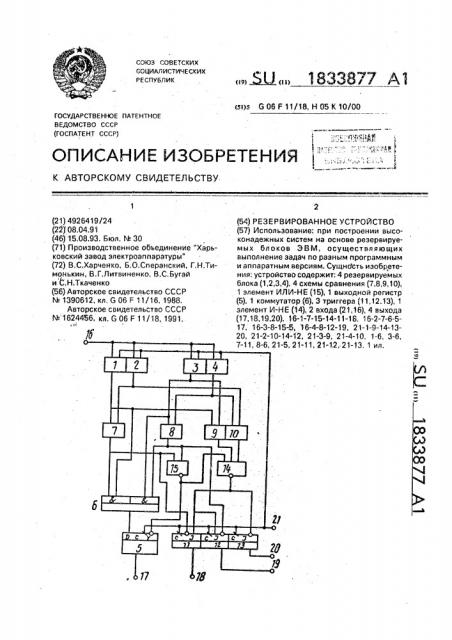

На чертеже представлена функциональная схема резервированного устройства. 45

На чертеже использованы следующие обозначения: 1-4 — первый-четвертый резервируемые блоки, 5 — выходной регистр, 6 — коммутатор, 7 — 10 — первую-четвертую схемы сравнения, 11-13 — первый-третий 50 триггеры, 14 — элемент И-НЕ, 15 — элемент

ИЛИ-НЕ, 16 — информационный вход устройства, 17 — вьгход данных устройства, 18 чи (пакета задач) с жестким периодом счета не более Т, либо для циклического решения одной задачи с постоянно обновляемыми данными (например, в системе управления летательного аппарата). Первый 1 и третий

3 резервируемые блоки выполняются по единой программно-аппаратной версии.

Второй 2 и четвертый 4 — также по единой версии, однако, отличной от версии первого

1 и третьего 3 блоков. Таким образом, резервируемые блоки, представляющие один подканал устройства, оказываются выполненными по различным программно-аппаратным версиям, так как первый подканал составляют первый 1 и второй 2 резервируемые блоки, а второй подканал — третий 3 и четвертый 4.

Регистр 5 предназначен для временного хранения данных, поступающих на выход 17 данных устройства.

Коммутатор 6 предназначен для коммутации на информационный вход регистра 6 выходов первого 1 и третьего 3 резервируемых блоков в случае совпадения данных на выходах блоков первого и второго подканалов соответственно.

Первая 7 (вторая 8) схемы сравнения предназначены для сравнения данных, поступающих с выходов резервируемых блоков первого (второго) подканала, т.е., с .выходов первого 1 (третьего 3) и второго 2 (четвертого 4) резервируемых блоков, а также для управления первым (вторым) информационным входом коммутатора 6.

Третья 9 (четвертая 10) схемы сравнения предназначен для сравнения данных, поступающих с выходов первого 1 и третьего 3 (второго 2 и четвертого 4) резервируемых блоков, выполненных по идентичным программно-аппаратным версиям.

Первый 11 и второй 12 триггеры предназначены для фиксации отказа первого и второго подканалов соответственно.

Третий 13 триггер предназначен для фиксации обнаружения ДП.

Элемент И-НЕ 14 предназначен для идентификации состояния обнаружения

ДП

Элемент ИЛИ-НЕ предназначен для управления регистром 5 и элементом И-НЕ.

Устройство работает следующим образом.

В исходном состоянии все триггеры 11—

13 обнулены, в регистре 5 записаны одни нули, на.выходах данных всех резервируемых блоков 1 — 4 — нули, Выполнение задачи каждый из резервируемых блоков начинает по импульсу, поступающему на их синхровходы, а закончить должен к приходу очередного. Если эа время Т, равного периоду

1833877

55 следования импульсов, поступающих на вход 21 синхронизации устройства; выполнение задачи не закончено, то блок считается отказавшим. Итак, на все входы всех схем сравнения 7 — 10 поступают нули, — на их выходах единицы, Следовательно, на выходе элемента ИЛИ вЂ” НЕ будет нуль, разрешающий запись в регистр 5 и закрывающий элемент И-НЕ 14. На выходе элемента И-НЕ

14 будет единица, которая поступает на jвходы триггеров 11, 12 и инверсный вход триггера 13, запрещая изменение состояния последнего. Изменение состояния первого 11 и второго 12 триггера запрещают единицы, поступающие соответственно с выходов схем 7 и 8 сравнения на инверсные входы триггеров. Таким образом, по первому тактовому импульсу изменения состояния триггеров 11 — 13 не происходит, а в регистр 5 вновь записываются одни нули, так как на оба открытых входа коммутатора

6 поступают нули с выходов первого 1 и третьего резервируемых блоков.

Все четыре 1-4 резервируемых блока начинают решение одной задачи, с одними и теми же данными, поступающими со входа

16 устройства, по различным программным версиям. Закончить решение задачи блоки

1 — 4 в случае отсутствия ДП и отказов должны к моменту прихода очередного импульса со входа 21 синхронизации устройства, "выставив" нэ своих выходах результаты решения задачи.

Если за время Т отказов или сбоев ни в одном из резервируемых блоков 1 — 4 не произошло, и ДП не проявились, то к моменту прихода очередного импульса синхронизации на выходах всех блоков находятся идентичные данные. Таким образом, на выходах всех схем сравнения 7 — 10 будут единичные потенциалы. Следовательно, оба информа- ционных входа коммутатора 6 будут открыты, и данные с выходов первого 1 и третьего

3 резервируемых блоков, объединяясь "по

ИЛИ" беэ искажений, поступают на информационный вход регистра 5, Нуль с выхода

ИЛИ-НЕ 15 разрешает запись в регистр 5 и по прежнему блокирует элемент И-НЕ 14, блокируя изменение состояния триггера 13.

Очередной синхроимпульс, поступивший со входа 21, запишет в регистр 5 результаты решения первой задачи и инициирует начало решения очередной, поступая на входы синхронизации резервируемых блоков 1-4.

Состояния триггеров 11-13 не изменяются.

Далее устройство работает аналогично до тех пор, пока не возникнет отказ какого-либо иэ блоков 1-4, или не проявится ДП в одной иэ программно-аппаратных версий.

Рассмотрим последовательно оба случая.

Допустим, возник отказ в первом резервируемом блоке 1, Тогда к моменту.прихода очередного тактового импульса на выходе первого элемента сравнения 7 будет нуль, который блокирует первый информационный вход коммутатора 6, запрещая тем самым прохождение данных с выхода первого резервируемого блока 1 на вход регистра 5, Следовательно, на информационный вход регистра 5 поступят данные с выхода третьего резервируемого блока 3, данные с выхода которого совпали с данными на выходе четвертого резервируемого блока 4, Аналогичные события произойдут и при отказе второго резервируемого блока 2. Таким образом, к моменту прихода очередного тактового импульса нэ информационном входе регистра 5 находятся данные с выхода второго подканала, так как один иэ блоков первого подканала отказал (идентифицировать какой именно невозможно), кроме того на инверсный J-вход первого триггера 11 поступает нуль с выхода схемы сравнения 7, на его прямой J-вход поступает единица с выхода элемента И-НЕ 14, ведь на двух его входах будут нули: один с выхода схемы сравнения 9, а другой — с выхода ИЛИ-НЕ

"15. Следовательно, по очередному тактовому импульсу в регистр 5 запишутся данные с выхода третьего резервируемого блока, а триггер 11 перейдет в единичное состояние, выдавая на выход 18 отказа первого подканала устройства сигнал об отказе иэ.блоков первого подканала: первого 1.или второго 2 резервируемых блоков.

В случае отказа одного из блоков второго подка нала, то есть третьего 3 и четвертого

4 резервируемых блоков устройство работает аналогично, с той лишь разницей, что данные в регистр 5 записываются с выхода первого резервируемого блока 1, так как второй вход коммутатора блокируется нулем, поступающим с выхода схемы сравнения 8; в единичное же состояние переходит второй триггер 12, сигнализируя об отказе второго подканала, выдавая на выход 19 устройства единичный потенциал.

В случае отказа еще одного из резервируемых блоков возможно два варианта, в зависимости от того в каком из подканалов произошел второй отказ.

Допустим, при первом отказавшем блоке 1 в первом подканале отказал и второй резервируемый блок 2, причем данные на их выходах по-прежнему не совпадают. В этом случае никаких изменений не происходит, и устройство продолжает работать аналогично, по выше описанному алгоритму.

Если же при наличии отказавшего блока в первом подканале, отказал один иэ блоков

1833877 второго подканала (или наоборот), то тогда к моменту прихода очередного тактового импульса на выходах всех четырех схем сравнения 7-10 будут нули, оба входа коммутатора 6 закрыты, на выходе элемента

ИЛИ-HE 15 появится единица, запрещающая запись в регистр 5, на входах же элемента И-НЕ 14 будут нули (с выходов схем сравнения 9, 10), Следовательно, очередной импульс переведет в единичное состояние уже оба триггера 11 и 12, сигнализируя об отказе устройства в целом, сохраняя на выходе 17 данных последнюю достоверную информацию. После этого дальнейшая эксплуатация устройства невозможна до устранения возникших неисправностей хотя бы в одном из подканалов.

Рассмотрим теперь работу устройства при обнаружении ДП. В случае исправности всех резервируемых блоков устройства способна обнаруживать искажения выходных данных, вызванные проявляющимися ДП аппаратных и программных средств резервируемых блоков. Так как блоки одного подканала выполнены по различным програмно-аппаратным версиям, то проявление ДП в каждой версии будет индивидуальным. Таким образом, вероятность того, что в обоих версиях допущены идентичные

ДП, да и еще проявляющиеся одинакова, черезвычайно мала. Следовательно, проявление ДП в одном из блоков подканала приведет к несовпадению данных на входах схем сравнения 7 и 8, оба входа коммутатора 6 будут закрыты, Однако, сравнение данных на входах схем сравнения 9 и 10 даст положительный результат, так как эти элементы сравнивают выходы блоков, реализованных по идентичным программноаппаратным версиям, а следовательно ДП проявятся идентично. Таким образом, на всех входах элемента И-HE 14 будут единицы. Нуль с выхода этого элемента блокирует изменение триггеров 11, 12, исключая ложную оценку состояния устройства, но изменение триггера 13 становится возможным и происходит по очередному синхроимпульсу, который переводит этот триггер в единичное состояние и записывает в регистр 5 одни нули, На выходе 20 наличия ДП появляется единичный потенциал, сигнализирующий о том, что при решении данной задачи проявился ДП в одной из версий. Тем самым исключается выдача ложных данных на выход 17 данных устройства.

В случае, если ДП проявился при наличии в устройстве отказавшего подканала, либо одновременно с отказом одного из

30 схемы сравнения, выход третьего резерви35

45

5

20 блоков то выявление. такого события в данном цикле решения задачи невозможно, и оно идентифицируется как отказ обоих подканалов.

Формула изобретения

Резервированное устройство, содержащее первый-четвертый резервируемые блоки, первую-третью схемы сравнения, элемент И-НЕ и коммутатор, выходы первого и второго резервируемых блоков подключены к первому и второму входам соответственно первой схемы сравнения, а выход третьего резервируемого блока к первым входам второй и третьей схем сравнения, второй вход последней из которых соединен с выходом первого резервируемого блока, причем информационный и синхронизирующий входы каждого из четырех резервируемых блоков подключены к одноименным входам устройства, а выход третьей схемы сравнения соединен с первым входом элемента И-НЕ, о т л и ч а ющ е е с я тем, что, оно содержит четвертую схему сравнения, элемент ИЛИ-НЕ, выходной регистр и первый-третий триггеры, выход первого резервируемого блока подключен к первому информационному входу коммутатора, выход второго резервируемого блока — к первому входу четвертой руемого блока —. второму информационному входу коммутатора, а выход четвертого резервируемого блока — к вторым входам второй и четвертой схем сравнения, выход первой схемы сравнения соединен с первым управляющим входом коммутатора, с инверсным информационным входом первого триггера и с первым входом элемента

ИЛИ-НЕ. второй вход которого подключен к выходу второй схемы сравнения, к второму управляющему входу коммутатора и инверсному информационному входу второго триггера. а выход — к входу блокировки выходного регистра и второму входу элемента

И-НЕ, соединенного третьим входом с выходом четвертой схемы сравнения, а выходом — с прямыми информационными входами первого и второго триггеров и с инверсным информационным входом третьего триггера, выход коммутатора соединен с управляющим входом выходного регистра, выходы первого-третьего триггеров являются выходами сигналов результатов контроля устройства, их синхронизирующие входы соединены с одноименными входами устройства и выходного регистра, выход которого является выходом данных устройства.