Устройство для управления высоковольтным силовым транзистором

Иллюстрации

Показать всеРеферат

Сущность изобретения: устройство содержит оптронный элемент гальванической развязки 1, каскады промежуточного усиления 2, защиты 4 и блокировки 5, выполненные в виде компараторов, транзисторный усилитель мощности 3,двухполярный источник питания 6, клеммы 7, 8, 9 для подключения силового транзистора и клеммы для подачи сигнала управления 10, 11. В безаварийном режиме импульсы управления после элемента гальванической развязки проходит двойное усиление в промежуточном каскаде и транзисторном усилителе мощности и поступают на базу силового транзистора . Если управляющий импульс поступает в момент, когда через обратный диод, включенный параллельно силовому транзистору, еще протекает ток, каскад блокировки вносит задержку импульса управления до момента спадания тока до нуля, тем самым препятствуя протеканию инверсного тока через силовой транзистор. Если в момент прохождения импульса управления происходит перегрузка силового транзистора по току, приводящая его к выходу из режима насыщения , происходит срабатывание каскада защиты, который блокирует импульсы управления на время, задаваемое его внутренней RC-цепью. При сохранении перегрузки защита работает в режиме автоматического повторного включения. Устройство имеет простую перестройку функций защиты: с защелкой или укорачиванием импульса управления и кроме того, осуществляет контроль от снижения собственного отрицательного уровня питания. 4 з.п.ф-лы, 1 ил. (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ПАТЕНТУ

- А е (21) 4948928/07 (22) 25.06.91 (46) 15.08.93. Бюл, ¹ 30 (71) Филиал Всесоюзного научно-исследовательскоГО института электромеханики (72) С.Н.Болдырев (73) Филиал Всесоюзного научно-исследовательского института электромеханики (56) Электронная техника в автоматике, ¹ 9, М., Советское радио, 1977, с. 57.

Патент CLLIA ¹ 4б80664, кл. Н 02 Н 3/04, 1987.

Патент ФРГ ¹ 3522429, кл. В 02 M 3/155, 1985. (54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ВЫСОКОВОЛЬТНЫМ СИЛОВЫМ ТРАНЗИСТОРОМ (57) Сущность изобретения; устройство содер>кит оптронный элемент гальванической развязки 1, каскады промежуточного усиления 2, защиты 4 и блокировки 5, выполненные в виде компараторов, транзисторный усилитель мощности 3, двухполярный источник питания б, клеммы 7, 8, 9 для подключения силового транзистора и клеммы для подачи сигнала управления 10, 11. В безаваИзобретение относится к преобразовательной технике и может быть использовано в транзисторных инверторах и преобразователях посеянного напряжения.

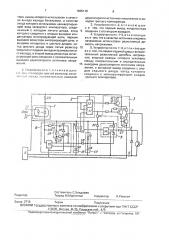

Цель изобретения: повышение надежности, которая достигается исключением триггеров, повышение быстродействия защиты, введением режима автоматического возврата в исходное состояние после срабатывания защиты от перегрузки, и блокиров. БЦ. 1835118 АЗ рийном режиме импульсы управления после элемента гальванической развязки проходит двойное усиление в промежуточном каскаде и транзисторном усилителе мощности и поступают на базу силового транзистора. Если управляющий импульс поступает в момент, когда через обратный диод, включенный параллельно силовому транзистору, еще протекает ток, каскад блокировки вносит задержку импульса управления до момента спадания тока до нуля, тем самым препятствуя протеканию инверсного тока ÷åрез силовой транзистор. Если в момент прохождения импульса управления происходит перегрузка силового транзистора по току, приводящая его к выходу из режима насыщения, происходит срабатывание каскада защиты, который блокирует импульсы управления на время, задаваемое его внутренней RC-цепью, При сохранении перегрузки защита работает в режиме автоматического повторного вкл|очения. Устройство имеет простую перестройку функций защиты: с защелкой ипи укорачиванием импульса управления и кроме того, осуществляет контроль от снижения собственного отрицательного уровня питания, 4 э.п,ф-лы, 1 ил. ке импульсов управления при снижении отрицательного уровня питания, На чертеже приведена электрическая схема управления.

Устройство уп ра вп ения высокг вол ьтным силовыми транзисторами содержит элемент гальванической развязки 1, например, оптрон, промежуточный каскад 2, усилитель мощности З,каскад защиты 44, каскад блокировки 5, двухпопярный исто чник питания б, клеммы для подключения силового

1835118

50

55 транзистора 7, 8, 9, клеммы для подключения сигнала управления 10, 11, четыре компзратора 12, 13, 14, 15, источник опорного напряжения 16, интегрирующую цепь 17, два конденсатора 18, 19, семь резисторов

20-26 и шесть диодов 27 — 32.

Клеммы для подключения сигнала управления 10, 11 соединены со входами элемента гальвзнической развязки 1, первый выход ко3орого соединен через первый резистор 20 с положительным выводом двухполярного источника питания L1 первыми входами первого 12 и второго 13 компараторов, промежуточного каскада 2, выходы которых соединены с первым и вторым входами усилителя мощности 3. выход которого соедин".í с, Yлеммой 7 для подключения баэовогс вывода силового транзистора.

Вт-с;!(:. выход элемента гальванической раза::.эки соединен с выходом четвертого кок:г(арз(орз 5 каскада защиты 4. шестым

25 и riT(3ðû÷ 2 l 3(3исторами. причем второй вывел ое 3:» i;>(! а >1 чер э первый конденсат(,(.,(соединен -. а3одом второго 28 и анодом . ре" ье- 29 диодов. Катод диода 29 с(„-"ди,,,е с неинвертирующим входом четв-:; то -ñ., (3мпзпзтора 15 и катодом четвертого, иг,, (а .1(ч àr!i)ä ко,орого соединен с ич егоир;л щей цепи 17 и анодам(; . .--.о(о 1", и шес(ого 32 диодов. Катод д."ела 32 через пятый резистор 24 соединен с Fûõoäî-.1 в орого компзратора 13, а катод пятого длод,. 31 соединен с неинвертирующим вхо,о 4 тре iüåãî компзраторз 14 каскада блокировки 5. первым выводом четве,3т(3го резистора 23 и анодом первого диода 27 катод которого соединен с клемк ой 8 для подключения коллектора силового транзистора. Выход третьего компаратора (4 соединен со вторыми входами первого 12 и второго 13 компзраторов, и через третий резистор 22 с выходом источника опорного (зпряжения 16 и инвертирующим входом четвеотогг компзраторз 15, выводь: питани" компзг.атооов 12. 33, 14, 15 и усилителя мощности 3 подключены к соответствующим выводам двухполярного источника питания 6, отрицательный вывод которого подключен также к аноду второго диода 28, а положительный ко вторым выводам резисторов 23, 25 и 26 интегрирующей цепи 17, источнику опорного напряжения 16, вторые выводы двух последних соединены с его общим выводом, инвертирующим входам третьего компаратора 14, и клеммой 9 для подключения эмиттера силового транзистора.

Устройство работает следующим образом, в исходном состоянии т.е. при включенном двухполярном источнике питания 6 и отсутствии управляющего импульса через первый резистор 20 на первые входы, инвертирующий и неинвертирующий соответственно, первого 12 и второго 13 компараторов поступает положительный уровень напряжения по величине больший, чем на их вторых входах, при этом на выходе первого компаратора 12 присутствует отрицательный, а на выходе второго компаратора 13 положительный сигналы. Транзистор

35 усилителя мощности 3 закрыт, а транзисторы 36 и 37 открыты, при этом на базе силового транзистора, клемма 7, устанавливается отрицательный уровень напряжения.

На выходе третьего компзратора 14 положительный уровень напряжения. Второй конденсатор 19 через шестой диод 32, резистор

24 и первый компаратор 12 заряжен до отрицательного потенциала. Четвертый компаратор 15 находится во включенном состоянии.

С приходом импульса управления фотодиод оптрона элемента гальванической развязки 1 переходит в проводящее состояние и потенциал напряжения на первых входах первого 12 и второго 13 компараторов становится меньше, чем на их вторых входах.

Компараторы переключаются, транзистор

35 усилителя мощности 3, переходит в проводящее состояние, транзисторы 36, 37 выключак3Tñë и силîBой транзистор открывается. При этом, величина напряжения на втором конденсаторе 19, интегрирующей цепи 17 становится равной сумме прямых падений напряжения пятого 31, первого 27 диодов и силового транзистора.

Выходное напряжение источника опорного напряжения 16 выбирается большей величины, поэтому четвертый компаратор 15 каскада защиты 4 остается во включенном состоянии. Если режим работы силового транзистора не меняется, то процессы повторя ются.

Если управляющий сигнал приходит в момент времени, когда через обратный диод, параллельный силовому транзистору, еще протекает ток, потенциал его коллектора относительно эмиттера становится отрицательным. При этом, потенциал напряжения на неинвертирующем входе. третьего компаратора 14, каскада блокировки 5, становится меньше, чем на его инвертирующем входе, На выходе компаратора 14 устанавливается отрицательный уровень напряжения. который накладывает блокировку по вторым входам компараторов 12, 13 на прохождение импульса управления, до тех пор, пока через обратный диод протекает ток. Отрицательный уровень напряжения на база-эмиттерном переходе

1835118

15

55 силового транзистора удерживает его в закрытом состоянии и препятствует протеканию инверсного тока.

В безаварийном режиме силовой трэнзистор находится в насыщенном состоянии и его прямое падение напряжения невелико. При перегрузке по току рабочий режим работы транзистора смещается в активную область, напряжение на его коллекторэмиттерном переходе увеличивается и вызывает увеличение напряжения на втором конденсаторе 19. В этот момент, когда напряжение на нем станет больше, чем на выходе источника опорного напряжения 16, четвертый компаратор 15, каскада защиты

4, выключается и обрывает цепь протекания тока через фотодиод оптрона элемента гальванической развязки 1,Первый 12 и второй 13 компараторы переключаются и к базе силового транзистора прикладывается отрицательный уровень напряжения, транзистор закрывается. Компаратор 15 находится в выключенном состоянии до тех пор, пока по цепи: "положительный вывод двухполярного источника питания, шестой 25, второй 21 резисторы, первый конденсатоо

18, третий диод 29 и вход компаратора 15" протекает ток. После чего, он переходит снова во включенное состояние, первый конденсатор 18 быстро разряжается через второй диод 28, резистор 21 и компаратор

15. Если перегрузка не устранилась, устройство работает в режиме автоматического повторного включения.

Если в устройстве закоротить первый конденсатор 18, то после режима перегрузки компаратор сработает. однократно, т.е. реализуется функция защиты с защелкой.

Если не устанавливать шестой резистор

25, то после режима перегрузки компаратор

15 будет находиться в выключенном состоянии только то время, пока присутствует импульс управления и фотодиод элемента гальванической развязки 1 находится в проводящем состоянии, т.е. реализуется функция защиты с укор ачи ванием им пул ьса.

При введении дополнительного резистивного делителя напряжения 38 и диода

3Q компаратор 15 выполняет вторую функцию зау иты — контроль уровней питания, так как при снижении (или пропадании) отрицательного уровня питания он также переходит в выключенное состояние и блокирует импульсы управления. Наиболее полезно эта функция проявляется в моменты подачи и снятия питания.

Формула изобретения

1. Устройство для управления высоковольтным силовым транзистором, содержащее клемму подключения базы силового транзистора, соединенную с выходом усилителя мощности, выполненного с первым и вторым входами подачи сигналов запирания и отпирания силового транзистора, соответственно соединенными с первым и вторым выходами промежуточного каскада соответственно, первый вход которого соединен с первым выводом первого резистора и первым выходом элемента гальванической развязки, входы которого соединены с клеммами подключения сигнала управления, а второй выход соединен с первым выводом второго резистора и выходом каскада защиты, каскад блокировки, выход которого соединен с вторым входом промежуточного каскада и первым выводом третьего резистора, первый диод, катод которого соединен с клеммой для подключения коллектора силового транзистора, а анод соединен с входом каскада блокировки и первым выводом четвертого резистора, второй вывод которого соединен с вторым выводом первого резистора, первым входом источника опорного напряжения и положительным выводом двухполярного источника питания, общий вывод которого соединен с клеммой подключения эмиттера силового транзистора и вторым входом источника опорного напряжения, а положительный и отрицательный выводы соединены с входами питания каскадов и усилителя мощности, пятыи резистор, конденсатор и интегрирующую цепь, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности, введены четыре компаратора и второй, третий, четвертый, пятый и шестой диоды, причем выходы первого и второго компараторов использованы в качестве первого и второго выходов промежуточного каскада, в качестве первого входа которого использованы соединенные первые разноименные входы первого и второго компараторов, соединенные вторые вхдды которых использованы в качестве второго входа промежуточного каскада, выход третьего компаратора использован в качестве выхода каскада защиты, соединенного через последовательно включенные второй резистор и конденсатор с катодом второго диода и анодом третьего диода, катод которого соединен с катодом четвертого диода и неинвертирующим Входом третьего компаратора, инвертирующий вход которого соединен с вторым выводом третьего резистора и выходом источника опорного напряжения, анод второго диода соединен с отрицательным выводом двухполярного источника напряжения, общий вывод которого соединен с первым выводом конденсатора интегрирующей цепи и инвертирующим входом четвертого компара1835118

2, Устройство no n. 1, о т л и ч а ю щ е ес я тем, что введен шестой резистор, вклю .:е.н.ый между положительным выводом

Составитель С.Болдырев

Тех ред M. M îð ãåíòàë Корректор Н.Ревская

Редактор

Заказ 2716 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва Ж-35 Раушскэя наб, 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101 тора, выход которого использован в качестве выхода каскада блокировки, в качестве входа которого использован неинвертирующий вход четвертого компаратора, соединенный с катодом пятого диода, анод 5 которого соединен с вторым выводом конденсатора интегрирующей цепи, первым выводом резистора интегрирующей цепи, и анодами четвертого и шестого диодов, катод шестого диода через пятый резистор 10 соединен с первым выходом. промежуточного каскада, а второй вывод резистора интегрирующей цепи соединен с положительным выводам двухполярного источника напряжения, 15 двухполярного источника напряжения и выходом третьего компаратора.

3, Устройство по и. 2, о т л и ч а ю щ е ес я тем, что первый вывод конденсатора соединен с его вторым выводом.

4. Устройство по пп. 1-3, о т л и ч а ю щ ее с я тем, что в качестве источника опорного напряжения использован резистивный делитель напряжения.

5, Устройство по пп. 1 — 4, о т л и ч а ю щ ее с я тем, что введен седьмой диод и вспомогательный резистивный делитель. напряжения, входные выводы которого включены между положительным и отрицательным выводами двухполярного источника напряжения, а выходной вывод соединен с анодом седьмого диода, катод которого соединен с неинвертирующим входом третьего компаратора.