Устройство для умножения частоты

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах автоматического управления различного назначения. Цель изобретения - повышение точности работы устройства. Устройство для умножения частоты содержит генератор тактовых импульсов , схему измерения периода, блок управления, первый двоичный умножитель и регистр, причем выход схемы измерения периода соединен с установочным входом блока управления, блок памяти, адресные входы которого соединены соответственно с разрядными выходами регистра, выходы блока памяти соединены соответственно с информационными входами первого двоичного умножителя. Новым в устройстве является соединение выхода первого двоичного умножителя с суммирующим входом реверсивного счетчика импульсов, вычитающий ёхрд которого соединен с выходом второго двоичного умножителя частоты и выходом устройства. При этом разрядные выходы реверсивного счетчика соединены с информационными входами второго двоичного умножителя, тактовый вход которого связан последовательно через элемент задержки с выходом генератора тактовых импульсов. 1 ил,

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 G 06 F 7/68

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ПАТЕНТУ (, Д ( (Ь

1 (21) 4943910/24 (22) 19.04.91 (46) 23.08.93. Бюл. hL 31 (71) Тамбовское высшее военное авиационное инженерное училище им. Ф.Э.ДзержинСКОГО (72) Е.А.Писклаков, A.È,eåñåíêî. В.М.Делик и А.Н.Пахомов (73) Тамбовское высшее военное авиационное инженерное училище им, Ф.Е.Дзержинского (56) Авторское свидетельство СССР

М 634277, кл. 6 06 F7/68,, 1 977.

Авторское свидетельство СССР

N. 928354,.кл. 6 06 F 7/68, 1980.

Авторское свидетельство СССР

М 1591011, кл, G 06 F 7/68, 1988. (54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧАСТОТЫ (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах автоматического управления различного назначения. Цель изобретения — повышение точности работы

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах автоматического управления различного назначения.

Цель изобретения — повышение точности работы устройства.

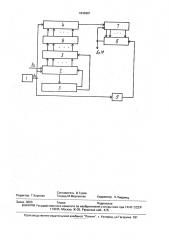

На чертеже приведена функциональная схема устройства.

Устройство для умножения частоты содержит генератор 1 тактовых импульсов, схему 2 измерения периода, блок 3 управления, первый двоичный умножитель 4, ре,„, Ж,„, 183бб81 А3 устройства. Устройство для умножения частоты содержит генератор тактовых импульсов, схему измерения периода, блок управления, первый двоичный умножитель и регистр, причем выход схемы измерения периода соединен с установочным входом блока управления, блок памяти, адресные входы кбторого соединены соответственно с разрядными выходами регистра, выходы блока памяти соединены соответственно с информационными входами первого двоичного умножителя. Новым в устройстве является соединение выхода первого двоичного умножителя с суммирующим входом реверсивного счетчика импульсов, вычитающий вход которого соединен с выходом второго двоичного умножителя частоты и выходом устройства. При этом разрядные выходы реверсивного счетчика соединены с информационными входами второго двоичного умножителя, тактовый вход которого связан последовательно через элемент задержки с выходом генератора тактовых импульсов. 1 ил. гистр 5, блок 6 памяти, реверсивный счетчик

7 импульсов, второй двоичный умножитель

8 и блок 9 задержки.

Устройство для умножения частоты работает следующим образом.

Входная частота f< поступает на управляющий вход схемы 2 измерения периода, на тактовый вход которой поступают импульсы с частотой fo с выхода генератора 1 тактовых импульсов. В схеме 2 каждый период формируется код N«значения периода входной частоты f

N o из схемы 2 измерения периода в регистр

5, а со второго выхода — установке схемы 2

8 йсхОДное состоЯние, КОД Ngn c выхоДа регистра 5 поступает на адресные входы блока 6 памяти. Коды, занесенные в блок 6 памяти, выбраны таким образом, что при любом значении Мил частота на выходе двоичного умножителя 4 в постоянное число раз (например, в М раз) выше значения

ВХОДНОЙ ЧаСтотЫ fx.

Реализация соотношение fsgtx = fx M(fsvx— выходная частота двоичного умножителя 4) обеспечивается выбором параметров от- 2О дельных его узлов в зависимости от диапазона и значений входного сигнала, требуемого коэффициента умножения и погрешностии.

Статическая характеристика устройства

М2и где и — разрядность двоичного умножителя

Ni — код на информационных входах двоичного умножителя 4, то Мг М (1)

2л Txmin + zo (1 — 1) где z = 1

35 о

t — номер отсчета (кода s схеме измереНИЯ ПЕРИОДа, НаЧИНаЯ С TXmln И ПРИНИМаЮщий значение 1, 2, 3, ... K(K — число отсчетов).

Импульсы с частотой 4, поступают íà 4Q суммирующий вход реверсивного счетчика

7, вычитающий вход которого соединен с выходами второго двоичного умножителя 8 частоты и устройства для умножения частоты. На тактовый вход двоичного умножителя 45

8 поступает через блок 9 задержки опорная

ЧаСтота fo.

Реверсивный счетчик 7 и двоичный умножитвль 8 частоты с показанными связями образуют следящую систему с передаточ- 5п ной функцией апериодического звена первого порядка

W(P) = ) (2) где Р— оператор Лапласа; К вЂ” коэффициент усиления;

Т вЂ” постоянная времени.

Если код блока в памяти строго постоянный, то частоть| на выходах умножителей

4 и 8 одинаковы, Если же при 1х = const код блока 6 изменяется на единицу младшего разряда, то на выходе умножителя 4 наблюдаются скачкообразные изменения частоты (при fx = const), а на выходе умножителя 8 формируется сгла>кенный сигнал в соответствии с динамической характеристикой (2) следящей системы, Формула изобретения

Устройство для умножения частоты, содержащее генератор тактовых импульсов, схему измерения периода, блок уп равления, первый двоичный умножитель и регистр, при:ем выход схемы измерения периода соединен с установочным входом блока управления, первый выход которого соединен с синхровходом регистра, а второй выход — с установочным входом схемы измерения периода, информационные. входы регистра соединены соответственно с разрядными

Входами схемы измерения периода, блок памяти, адресные входы которого соединены соответствен lo с разрядными выходами регистра, выходы — соответственно с информационными входами первого двоичного умножителя, причем счетный вход первого двоичного умножителя соединен с выходом генератора тактовых импульсов и тактовым входом схемы измерения периода, управляющий вход которой соединен с информационным входом устройства, о т л и ч а ющ е е cÚ тем, что, с целью повышения точности преобразования, в него введены реверсивный счетчик импульсов, суммирующий вход которого соединен с выходом первого двоичного умножителя частоты, второй двоичный умножитель, выход которого подключен к Вычитающему Входу реверсивного счетчика и является выходом устройства, при этом разрядные выходы реверсивного счетчика соединены с информационными входами Второго двоичного умно>кителя, тактовый вход которого связан последовательно через элемент задержки с выходом генератора тактовых импульсов.

1836681

Составитель В.Гусев

Техред M.MoðãåHòàë Корректор Л.Ливринц

Редактор Т.Куркова

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

Заказ 3020 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб.. 4/5