Устройство для извлечения квадратного корня из суммы квадратов двух величин

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и автоматике и может быть использовано в аналоговых вычислительных машинах, а также в системах автоматики, например, для вычислений длины двумерного вектора по его составляющим. Устройство для извлечения квадратного корня из суммы квадратов двух величин содержит пять блоков выделения модуля 1-5, блок выделения минимального сигнала 6, блок выделения максимального сигнала 7, инвертор 8, делитель 9, четыре сумматора 10-13. 1 ил,

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (st)s G 06 G 7/20

ПАТЕНТНОЕ

НИЕ ИЗОБРЕТЕНИЯ

МУ. С ВИДETEJlbCTBY

- - "4QH

-"" 1 ь8МЧД Щ

-. l ЕКА (2 ) 4873448/24 (2 ) 0810.90 (4 ) 30.08.93. Бал. М 32 (7 ) Харьковский государственный универси ет им.А.M.Ãîðüêoão и Харьковский и женерно-педагогический институт и .И.Ç.Соколова (7 ) Ю.Г.Белов, В.А.Добрыдень;

Н..Литвинец, П.Д.Литвинец и .С.Элькин (5 ) Авторское свидетельство СССР

ЬЬ 957228, кл. G 06 G 7/20, 1981.

Авторское свидетельство СССР

М 1140133, кл. 6 06 8 T/20, 1983, „, Ы„„1837270 А1 (54) УСТРОЙСТВО ДЛЯ ИЗВЛЕЧЕНИЯ

КВАДРАТНОГО КОРНЯ ИЗ СУММЫ КВАДРАТ0В ДВУХ ВЕЛИЧИН (57) Изобретение относится к вычислительной технике и автоматике и может быть использовано в аналоговых вычислительных машинах, а также в системах автоматики. например, для вычисления длины двумерного вектора пь его составляющим, Устройсг во для извлечения квадратного корня из суммы квадратов двух величин содержит пять блоков выделения модуля 1 — 5, блок выделения минимального сигнала 6, блок выделения максимального сигнала 7, инвертор 8. делитель 9, четыре сумматора 10-13.

1 ил.

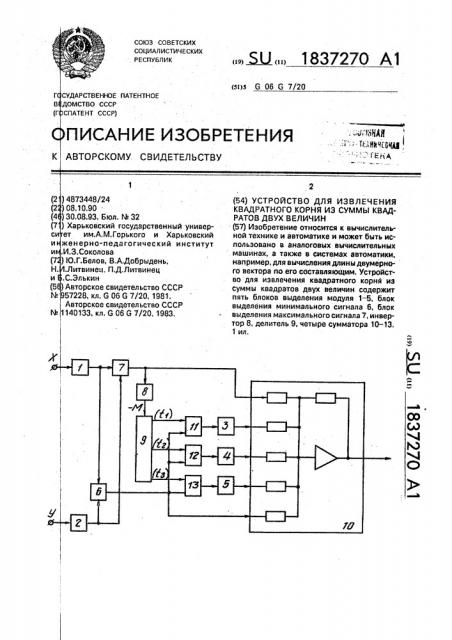

1837270 Лзобретение относится к вычислитель. ной технике и автоматике, оно может быть использовано в аналоговых вычислительных машинах, а также в системах автоматики, например, для вычисления длины двумерного вектора по его составляющим, Цель изобретения — повышение точности, На чертеже представлена блок-схема устройства.

Устройство содержит блоки 1 — 5 выделения модуля (с первого по пятый соответственно), блок 6 выделения минимального сигнала, блок 7 выделения максимального сигнала, инвертор 8, делитель 9 напряжения, сумматоры 10 — 13 (с первого по четвертый соответственно).

Устройство работает следующим образом.

На входы первого и второго блоков выделения модуля, являющиеся входами устройства, подаются входные сигналы Х и Y соответственно. На выходе блока 1 формируется при этом сигнал IX I, а на выходе блока 2 — сигнал I Y I. Зти сигналы поступают на входы блока 3 выделения максимального сигнала и на входы блока 4 выделения максимального сигнала, Таким образом, на выходе блока 3 формируется сигнал

m = min(IXI, IYI), а на выходе блока 4 — сигнал

M = max (I Х I, I Y I). (2)

Эти сигналы поступают на первый и второй входы первого сумматора 10 соответственно.

Сигнал M поступает, кроме того, на вход инвертора 8, выходной сигнал — M которого подается на вход делителя 9 напряжения.

На первом, втором и трс ьем выходах делителя 9 напряжения формируются соответственно сигнагы -t1M, -t2M, -AM, поступающие на первые входы второго, третьего и четвертого сумматоров 11, 12, 13 соответственно.

Вторые входы этих сумматоров объединены и соединены с выходом блока 6 выделения минимального сигнала. Следовательно, на выходе второго сумматора 11 формируется сигнал m-т1М, на выходе третьего сумматора 12 — сигнал m-AM, а на выходе четвертого сумматора — сигнал

m 1ЗМ. Блохи 3-5 выделяют модули соответствующих сигналов: на выходе блока 3 формируется сигнал lm t M I, на выходе блока

4 — сигнал lm--тгМ I, на выходе блока 5— сигнал Im — tgM I . Обозначим через S коэффициент суммирования первого сумматора 10 по i-My входу (i = 1, 2, „, 5). Поскольку выходы блоков 3, 4, 5 выделения модуля подключены соответственно к третьему, четвертому и пятому входам сумматора 10, на его выходе будет сформирован сигнал Z, определяемый формулой

10 Z = Stm+ SzM+ Sa Im — ttMI

+ S4 Im uM I+ $ь Im-тзМ1 Х Р (3) Коэффициенты tt, t>, тз, и S„, Яр, .„, Ss выбираются из условия минимума погрешности. При t1 = 0,21875, tg = 0,4535, u = 0,7239, S t = 0.379469161, Я2 = 0,878765278, S4 =«0,093961610, Яь = 0,073033935, Яз=

20 = 0,104376657 максимальная относительная погрешность вычисления величины р = V>(> p y> по формуле (3), определяемая формулой д — IP ZI 10000

Р о не превышает 0,293%, Ниже s таблице приведены значения 6 для различных сочетаний Х и Y на отрезке 0,1 с шагом 0,1.

Благодаря введению ряда новых элементов и новых функциональных связей, точность определения результата предло>кенным устройством существенно выше (примерно в 1,7 раза), чем точность прототипа.

Формула изобретения

Устройство для извлечения квадратного корня из суммы квадратов двух величин, содержащее первый и второй блоки выделения модуля, входы которых являются входами устройства, а выходы подключены к входам блока выделения минимального сигнала и к входам блока выделения максимального сигнала, выходы которых соединены соответственно с первым и вторым входами первого сумматора, а также делитель напряжения, о т л и ч а ю щ е е с я тем, что, с целью повышения точности, в него введены второй, третий и четвертый сумматоры, третий, четвертый и пятый блоки выделения модуля и инвертор, подключенный входом к выходу блока выделения максимального сигнала, а выходом — к входу делителя напряжения, первые входы второго, третьего и четвертого сумматоров соединены с соответствующими выходами

183?270

Составитель 6.Элькин

Техред M.Mîðãeíòàë КоРРектоР А,Мотыль

Редактор Н.Коляда Заказ 2865 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101 делителя напряжения, вторые входы объединены и соединены с выходом блока выде ления минимального сигнала, а выходы соединены с входами соответственно третьего, четвертого и пятого блоков выделения модуля, выходы которых подключены соответственно к третьему, четвертому и пятому входам первого сумматора.