Устройство для предварительной обработки информации

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть использовано при проведении отладки и испытании измерительных и управляющих систем, а также в различного рода имитаторах и тренажерах, работающих в комплексе с электронной вычислительной машиной. Цель изобретения - повышение надежности работы устройства за счет исключения возсо со Ч к ч ь

СОЮЗ СОВЕТСКИХ .СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (ll) (s1)s G 06 F 3/00

ННОЕ flATEHTHOE

BE ОМСТВО СССР (Г СПАТЕНТ СССР)

flMCAlHIME ИЗОБРЕТЕНИЯ !

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (2 (2 (4 (7

5 че (7 (5

) 4945091/24

) iI3.06.91

) 30.08.93. Бюл. М 32

) Киевский политехнический институт им. летия Великой Октябрьской социалистикой революции

) В.Н,Калина и А.А.Мусайлян

) Авторское свидетельство СССР

924672, кл. G 05 В 19/18, 1979.

Авторское свидетельство СССР

1062684, кл. G 06 F 3/05, 1982, (54) УСТРОЙСТВО ДЛЯ ПРЕДВАРИТЕЛЬНОЙ ОБРАБОТКИ ИНФОРМАЦИИ (57) Изобретение относится к области вычислительной техники и может быть использовано при проведении отладки и испытании измерительных и управляющих систем, а также в различного рода имитаторах и тренажерах, работающих в комплексе с электронной вычислительной машиной.

Цель изобретения — повышение надежности работы устройства за счет исключения воз1837274

30

40 можности считывания ложной информации, Устройство содержит блок ввода 1, блок памяти 3, счетчик времени 4, арифметический блок

5, шифратор 10, элемент задержки 11, коммутатор 12 и генератор опорной частоты 13.

Новыми в устройстве являются дополнительные элементы задер>кки 14, регистр 15 и элемент И 16. Положительный эффект

Устройство относится к области вычислительной техники и может быть использовано при проведении отладки испытании измерительных и управляющих систем, а также в различного типа имитаторах и тренажерах, работающих в комплексе с электронной вычислительной машиной (3BM).

Целью изобретения является повышение надежности работы путем исключения ложных срабатываний из-за несинхронности работы отдельных блоков(счетчика времени, арифметического блока и элемента задер>кки).

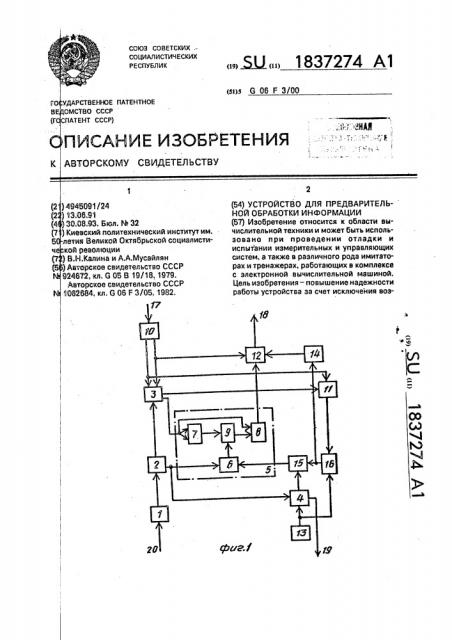

На фиг.1 представлена блок-схема устройства; на фиг,2 — временная диаграмма синхронизации работы блоков устройства; на фиг.3 — функциональная схема блока буферной памяти 2; на фиг.4 — функциональная схема блока памяти 3; на фиг.5 — схема делителя 6, на фиг.6 — схема элемента задержки 11; на фиг,7 — детализированный фрагмент схемы устройства, отражающий взаимодействие блока ввода 1, блока буферной памяти 2 и блока памяти 3 между собой и их связь с другими блоками устройства.

Устройство содержит блок 1 ввода, блок

2 буферной памяти, блок 3 памяти, счетчик

4 времени, арифметический блок 5, включающий делитель 6, сумматоры 7 и 8, узел 9 умножения, шифратор 10, первый элемент

11 задержки, коммутатор 12, генератор 13 опорной частоты, второй элемент 14 задержки, регистр 15, элемент И 16, управляющий вход 17 устройства, информационный

18 и управляющий 19 выходы и информационный вход 20 устройства.

Блок 2 буферной памяти (фиг,3) предназначен для записи информационного кадра независимо от наличия или отсутствия запросов от ЭВМ, Блок 2 содержит в своем составе набор регистров 21 в количестве и, определяемом размерами информационного кадра. В данном варианте реализации устройства в качестве регистров 21 используются интегральные микросхемы типа К 45

155 ИР 1.. Запись информации в блок 2 буферной памяти осуществляется следующим достигается за счет фиксации значения текущего времени интервала интерполяции арифметическим блоком и выдачи ее через коммутатор, и за счет синхронизации во времени процессов переключения счетчика, работы арифметического блока и выдачи информации через коммутатор. 7 ил, образом (фиг.7). Информация со входов 20 устройства в,момент времени, начало которого определяется сигналом запроса с выхода 19 устройства, поступает в блок ввода

1. В блоке 1 часть информационных разрядов через блок усилителей 22 поступает параллельно на все информационные входы регистров 21 блока 2 буферной памяти. Другая часть разрядов вместе со стробирующим сигналом поступает на дешифратор 23 блока 1, Каждый из выходов дешифратора

23 соединен с соответствующим стробирующим входом каждого из регистров 21 блока

2 буферной памяти. Таким образом, запись информации в блок 2 осуществляется со стороны внешнего источника путем последовательной установки информационных разрядов, поступающих на все регистры 21 и последующим формированием стробирующих сигналов дешифратором 23, индивидуальных для каждого регистра 21 блока 2.

Порядок записи информации в регистры определяется со стороны внешнего источника кодами, поступающими на дешифратор 23 блока 1 ввода и может быть произвольным.

Блок 3 памяти (фиг.4) предназначен для хранения и выдачи операндов на арифметический блок 5 передачи информации на элемент 11 задержки в момент времени, определяемый запросом от ЭВМ. Блок 3 содержит в своем составе набор регистров 24 и коммутаторов 25. Регистры 24 могут быть реализованы на микросхемах типа

К155ИР1, а коммутаторы — на микросхемах типа К155ЕП2 или аналогичных. Управление записью/считыванием блока 3 памяти осуществляется следующим образом (фиг.7).

Информационные входы регистров блока 3 соединены с соответствующими выходами регистров блока 2 последовательно. Запись информации в регистры 24 блока 3 памяти осуществляется путем подачи стробирующего сигнала на все регистры 24 одновременно. Стробирующий сигнал формируется одним из выходов второй группы выходов шифратора 10. Перезапись информации с регистров блока буферной памяти 3 осуще1837274 ст ва щ сл ш

rp ка та ст по эа

7 пр вр вх

10 ци м

6 за

5 де вх ве с р с

P н ч ш х и т чи р д ус р

30 за с о д

Г з з б з в р ( р е

1 р

Н б

2 и н

50 ляется параллельно за один такт. Считыие информации из блока 3 памяти осутвляется по сигналам шифратора 10 дующим образом. Код, формируемый фратором 10, поступает с его первой ппы выходов через адресные входы бло8 памяти на управляющие входы коммуора 25, Коммутатор 25 (фиг.4) выполнен оенным, т.е. транслирует информацию трем параллельным каналам: на элемент ержки 11 и две группы входов сумматора рифметического блока 5. Информация сутствует на выходах блока 3 памяти все мя, пока поступает данный адрес на д блока 3.

Делитель 6 (фиг.5) осуществляет операделения над операндами, поступающи«а его первый и второй входы. Делитель еализован на микросхеме постоянного сминающего устройства типа КР 556 PT кс; 348.322 ТУ 5). Операнды (делимое и итель), поступающие на первый и второй ды делителя 6 (фиг.1) поступают на сооттвующие группы адресных входов микхемы КР556РТ5 (фиг.6). Суть данной лизации заключается в том, что для ограенного числа состояний, т.е. для небольпо разрядности значений интервалов ерполяции, можно предварительно вылить возможные дискретные значения ультатов деления для различных операни записать в постоянное запоминающее

Ойство.

Элемент 11 задержки (фиг.6) имитирует ержку прохождения информации через стему устройств связи с объектом (УСО) и ределяет время задержки выдачи сигнала твет на внешний запрос. Элемент 11 соржит счетчик 26, который может быть вылнен на микросхеме К 155 ИЕ 7, нератор 27 импульсов, элемент И 28, тригр 29 и инвертор 30. Работа элемента 11 держки осуществляется следующим обрам. Со вторых информационных выходов ока 3 памяти (см. фиг.4) на вход элемента держки 11 поступает код числа, сопрождаемый стробирующим сигналом со втоtx выходов шифратора 10. Счетчик 26 иг.6) в этот момент времени находится в жиме параллельного занесения, т.к. на о управляющем режимами входе (контакт

) находится нулевой потенциал. Четырехзрядный код с выходов блока памяти 3 ступает на входы параллельного занесея счетчика 26. Стробирующий сигнал от ока 10 поступает на синхровход триггера, устанавливая его прямой выход в едичное состояние. Единичный уровень сигла с выхода триггера 29 переключает счетчик 26 иэ режима гараллельного занесения в режим счета и одновременно разблокирует элемент И 28, С приходом очередного импульса от генератора импульсов 27 начинается переключение счетчика

26. Процесс счета повторяется до тех пор, пока не исчерпается время задержки, заданное кадом, записанным в счетчик 26.

При окончании счета на выходе счетчика 26 появляется сигнал переноса (заема), который,поступая на вход сброса триггера 29, устанавливает его выход в нулевое состояние, тем самым переключая счетчик в режим параллельного занесения для приема очередного кода задержки, и блокирует элемент И 28 для прохождения импульсов генератора 27, Этот же сигнал задержки через инвертор 30 поступает на выход элемента 11 задержки и далее на вход элемента И

16, Далее под управлением сигналов от

Э ВМ вышеописанные процессы повторяются.

Принцип работы устройства основан на вычислении значения воспроизводимого сигнала в момент поступления запросов от

ЭВМ на участке интерполяции, заданном кодами от начала, конца и длительности, При этом номер канала преобразования, момент времени вычисления значения сигнала и участок интерполяции, на котором проводится вычисление, определяются моментом поступления и содержанием запроса ЭВМ, совместно с которой функционирует устройство по соответствующим алгоритмам обмена и временной диаграмме.

Количество каналов преобразования зависит не только от объема используемой памяти, а также разрядности шифратора и коммутатора, определяющей возможности адресации.

В каждый момент времени в системе хранится информация двух кадров — текущего и последующего. Текущий кадр содержит коэффициенты К(и).и Ki начала и конца интервала интерполяции по всем каналам преобразования, величину интервала интерполяции 1, общую для всего кадра (всех каналов преобразования), а также величины задержки выдачи сигнала, подобранные таким образом, чтобы задержка в получении ЭВМ информации в ответ на запрос соответствовала времени прохождения ее через систему УСО, или любых других систем преобразования информации.

Причем но истечении интервала интерполяции предыдущего кадра начинается отсчет времени текущего кадра, а в систему вводится информация последующего кадра, 1837274 и такое обновление информации происходит независимо от наличия или отсутствия запросов от 3ВМ.

Поскольку конец предыдущего кадра является началом последующего, то в последующем кадре отсутствует коэффициент начала интервала интерполяции.

В исходном состоянии в блоке 3 памяти находятся коэффициенты Ко и К всех каналов преобразования и соответствующие им величины задержек; величина интервала интерполяции первого кадра т1 занесена в делитель 6 и в счетчик 4.

Информация второго кадра, т.е. коэффициенты Кз всех кадров преобразования, соответствующие величины задержек и величина интервала интерполяции второго кадра находятся в блоке 2, В начальный момент времени на управляющий вход 17 шифратора 10 поступает запрос от внешнего управляющего устройства (например, ЭБМ). По этому сигналу шифратор 10 вырабатывает соответствующий код, поступающий на вход блока 3, как адрес ячейки памяти, и на управляющий вход коммутатора 12 как HQMep канала.

Значения коэффициентов, выбранные по адресам, сформированным шифратором

10, с выхода блока 3 поступают на сумматор

7. Кроме того, значение коэффициента Ко поступает на вход сумматора 8. Момент поступления значения t — текущего времени интервала интерполяции т на вход делителя б определяется временем задержки перaoro элемента 11 =.àäåðæêè, имитирующем задержку прохождения информации через систему УСО и определяющем время задержки выдачи сигнала в ответ на внешний запрос. По истечении времени задер>кки на выходе элемента 11 задержки, выполненного на базе счетчика, появляется сигнал (фиг.2е), поступающий на второй вход элемента И 16. Как видно из временной диаграммы на фиг.2, импульсы генератора 13 опорной частоты (фиг,2а) своим отрицательным фронтом осуществляют переключение счетчика 4 времени (на фиг.2б — д в качестве примера показаны выходы первых четырех разрядов счетчика 4). Стробирование элемента И 16 осуществляется положительным фронтом импульса генератора 13. Таким образом, после окончания переходных процессов при переключении счетчика 4 и времени на выходе элемента И 16 формируется сигнал (фиг.2ж), по которому производится перезапись содержимого счетчика 4 в регистр 15 (фиг.2з) и запускается второй элемент 14 задер>кки (фиг.2к).

Значение t — гекущего времени интервала интерполяции t, зафиксированное в регистре 15, поступает на вход делителя 6. При этом делитель 6 вырабатывает код t r, кото5 рый поступает на вход узла 9 умно>кения, на другой вход которого поступает разность вида К вЂ” К > с выхода сумматора 7. Результат умно>кения с выхода узла 9 поступает на вход сумматора 8 и суммируется с коэффи10 циентом Ко, поступающим на другой вход сумматора 8. Полученное таким образом значение сигнала в точке опроса в виде кода

Х = Ко+(К вЂ” К>) t/t с выхода сумматора 8 (фиг.2и) поступает на вход коммутатора 12.

15 Время задержки второго элемента 14 задержки выбирается чуть большим времени срабатывания арифметического блока 5, чтоб обеспечить прохождение информации через коммутатор 12 после завершения пе20 реходных процессов в арифметическом блоке 5. С выхода второго элемента 14 задер>кки сигнал поступает на стробирующий вход коммутатора 12, на управляющем входе которого установлен номер канала с

25 выхода шифратора 10.

Поскольку информация кадра сохраняется в памяти устройства неизменной до конца отработки интервала интерполяции, т.е. до заполнения счетчика 4, запрос от

30 внешнего управляющего устройства может быть повторен llo произвольному или прежнему каналу, и на выходе 18 коммутатора 12 будут получены новые значения сигналов в точке опроса.

35 По окончании заполнения счетчика 4 формируется запрос очередного кадра информации, который с выхода 19 поступает во внешний источник информации, По этому запросу на вход 20 блока 1 ввода инфор40 мации от внешнего источника информации поступают коды, соответствующие очередному кадру информации, и записывается в блок 2 буферной памяти. При этом коэффициенты и соответствующие им величины за45 дер>кек очередного кадра переписываются из блока 2 в блок 3, а значение с выхода блока 2 поступает на вход делителя 6 и вход счетчика 4. В дальнейшем устройство функционирует в соответствии с вышеизложен50 ным алгоритмом.

Таким образом, за счет фиксации значения текущего времени т интервала интерполяции z в регистре 15 на время, необходимое для обработки информации

55 арифметическим блоком 5 и выдачи ее через коммутатор 12 и за счет синхронизации во времени процессов переключения счетчика

4. работы блока 5 и выдачи через коммутатор 12 исключается возможность считыва i0

1837274

Я н я ложной информации с устройства, чем с щественно повышается надежность его р боты.

Формула изобретения

Устройство для предварительной обраб тки информации, содержащее блок ввод, блок буферной памяти, блок памяти, счетчик времени, шифратор, первый элемент задержки, коммутатор, генератор

1 о орной частоты и арифметический блок, к торый содержит делитель, первый и втор и сумматоры и узел умножения, причем и формационный вход блока ввода являетс информационным входом устройства, в ход блока ввода подключен к входу блока б ферной памяти, первый выход которого и дключен к информационному входу блока и мяти, первый информационный выход кот рого подключен.к входу первого и первом входу второго сумматоров, первый вход елителя соединен с вторым выходом блока

6 ферной памяти и с информационным вход м счетчика времени, выход второго сумматора подключен к информационному в оду коммутатора, вход шифратора являетс управляющим входом устройства, перв и выход шифратора соединен с адресным в одом блока памяти и с управляющим входрм коммутатора, информационный вход первого элемента задержки соединен с вторым информационным выходом блока памяти, выход коммутатора является информационным выходом устройства, так5 товый вход счетчика времени соединен с выходом генератора опорной частоты, управляющий выход счетчика времени является управляющим выходом устройства, входы узла умножения подключены соот10 ветственно к выходам первого сумматора и делителя, второй вход второго сумматора подключен к выходу узла умножения, о т л ич а ю щ е е с я тем, что, с целью повышения надежности устройства, в него введены вто15 рой элемент задержки, регистр и элемент И, первый вход которого соединен с выходом генератора опорной частоты, второй вход подключен к выходу первого элемента задержки, а выход соединен с входом второго

20 элемента задержки и стробирующим входом регистра, информационный вход которого соединен с информационным выходом счетчика времени, а выход соединен с вторым входом делителя, выход вто25 рого элемента задержки соединен со стробирующим входом коммутатора, второй выход шифратора соединен со стробирующими входами блока памяти и первого элемента задержки. I837274

1 8372 14

1837274

1837274

Составитель В.Калина

Техред М.Моргентал дактор H.Êîëÿäà

КоРРектоР С.Патрушева

Производственно-издательский комбинат "Патент" г, У, г, жгород, ул, агарина, 101 ,Г

Заказ 2865 Тираж

ВНИИПИ Гос

Подписное осударственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб„4/5