Многоканальный сигнатурный анализатор

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой вычислительной технике и может быть использовано для технического диагностирования цифровых устройств. Целью изобретения является повышение достоверности контроля . Анализатор содержит три формирователя сигнатур, три блока хранения сигнатур, два блока сравнения, два счетчика, два триггера , блок индикации, одновибратор, два индикатора, элемент ИЛИ, четыре элемента И, группу элементов И, регистр сдвига, элемент И-НЕ, элемент задержки. Анализатор позволяет локализовать пачки ошибок в анализируемой последовательности, что позволяет повысить достоверность контроля. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК! ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ ! ВЕДОМСТВО СССР . (ГОСПАТЕНТ СССР)

ОПИСАНИЕ ИЗОБРЕТЕНИЯ (si>s G 06 F 11/00 Фю ЩФЩЦ

-Al:.:

4 ° 1 < и - ;, - ю ° 1,: Г, К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1! (21) 4767976/24 (22) 08.12.89

l(46) 30.08.93. Бюл. М 32 (71) Донецкий политехнический институт (72) О.Н.Дяченко ! (56) 1. Авторское свидетельство СССР

t % 1797118, кл. G 06 F 11/00, 1989, ((54) МНОГОКАНАЛЬНЫЙ СИГНАТУРНЫЙ АНАЛИЗАТОР (57) Изобретение относится к цифровой вы,, числительной технике и может быть исполь; зовано для технического диагностирования

Изобретение относится к цифровой вы числительной технике и может быть исполь, зовано для технического диагностирования, цифровых устройств.

Целью изобретения является повыше-! ние достоверности контроля.

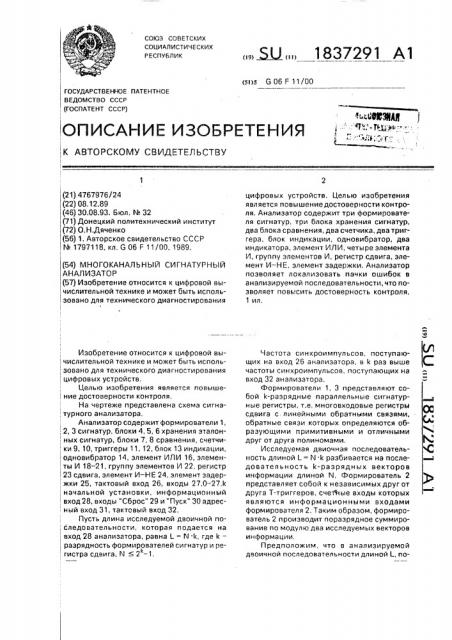

На чертеже представлена схема сигна турного анализатора.

Анализатор содержит формирователи 1,, 2, 3 сигнатур, блоки 4, 5, 6 хранения эталонных сигнатур, блоки 7, 8 сравнения, счетчи ки 9, 10, триггеры 11, 12, блок 13 индикации, одновибратор 14, элемент ИЛИ 16, элемен ты И 18-21, группу элементов И 22, регистр .23 сдвига, элемент И вЂ” НЕ 24, элемент задер ; жки 25, тактовый вход 26, входы 27.0 — 27,k .начальной установки, информационный вход 28, входы "Сброс" 29 и "Пуск" 30 адрес ный вход 31, тактовый вход 32.

Пусть длина исследуемой двоичной по; следовательности, которая подается на, вход 28 анализатора, равна L = N k, где k—

1 разрядность формирователей сигнатур и регистра сдвига, N 2 -1.

„, . Ж, 1837291 А1 цифровых устройств. Целью изобретения является повышение достоверности контроля. Анализатор содержит три формирователя сигнатур, три блока хранения сигнатур, два блока сравнения, два счетчика, два триггера, блок индикации, одновибратор, два индикатора, элемент ИЛИ, четыре элемента

И, группу элементов И, регистр сдвига, элемент И вЂ” НЕ, элемент задержки. Анализатор позволяет локализовать пачки ошибок в анализируемой последовательности, что позволяет повысить достоверность контроля.

1 ил, Частота синхроимпульсов, поступающих на вход 26 анализатора, в k раз выше частоты синхроимпульсов, поступающих на вход 32 анализатора.

Формирователи 1, 3 представляют собой k-разрядные параллельные сигнатурные регистры, т.е, многовходовые регистры сдвига с. линейными обратными связями, обратные связи которых определяются образующими примитивными и отличными друг от друга полиномами, Исследуемая двиочная последовательность длиной L = N k разбивается на последовательность k-разрядных векторов информации длиной N, Формирователь 2 представляет собой к независимых друг от друга T-триггеров, счетные входы которых являются информационными входами формирователя 2, Таким образом, формирователь 2 производит поразрядное суммирование по модулю два исследуемых векторов информации.

Предположим. что в анализируемой двоичной последовательности длиной L, по1837291 ступающей на вход 28 анализатора, имеет место пачка ошибочных бит, размеры которой не превышают k. При разбиении этой последовательности на N k-разрядных векторов возможны два случая:

1) в полученной последовательности kразрядных векторов длиной L имеет место только один ошибочный вектор;

2) в полученной последовательности kразрядных векторов длиной N имеют место только два ошибочных вектора, причем, если порядковый номер первого из них равен и, то порядковый номер второго ошибочного вектора равен п+1, Каждый из блоков 4-6 хранит две эталонные сигнатуры.

Первые эталонные сигнатуры в блоках

4 — 6 получаются путем сжатия эталонной последовательности k-разрядных векторов длиной 2 -1 (если N < 2 -1, то эталонная

k последовательность векторов дополняется нулевыми векторами до требуемой длины).

Вторые эталонные сигнатуры получаются путем сжатия эталонной последовательности только тех k-разрядных векторов, порядксгвые номера которых являются четными, если N-четное число, или нечетными, если N-нечетное число, длиной 2 -1 (если N

< 2 -1, то эталонная последовательность векторов дополняется нулевыми векторами 30 до требуеМой длины).

Анализатор работает следующим образом.

По внешнему управляющему сигналу, поступающему на вход 29, все разряды фор- 35 мирователей 1 — 3 устанавливаются в нулевое состояние, На вход 31 анализатора подается логический нуль, соответствующий адресу первых эталонных сигнатур, хранящихся в блоках 4-6, На выходе эле- 4" мента И вЂ” НЕ 24 устанавливается логическая единица, По внешнему управляющему сигналу, поступающему на вход 30, счетчик 9 устанавливается в нулевое состояние, триггеры 11, 12 устанавливаются в нулевое со- 45 стояние, первые эталонные сигнатуры с выходов блоков 4 — 6 заносятся соответственно в формирователи 1-3 и с входов 27.027.К заносится двоичный код числа N в счетчик 10. При этом на инверсном выходе старшего разряда счетчика 10 появляется логическая единица (так как N < 2 -1), котоk рая разрешает прохождение сигналов через элемент И 19, через элемент И 21 и через группу элементов И 22. Кроме того, на выходе старшего разряда счетчика 9 устанавливается логический нуль, следовательно, на выходе элемента ИЛИ 16 появится логическая единица, разрешающая прохождение синхроимпульсов через элемент И 18, а так как триггер 12 установлен в нулевое состояние. то на его инверсном выходе установлена логическая единица, которая также разрешает прохождение синхроимпульсов через элемент И 18, Логический нуль на выходе старшего разряда счетчика 9 "запирает" элемент И 20.

Синхроимпульсы с входа 32 анализатора через элемент И 18 поступают на счетный вход триггера 11, который является нулевым разрядом счетчика 9, через элементы 18, 19

И синхроимпульсы поступаю1 на вычитающий вход счетчика 10, через элемент И 18 и элемент 25 задержки синхроимпульсы поступают на тактовые входы формирователей

1-3 сигнатур.

Исследуемая двоичная последовательность поступает на вход регистра 23 с информационного входа 28 анализатора, На тактовый вход регистра 23 поступают синхроимпульсы с входа 26, частота которых в k раз выше частоты синхроимпульсов, поступающих на вход 32 анализатора, Таким образом, векторы информации с информационных выходов регистра 23 через элементы И группы 22 поступают на информационные входы формирователей 1 — 3.

Таким образом, анализатор производит сжатие последовательности исследуемых векторов информации.

Через N тактов работы анализатора в формирователях 1, 3 сигнатур получаются сигнатуры вектора ошибки ошибочного вектора информации, а в формирователе 2 сигнатур — вектор ошибки ошибочного вектора информации. Во всех разрядах счетчика 10 будут нули, а на инверсном выходе старшего разряда счетчика 10 будет логическая единица, которая все еще разрешает прохождение синхроимпульсов через элемент И 19 и прохождение векторов информации через группу элементов И 22.(N+1)-й синхроимпульс устанавливает на инверсном выходе старшего разряда счетчика 10 логический нуль, который запрещает поступление синхроимпульсов через элемент

И 19 и прохождение исследуемых векторов информации через группу элементов И 22.

Синхроимпульсы, поступающие на входы формирователе 1-3, задерживаются элементом 25, поэтому, когда на входы формирователей сигнатур и ридет (N+1)-й синхроимпульс, передача исследуемых векторов информации через группу элементов

И 22 уже будет запрещена, На этом счетчик заканчивает свою работу.

Допустим, что в анализируемой двоичной последовательности (а, следовательно, и в исследуемых векторах информации) не было ошибочных битов, Тогда через N так1837291 т м н н

С г с с

И

Р и б б ц к

20 н

Ч а

1 б с ге ш л

2 о и н и р ч тр

Ф и че та

A б р ве н ва к о сл но

1 в работы анализатора содержимое форрователей 1 — 3 сигнатур будет нулевым, а выходе блока 7 появляется логический ль, который "запирает" элемент И 20. етчик, образованный счетчиком 9 и триг4В k ром 11, досчитывает до, 2 . на выходе аршего разряда этого счетчика установитлогическая единица, на выходе элемента

И 16 появляется логический нуль, котой запрещает прохождение синхроимльсов через элемент И 18. На выходе ока 8 будет логический нуль. На этом рата анализатора завершается с индикаей двоичного числа, в старшем разряде торого единица, а в остальных — нули.

Допустим, что в анализируемой двоичй последовательности имеет место пачка ибочных битов, размер которой не пре шает k. Тогда возможно два случая, Пусть все ошибочные биты расположев одном ошибочном векторе информаи. Тогда через N тактов работы ализатора содержимое формирователей

3 сигнатур не будет нулевым, а на выходе ока 7 будет логическая единица. Когда етчик, образованный счетчиком 9 и тригом 11, досчитает до 2k, на выходе старго разряда этого счетчика установится ическая единица, на выходе элемента И появится логическая единица, на выходе новибратора 14 появится одиночный имьс, который установит триггер 11 s едичное состояние, В дальнейшем оисходит изменение сигнатуры в формивателях 1, 3 сигнатур и счет тактов в счетке, образованном счетчиком 9 и ггером 11, до тех пор, пока содержимое рмирователей 1, 2 сигнатур не совпадут, и этом на выходе блока 7 появится логикий нуль, на выходе элемента ИЛИ 16 же появится логический нуль, который ретит прохождение синхроимпульсов ез элемент И 18. На выходе блока 8 будет ческий нуль — признак того, что ошибочвектор только один. На этом работа лизатора завершается с индикацией ичного кода порядкового номера ошиного вектора информации (пачки исканных битов), Пусть ошибочные биты пачки ошибок положены в двух соседних ошибочных торах информации. Тогда по завершео работы анализатора будет индицироься двоичное число, в младшем разряде орого — единица (признак кратности ибочных веткоров информации). В этом чае работа анализатора повторяется зао (необходимо еще раз производить тие анализирумой двоичной последованости). При этом работа анализатора

55 аналогична рассмотренной выше за исключением следующего: на вход 31 анализатора поступает потенциальный сигнал (логическая единица), соответствующий адресу вторых эталонных сигнатур, хранящихся в блоках 4 — 6. Эти эталонные сигнатуры заносятся соответственно в формирователи 1 — 3 сигнатур по внешнему управляющему сигналу, поступающему на вход 30.

В процессе сжатия векторов информации на выходе элемента И вЂ” НЕ 24 будут чередоваться состояния логического нуля и единицы. Если К (начальное состояние счетчика 10) четное число, то вектора информации. порядковые номеры которых нечетные. исключаются из последовательности векторов информации и не участвуют в процессе сжатия последовательности, так как в соответствующие их появлению моменты времени на выходе элемента И вЂ” НЕ 24 логический нуль, который запрещает прохождение информации через группу элементов И 22. Аналогично, если M — нечетное число, то исключаются векторы информации, порядковые номера которых четные, В соответствии с предложением о том, что в анализируемой двоичной последовательности имеет место пачка ошибочных бит, размерность которой не превышает К а ошибочные биты располагаются в двух ошибочных соседних векторах, следует, что порядковый номер одного из них четный, а порядковый номер другого ошибочного вектора — нечетный. Поэтому при сжатии последовательности векторов информации один ошибочный вектор исключается из последовательности сжимаемых вектоpos информации. а другой остается. Таким образом, когда в последовательности векторов информации имеет место только один ошибочный вектор, в конце работы анализатора будет индицироваться двоичные число (за исключением младшего и старшего разряда), равное порядковому номеру ошибочного вектора. Порядковый номер второго ошибочного вектора равен (n-1) или (и+1), При этом в младшем разряде индицируемого двоичного числа (признак кратности ошибочных векторов информации) должен быть логический нуль., в старшем разряде (признак отсутствия компенсации ошибок в одном из формирователей сигнатур) — логическая единица. В противном случае в анализируемой последовательности пачка ошибочных битов, размерность которой превышает К

Формула изобретения

Многоканальный сигнатурный анализатор, содержащий два счетчика, два блока

1837291

10

45 сравнения, блок индикации, элемент ИЛИ, два триггера, одновибратор, элемент задержки, группу элементов И, три элемента И. три блока хранения эталонных сигнатур, три формирователя сигнатур, входы сброса которых образуют вход сброса анализатора, входы сброса первого и второго триггеров, входы считывания первого, второго и третьего блоков хранения эталонных сигнатур, установочный вход первого счетчика и вход параллельной загрузки второго счетчика объединены и образуют вход пуска анализатора, группа информационных входов второго счетчика образует группу входов. начальной установки анализатора, группа разрядных выходов первого счетчика соединена с группой входов блока индикации, выход первого элемента И соединен с тактовым входом второго счетчика, инверсный выход старшего разряда которого соединен с первым входом первого элемента И, группы информационных выходов первого и второго блоков хранения эталонных сигнатур соединены соответственно с группами входов начальной установки первого и второго формирователей сигнатур, выход первого блока сравнения соединен с первым входом элемента ИЛИ и первым вхОдом второго элемента И, второй вход которого соединен с прямым выходом старшего разряда первого счетчика, инверсный выход старшего разряда которого соединен с вторым входом элемента ИЛИ и счетным входом первого триггера, инверсный выход которого соединен с первым входом третьего элемента И, второй вход которого соединен с выходом элемента

ИЛИ, выход третьего элемента И соединен со счетным входом второго триггера, с вторым входом первого элемента И и входом элемента задержки, выход которого соединен с тактовыми входами первого, второго и третьего формирователей сигнатур, группы информационных входов которых поразрядно объединены и подключены к выходам соответствующих элементов И группы, выход второго блока сравнения и прямой выход второго триггера соединены соответственно с первым и вторым входами блока индикации. инверсный выход второго триггера соединен с тактовым входом первого счетчика; выход второго элемента И соединен с входом одновибратора, выход которого соединен с установочным входом второго триггера, третий вход третьего элемента И образует первый тактовый вход анализатора, группа информационных выходов третьего блока хранения эталонных сигнатур соединена с группой входов начальной установки третьего формирователя сигнатур, группа информационных выходов первого формирователя сигнатур соединена с первыми группами входов первого и второго блоков сравнения, группы информационных выходов второго и третьего формирователей сигнатур соединены с вторыми группами входов первого и второго блоков сравнения соответственно, о т л и ч а юшийся тем, что, с целью повышения достоверности контроля, он дополнительно содержит регистр сдвига. четвертый элемент И и элемент И вЂ” НЕ, выход которого соединен с первым входом четвертого элемента И, второй вход которого подключен к инверсному выходу последнего разряда первого счетчика, выход четвертого элемента И соединен с первыми входами элементов И группы, вторые входы которых подключены к соответствующим разрядным выходам регистра сдвига, информационный и тактовый входы которого образуют соответственно информационный и второй тактовый входы анализатора, первый входэлемента И-НЕ и адресные входы первого, второго и третьего блоков хранения эталонных сигнатур образуют вход задания эталонных сигнатур анализатора, второй вход элемента И вЂ” НЕ подключен к выходу младшего разряда второго счетчика, 183 гэ1

27.1

Редактор

Корректор О. Густи каз 2866 Тираж Подписное !

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент". г. Ужгород, ул.Гагарина, 101

29

Составитель О, Дяченко

Техред М.Моргентал