Устройство для адресации массивов данных

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, в частности к устройствам управления внешней памятью, и может быть использовано для расширения адресного пространства микроЭВМ при адресации памяти данных, носящих произвольно-последовательный характер. Целью изобретения является повышение быстродействия устройства . Поставленная цель достигается тем, что устройство содержит два регистра, дешифратор, два счетчика, схему сравнения и одновибратор. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 0 06 F 12/00

СУДАРСТВЕННОЕ ПАТЕНТНОЕ

ЕДОМСТВО СССР

ОСПАТЕНТ СССР) =;уа i> p

ПИСАНИЕ ИЗОБРЕТЕНИЯ ( ( ( ( АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

) 4803605/24

) 19.03.90

) 30.08.93, Бюл. N 32

) Львовский политехнический институт . Ленинского комсомола

) О.К.Мешков, И.Б,Боженко и Б.В,Грини) Титце У.. Шенк К. Полупроводниковая емотехника, M. Мир, 1982, с,389 — 397, с.21,17.

Патент США М 4346441, 6 06 F 13/06, 1982.

Изобретение относится к вычислительной технике. в частности к,устройствам уп1 рввления внешней памятью, и может быть использовано для расширения адресного пространства микроЭВМ при адресации паяти данных, носящих произвольно-послевательный характер.

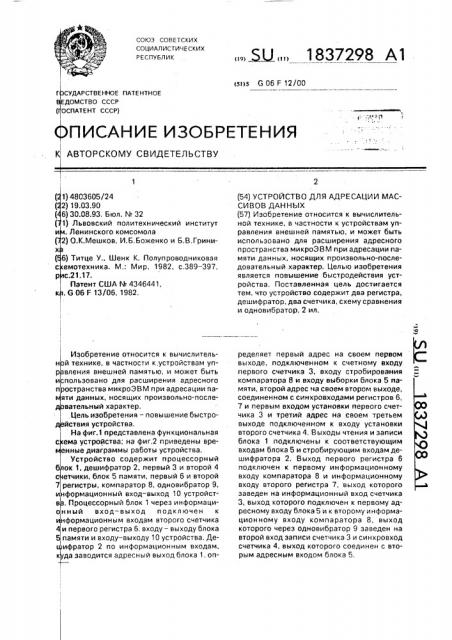

Цель изобретения — повышение быстрод йствия устройства, На фиг.1 представлена функциональная с ема устройства; на фиг.2 приведены вреенные диаграммы работы устройства.

Устройство содержит процессорный б бок 1, дешифратор 2, первый 3 и второй 4 с етчики, блок 5 памяти, первый 6 и второй

7 регистры, компаратор 8, одновибратор 9, информационный вход-выход 10 устройств, Процессорный блок 1 через информационный вход — выход подключен к нформационным входам второго счетчика и первого регистра 6, входу — выходу блока памяти и входу-выходу 10 устроиства. Двц1ифратор 2 по информационным входам. к да заводится адресный выход блока 1, on5U„, 1837298 А1 (54) УСТРОЙСТВО ДЛЯ АДРЕСАЦИИ МАССИВОВ ДАНН61Х (57) Изобретение относится к вычислительной технике, в частности к устройствам управления внешней памятью, и может быть использовано для расширения адресного пространства микроЭВМ при адресации памяти данных, носящих произвольно-последовательный характер. Целью изобретения является повышение быстродействия устройства. Поставленная цель достигается тем, что устройство содержит два регистра, дешифратор, два счетчика, схему сравнения и одновибратор. 2 ил.

\» ределяет первый адрес на своем первом выходе, подключенном к счетному входу первого счетчика 3, входу стробирования компаратора 8 и входу выборки блока 5 памяти, второй адрес на своем втором выходе, соединенном с синхровходами регистров 6, 7 и первым входом установки первого счетчика 3 и третий адрес на своем третьем выходе подключенном к входу установки второго счетчика 4. Выходы чтения и записи блока 1 подключены к соответствующим входам блока 5 и стробирующим входам дешифратора 2. Выход первого регистра 6 подключен к первому информационному входу компаратора 8 и информационному входу второго регистра 7, выход которого заведен на информационный вход счетчика

3, выход которого подключен к первому адресному входу блока 5 и к второму информационному входу компаратора 8, выход которого через одновибратор 9 заведен на второй вход записи счетчика 3 и синхровход счетчика 4. выход которого соединен с вторым адресным входом блока 5.

1837298

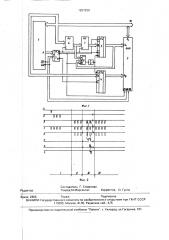

На фиг.2 обозначены: а — в — соответственно первый-третий выходы дешифратора 2; r, д — сигналы записи и чтения процессорного блока 1; е — интервал совпадения входных операндов компаратора 8; ж — выход компаратора 8; э — выход одновибратора 9.

Дополнительно обозначены участки: 1— инициализации счетчиков 3, 4 и регистров 6, 7 перед информационным обменом с памятью; II — начало записи/чтения первой строки фрагмента; ltl — запись/чтение последних двух элементов строки фрагмента;

IV — запись/чтение следующей строки.

Устройство работает следующим образом.

Блок 5 памяти хранит информационный массив размерностью 256х256 элементов.

Он адресуется по горизонтали 8-разрядным счетчиком 3, по вертикали 8-разрядным счетчиком 4, Верхний левый элемент массива адресуется нулевыми значениями счетчиков 3, 4, Передача элементов прямоугольного фрагмента массива производится в порядке слева направо, сверху вниз.

Перед передачей элементов фрагмента процессорный блок 1 производит инициализацию счетчиков 3, 4 и регистров 6, 7. Он последовательно выбирает из стека своей системной памяти их атрибуты и заносит в укаэанные счетчики и регистры, сначала указывая адрес АЗ, затем трижды А2. В результате выбранные процессорным блоком

1 из стека четыре байта атрибутов фрагмента последовательно выводятся на информационную шину 10, сначала байт УлВ, сопровождаемый адресом А3, затем дважды Xns, затем Хя, сопровождаемые адресом

А2. Выдаваемая информация стробируется по выходу записи (фиг.2г, 1), что отрабатывается третьим, а .затем вторым выходами дешифратора 2 (фиг.2а, б, 1).

По окончании процесса инициализации: в регистре 6 хранится координата Хп правого столбца, передаваемого прямоугольного фрагмента; в регистре 7, счетчике

3 — координата Хдв левого верхнего элемента передаваемого фрагмента; в счетчике 4— координата У в левого верхнего элемента передаваемого фрагмента. Процессорный блок 1 переходит к последовательному обмену байтами, укаэанного фрагмента с блоком 5 памяти. выставляя адрес А1, которому соответствует первый выход дешифратора 2.

Первый выход дешифратора 2 активизирует блок 5 памяти по входу доступа EN, по активности сигнала записи или чтения (WR, RD) подключая вход или выход блока 5 к шине 10 (фиг.2в, г, д. II). По окончании чте5

15 ния-записи очередного элемента в блоке 5 памяти счетчик 3 инкрементируется, адресуя следующий элемент фрагмента по строке. Последний элемент строки фрагмента определяется на компараторе 8 (фиг.2е, ж, Ш), импульс с стробируемого выхода которого своим задним фронтом запускает одновибратор 9 (фиг.2з, III), который заносит по второму входу записи в счетчик 3 из регистра 7 координату Х левого столбца фрагмента, и инкрементирует по счетному входу счетчик 4. В результате счетчики 3, 4 адресуют крайний левый элемент следующей строки и процесс перекачки может быть продолжен (фиг.2, IV). По просчету процессорным блоком 1 всех передаваемых элементов фрагмента процесс "перекачки" заканчивается.

Формула изобретения

Устройство для адресации массивов данных, содержащее регистр, дешифратор и два счетчика, причем вход задания режи ма функционирования устройства подключен к информационному входу дешифратора, первый и второй стробирующие входы которого соединены соответственно с входами чтения и записи устройства, первый выход дешифратора подключен к счетному

30 входу первого счетчика и к выходу стробирования обращения к памяти устройства, второй и третий выходы дешифратора подключены соответственно к первому входу записи первого счетчика и к входу записи

35 второго счетчика, выход которого подключен к выходу адреса столбца массива устрдйства, выход первого счетчика подключен к выходу адреса строки массива устройства, вход параметров адресуемого массива уст40 ройства подключен к информационному входу второго счетчика, о т л и ч а ю щ е ес я тем, что, с целью повышения быстродействия, в него введены регистр, схема сравнения и одновибратор, причем вход

45 параметров адресуемого массива устройства подключен к информационному входу первого регистра, выход которого подключен к информационному входу второго регистра и к первому информационному входу

50 схемы сравнения, выход которой через одновибратор подключен к второму входу записи первого счетчикя и к счетному входу второго счетчика, выход второго регистра подключен к информационному входу пер55 вого счетчика, выход которого подключен к второму информационному входу схемы сравнения, стробирующий вход которой подключен к первому выходу дешифратора, второй выход которого подключен к синхровходам первого и второго регистров.

1837298

Фиг. 2

Составитель Г. Смирнова

Техред М.Моргентал Корректор О. Густи

Редактор

Тираж Подписное осударственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб.. 4/5

Производственно-издательский комбинат "Патент", r, Ужгород, ул.Гагарина, 101